False Paths

这部分描述的约束命令是create_clock 和set_false_path.

我们并不需要对每一条路径都进行时序分析。非关键的同步路径可以从时序分析中移除。当我们声明非关键路径时,Quartus II的Fitter(布局布线工具)可以关注于关键路径的优化,减少编译时间。 Figure 1–16展示了一个简单的寄存器-寄存器的设计,在这个例子中,减去了对reg1到reg2的路径时序分析。

Palse Path 可以应用于时钟路径(clock-to-clock)或是独立的寄存器(individual register)。将Palse Path应用于时钟路径可以在时序分析中,排除目的时钟之间的所有路径。Example 1–19 展示了对false path的约束应用。

Example 1–19. False Path Clock-to-Clock

create_clock -period 10 [ get_ports clkA]

create_clock -period 5 [ get_ports clkB]

set_false_path -from [ get_clocks {clkA}] - to [ get_clocks {clkB }]

在Example 1–19中,所有源时钟是clka,目的时钟是clkb的寄存器之间的路径都被时序分析排除在外。同时,这样不会排除对源时钟是clkb,目的时钟是clka的路径时序分析。

对于Example 1–19来说,set_false_path命令除去了clka到clkb路径的时序分析。但是并没有出去clkb到clka的,为了出去clkb到clka的路径,必须再添加一个set_false_path命令。(for example,

set_false_path -from clkB -to clkA)。另外,我们也以通过

set_clock_groups这一个命令来同时除去这两条路径。

■ For more information about the set_clock_groups command, refer to Set Clock Groups Dialog Box (set_clock_groups) in Quartus II Help.

对单独寄存器使用false path命令,仅仅除去指定的路径。Example 1–20展示了这个约束。

Example 1–20. False Path Register-to-Register

create_clock -period 10 [ get_ports clkA]

create_clock -period 5 [ get_ports clkB]

set_false_path -from [ get_pins {reg1|q }] - to [get_pins { reg2| d}]

P25

Miscellaneous

This section contains the following topics:

■ “JTAG Signals” JTAG信号

■ “Input and Output Delays with Multiple Clocks” on page 1–22 多时钟下的输入输出延时

■ “Clock Enable Multicycle” on page 1–26 使能多时钟周期的时钟

JTAG Signals

这里描述的约束命令是create_clock, set_input_delay, set_output_delay

许多系统调试工具使用JTAG接口。当调试时,JTAG的TCK,TMS,TDI,和TDO信号将成为设计中的一部分。因此,Timequest Analyser标记这些信号为unconstrained,当unconstrained path report生成的时候。

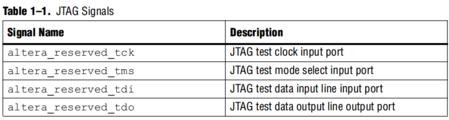

Table 1–1 shows the JTAG signals that might appear as unconstrained.

P26

P26你可以通过SDC命令对JTAG信号进行时序约束。

Example 1–21. JTAG Signal Constraints

#JTAG Signal Constraints

#constrain the TCK port

create_clock \

- name tck \

- period "10MHz" \

[ get_ports altera_reserved_tck]

#cut all paths to and from tck

set_clock_groups -exclusive - group [ get_clocks tck]

#constrain the TDI port

set_input_delay \

- clock tck \

20 \

[ get_ports altera_reserved_tdi]

#constrain the TMS port

set_input_delay \

- clock tck \

20 \

[ get_ports altera_reserved_tms]

#constrain the TDO port

set_output_delay \

- clock tck \

20 \

[ get_ports altera_reserved_tdo]

/2

/2

文章评论(0条评论)

登录后参与讨论