对于老手来说 fifo再简单不过了,可是对于新手来说,学习fifo总会遇到些问题。最近在做fifo仿真的时候,就遇到了几个问题,上网找了好多资料,但是针对性的回答很少,最后还是看xilink官方的文档找到了答案,这里做个记录,以便新手在这个地方不浪费过多时间。

在创建fifo的时候 有common clk 和independent clk 之说,这里以 independent clk 做为例子,创建的时候我觉得需要注意的是你在一直点next的时候,到异步复位那块需要多加小心。因为在生成的时候默认的是高电平的复位,而大部分板子是低电平的 ,所以这个时候你需要把1改为0。否则你会发现你的full和empty同时为高,这个矛盾的情况出现。刚出现这个情况的时候,我也是迷糊了好久。

其次我们来看看写时序的波形图,这里的波形图是我已经改过的,在刚开始的时候

我在系统刚开始复位结束的时候就向fifo写数据,发现1,2,3 这三个数据怎么写不进去(我的计数器是一复位结束就开始计数),后来找到原因:xilink 的fifo 在复位结束的三个时钟周期内是禁止任何写操作。

再来看看读时序,读时序分为两种模式,一种是标准读操作,还有一种是fwft读操作,具体这两种有什么区别,官方手册写的很详细也附带时序图,这里我就不赘述了。

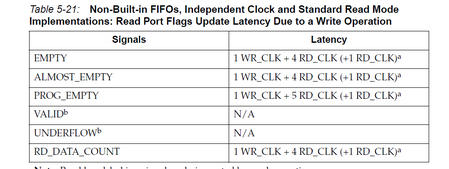

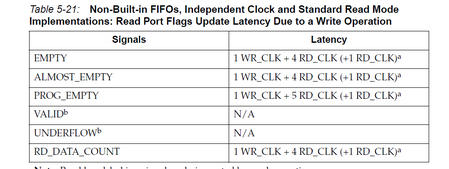

我想说的是请大家注意这个empty的信号,这个empty 并不是写进去一个数就立即变为低电平,而是等待6个时钟周期。难道官方的fifo有问题? 其实不是,这里是跨时钟传输的时候一种自我的保护模式,如果你选择的是common clk 就不会有这个latency。这里传个官方手册的图,详细的解释具体到你fifo延迟多少可以去官方手册上查阅。

最后附带的说下 我使用的是ise13.1 fifo 版本为8.1 查询的手册为ug175

/5

/5

用户377235 2015-10-26 12:20

非常感谢