module clk_odd_div(clk_in,rst_n,clk_out);

parameter DIV_NUM = 3,CNT_BIT = 4; //可设置奇数分频数

input clk_in,rst_n;

output clk_out;

reg [CNT_BIT-1:0] cnt1,cnt2;

reg clk_p,clk_n;

always @(posedge clk_in) begin //上升沿触发产生奇数分频时钟,占空比非50%

if(!rst_n) begin

cnt1 <= 0;

clk_p <= 0;

end

else

begin

if(cnt1 == 0) //时钟信号翻转时刻

begin

clk_p <=~clk_p;

cnt1 <= cnt1 + 1;

end

else if(cnt1 ==(DIV_NUM-1)/2) //时钟信号翻转时刻

begin

clk_p <=~ clk_p;

cnt1 <= cnt1 + 1;

end

else if(cnt1 ==DIV_NUM-1) //时钟信号保持时刻

begin

cnt1 <= 0;

clk_p <= clk_p;

end

else

begin

cnt1 <= cnt1 + 1;

clk_p <= clk_p;

end

end

end

always @(negedge clk_in) begin//下升沿触发产生奇数分频时钟,占空比非50%

if(!rst_n) begin

cnt2 <= 0;

clk_n <= 0;

end

else

begin

if(cnt2 == 0)

begin

clk_n <=~clk_n;

cnt2 <= cnt2 + 1;

end

else if(cnt2 ==(DIV_NUM-1)/2)

begin

clk_n <=~ clk_n;

cnt2 <= cnt2 + 1;

end

else if(cnt2 ==DIV_NUM-1)

begin

cnt2 <= 0;

clk_n <= clk_n;

end

else

begin

cnt2 <= cnt2 + 1;

clk_n <= clk_n;

end

end

end

assign clk_out = clk_p|clk_n;//两个错位时钟信号“或”得到占空比50%的时钟信号

endmodule

在testbench中,例化模块可以改变分频参数,实现任意奇数分频。

module clk_div_tb;

reg clk,rst_n;

wire clk_out;

initial

begin

clk = 1;

rst_n = 1;

#2 rst_n = 0;

#2 rst_n = 1;

end

always #1 clk = ~clk;

defparam clk_even_div_m1.DIV_NUM = 7;

defparam clk_even_div_m1.CNT_BIT = 4;

clk_odd_div clk_even_div_m1(clk,rst_n,clk_out);

endmodule

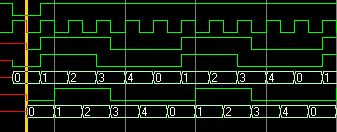

DIV_NUM = 5时的波形如下图:

第三行的波形为输出占空比50%的5分频波形。

第四行和第六行为占空比非50%的5分频波形。

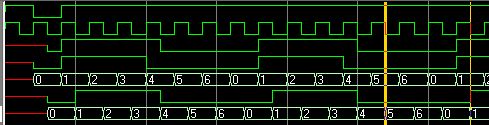

DIV_NUM = 7时的波形如下图

/5

/5

文章评论(0条评论)

登录后参与讨论