Altera FPGA优化技术-功耗的优化

KevinWan

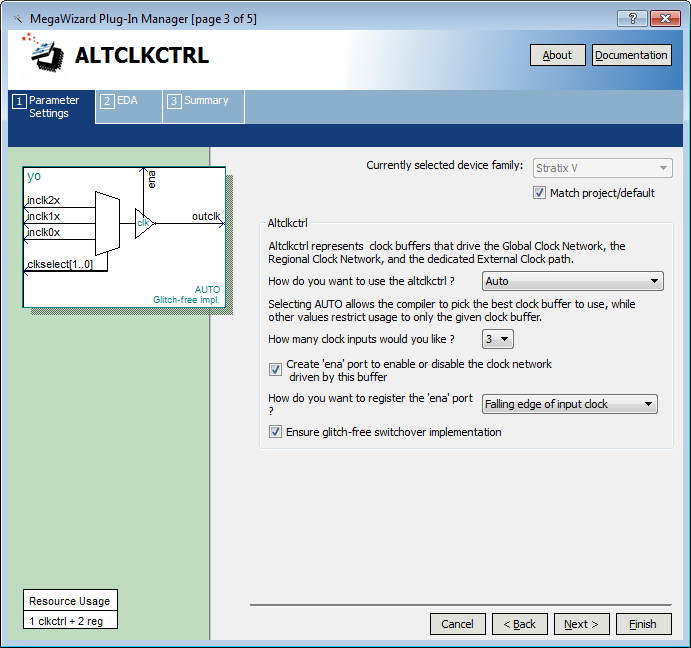

使用ALTCLKCTRL模块,管理时钟输出,有效的控制功耗。

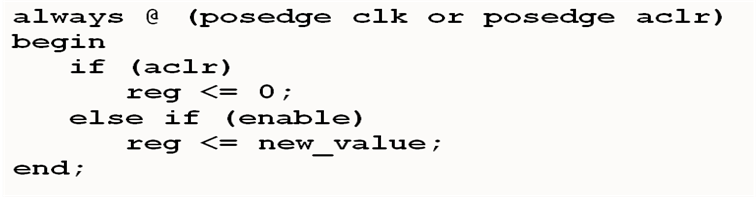

代码中设置使能信号,控制reg的翻转。

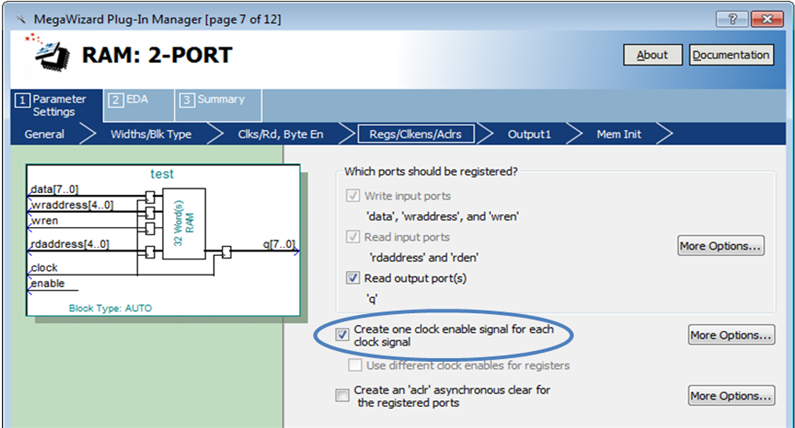

Ram的功耗主要消耗在动态时钟上,减小动态的时钟的使用是有效的减小Memory的功耗。

地址或者数据的翻转对memory功耗影响不大。

使用memory的clock enable control选项。

降低输出电流,降低输出翻转率。

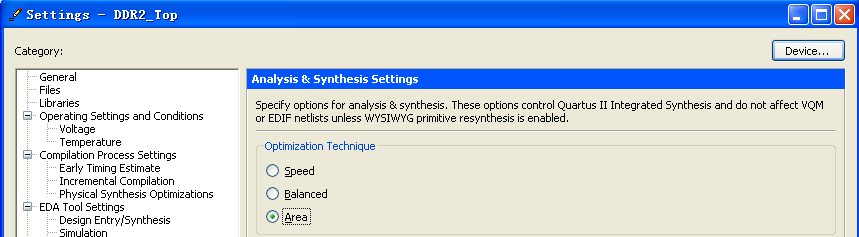

减小逻辑资源就等效于更少的逻辑翻转,可以减小功耗。

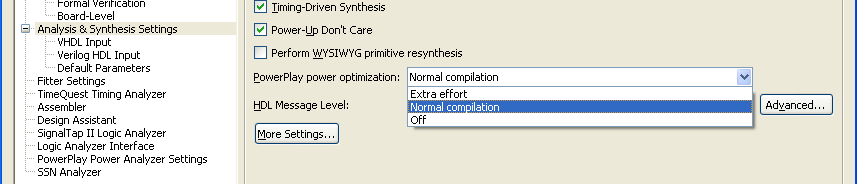

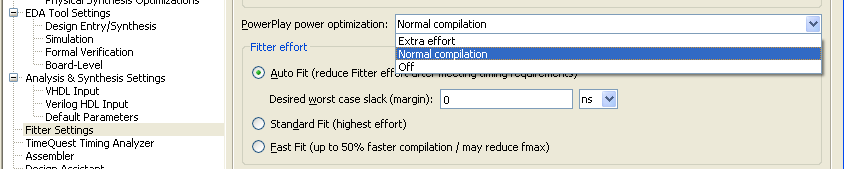

使用电源优化顾问来优化。

/5

/5

文章评论(0条评论)

登录后参与讨论