Altera FPGA优化技术-时序的优化

KevinWan

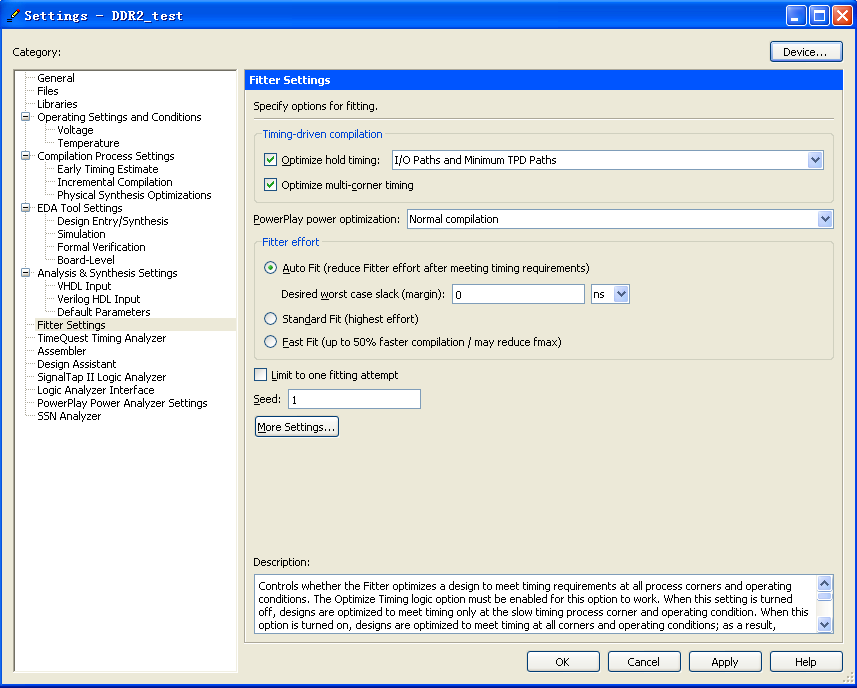

在Fitter Settings/Timing-drive complation中优化保持时间,可以选择All path和I/O Paths and Minimum TPD Paths.

Altera推荐采用时序驱动编译,工具会在多个关键路径中做折中,使得系统的性能最优。

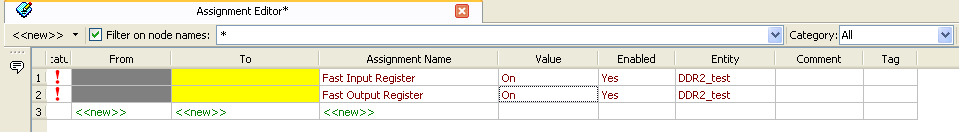

IOE块一般都有自己的寄存器,他是最靠近IO的,所以使用它可以获得最小的Tco,我们可以再Assignment Editor中选择快速输入寄存器(Fast Input Register)和快速输出寄存器( Fast Output Register)。

对于多时钟系统或者时钟路径较长,无法满足Tsu或者Th的时候,可以采用PLL对时钟进行移相,来满足Tsu和Th的要求。

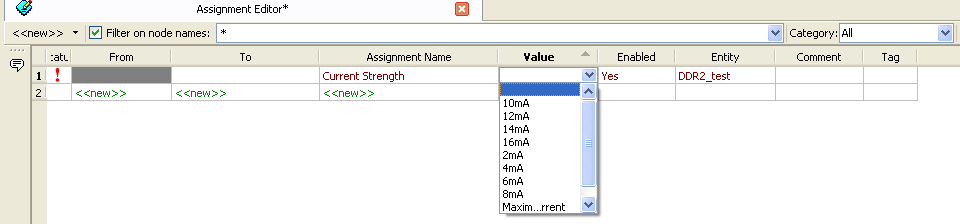

管脚的驱动电流越大,意味着输出驱动器的输出阻抗越小,输出管脚对负载电容的充电时间越短,信号输出延时越小,但是,电流越大,对系统带来较大的噪声。

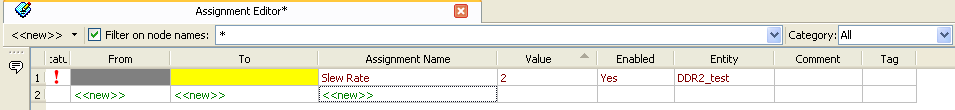

I/O翻转的斜率越大,速度越快,但是上冲和下冲也就越大。

/5

/5

文章评论(0条评论)

登录后参与讨论