Altera FPGA优化技术-资源的优化

KevinWan

模块时分复用解决面积的问题,达到节省资源的目的。

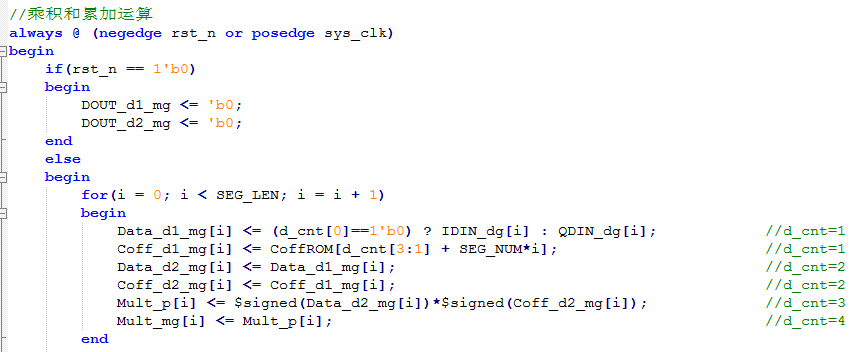

比如分时复用乘法器,在一个系统的主时钟下,分很多时隙,每个时隙条用同一个乘法器,这样就可以复用乘法器了。

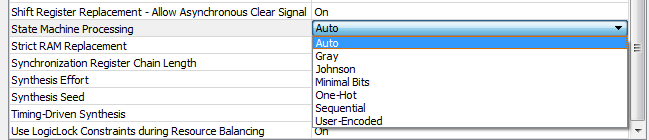

不同的编码方式对寄存器和状态机的性能都有影响,改变状态机的编码方式也是代码优化的一个有效的方式。

相同的功能,不同的代码会利用不同的资源,所以考虑不同的实现方式也是资源优化的一种方式。

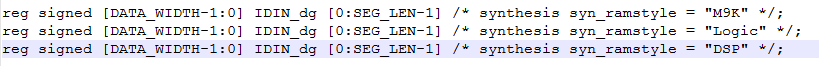

比如使用专用的资源实现DSP、RAM的模块。

时钟过约束会造成资源的大量使用,有时会造成局部设计的性能的下降,影响整个的Fmax。

这样会让综合工具尽量减小逻辑复制。

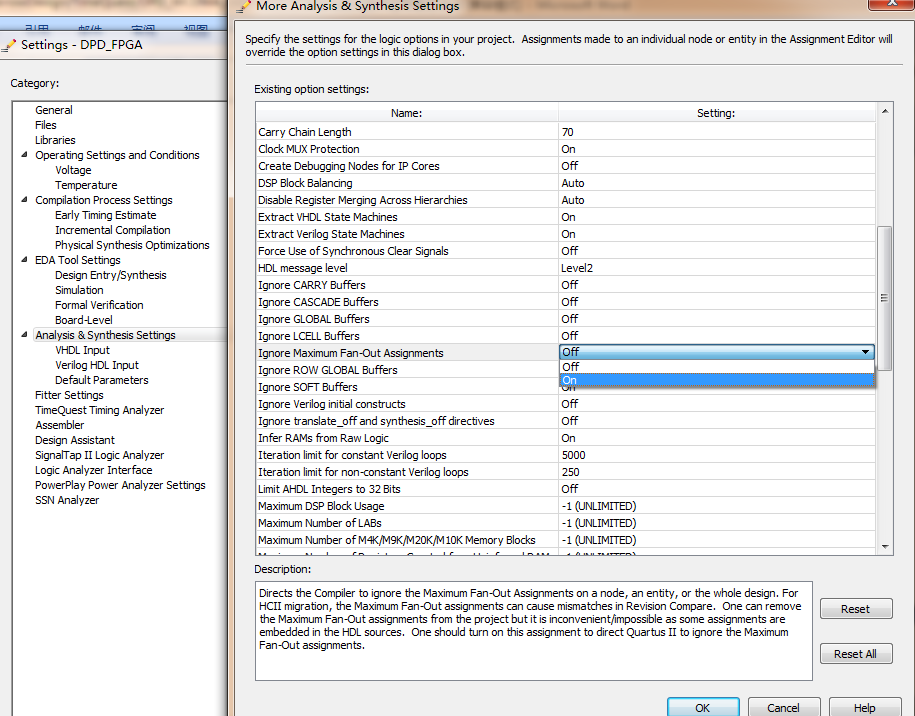

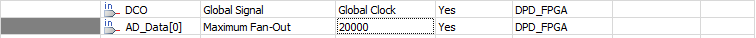

忽略最大Fan out的限制

也可以在Assignment Editor里设置最大的Fan out的具体的值,可以设置的很大。

可以采用DSP等模块的复用

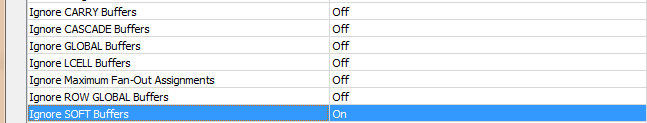

忽略相关的LCELL以及相关的寄存器和Buffer

较大的状态机采用二进制顺序编码或者格雷码,可以获得最优的面积优化。

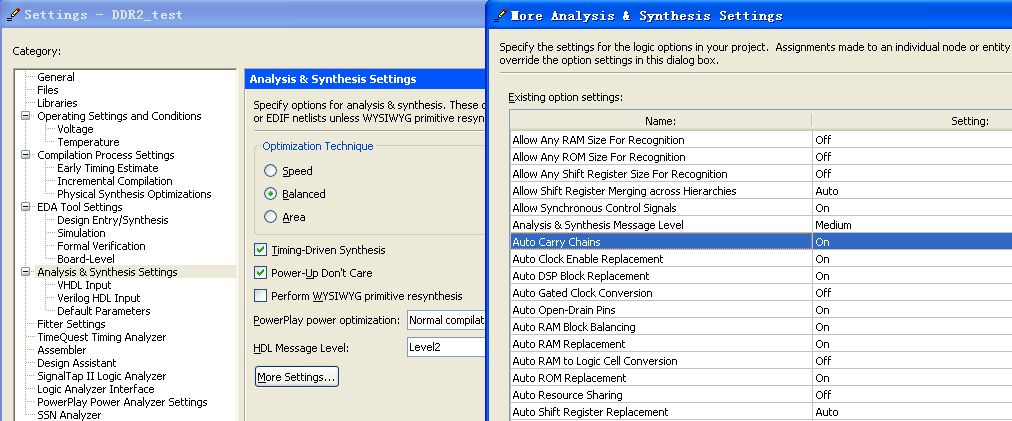

在Analisis&Synthesis Settings的More Settings里:

使得模块边界充分优化。

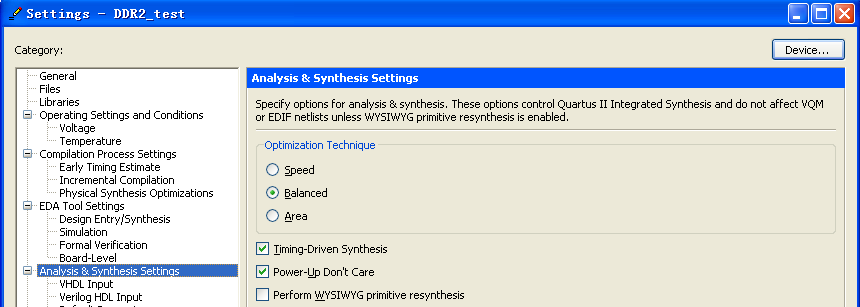

n 采用QuartusII中的Optimization Technique中的Area面积优化选项,达到目的优化。

n 采用QuartusII中的资源分配选项:

Ø Auto DSP Block Replacement : 自动决定是否用DSP模块资源替代设计中的同等功能模块

Ø Auto RAM Replacement : 自动决定是否用RAM模块资源替代设计中的同等功能模块

Ø Auto ROM Replacement : 自动决定是否用ROM模块资源替代设计中的同等功能模块

Ø Auto RAM Block Balancing : 自动决定采用哪一种RAM块类型

Ø Auto Shift Register Replacement : 自动决定是否替代逻辑中的移位寄存器

Ø DSP Black Balancing : DSP功能实现的资源分配方式

n 采用QuartusII中的资源优化选项

Ø Auto Resource Sharing :资源共享,节省面积

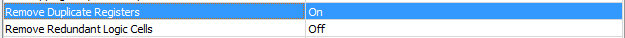

Ø Remove Duplicate Logic :去除复制的逻辑

Ø Remove Duplicate Registers :去除复制的寄存器

Ø Remove Redundant Logic Cells :去除多余的逻辑单元

网表主要是提供给第三方去作为设计的输入,QuartusII工具可以对输入的网表做优化。

在第三方的综合工具输入的网表中,逻辑功能一般以Altera的基本原语(Primitives)为单位来描述,这些原语包括Altera的基本单元,这些原语成为“所见即所得原语”(WYSIWYG Primitive),也称为“ATOMS”。

Altera把打包和解包的过程成为“WYSIWYG原语再综合”。

在QuartusII工具的布局布线时,工具可以把寄存器和设计中的其他部分进行打包封装,这样可以节省逻辑单元的使用,达到优化面积的效果。

例如:使用DSP或者RAM块的时候,他们本身输入输出都是有寄存器的,如果外面再加上寄存器作为流水线的话,可以设置寄存器打包,把外面的寄存器和DSP块作为一个整体进行打包操作。

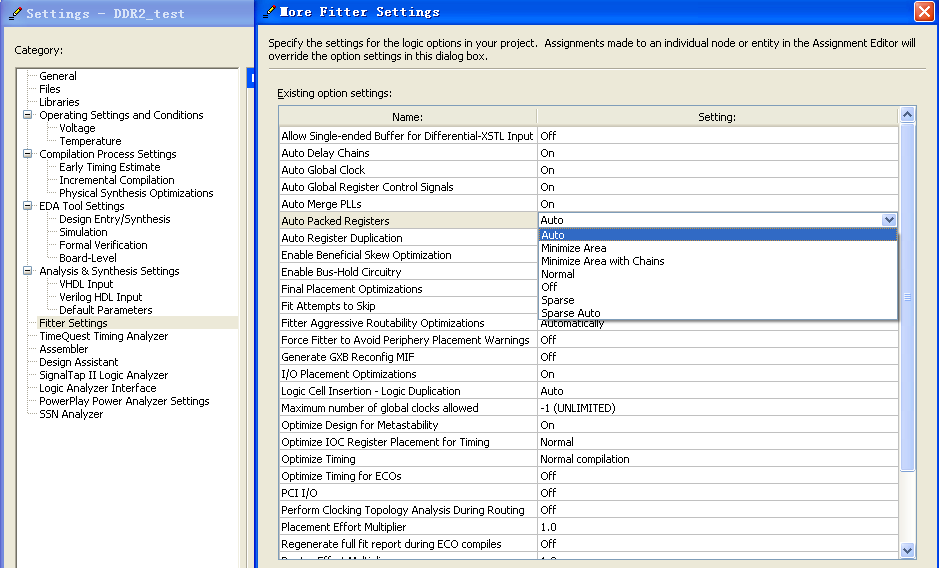

在Fitter Setting/More Setting/Auto Packed Registers选择不同的类型:

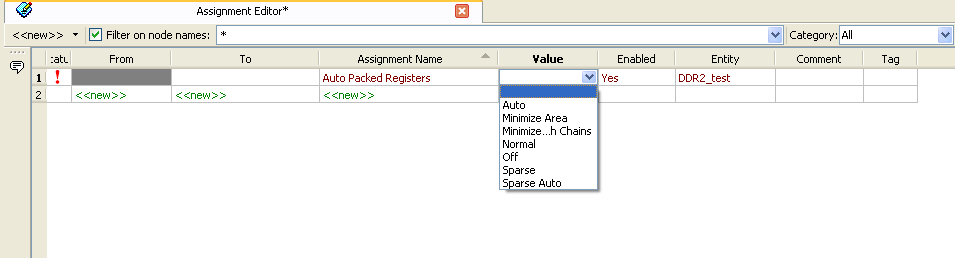

在Assignment Editor中可以进行局部的设置:

/5

/5

文章评论(0条评论)

登录后参与讨论