Altera FPGA优化技术-Fmax的优化

KevinWan

在设计中,把较大的组合逻辑分成小块,中间加上寄存器做流水,这样可以显著提高系统的Fmax。

这条类似与增加流水线,使得较大的组合逻辑分一部分到较小的逻辑中,这样可以达到平衡。

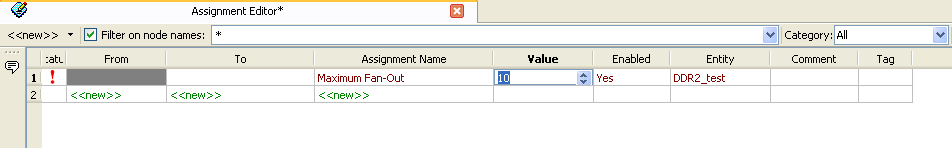

复制节点的好处是提高设计的性能和可布线性,但是会造成资源的增加

对于模块的设计,Altera推荐输入的信号用寄存器打一拍,输出的信号也用寄存器打一拍再输出。

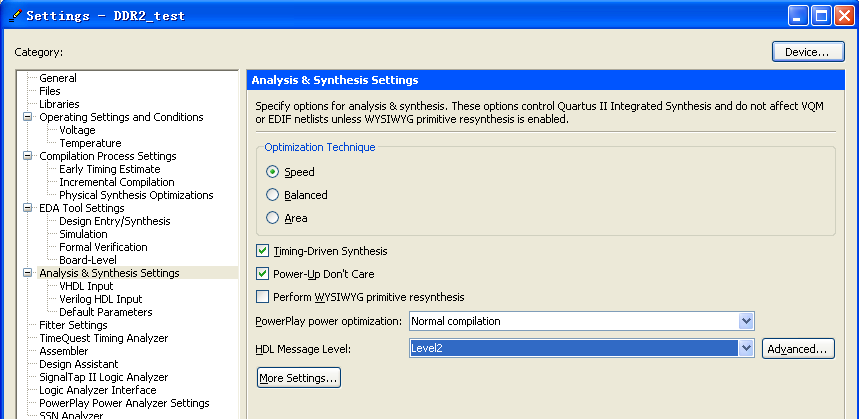

在Analysis & Synthesis Settings中的Optimization Technique选择Speed,工具会在综合的时候对设计进行速度优化。

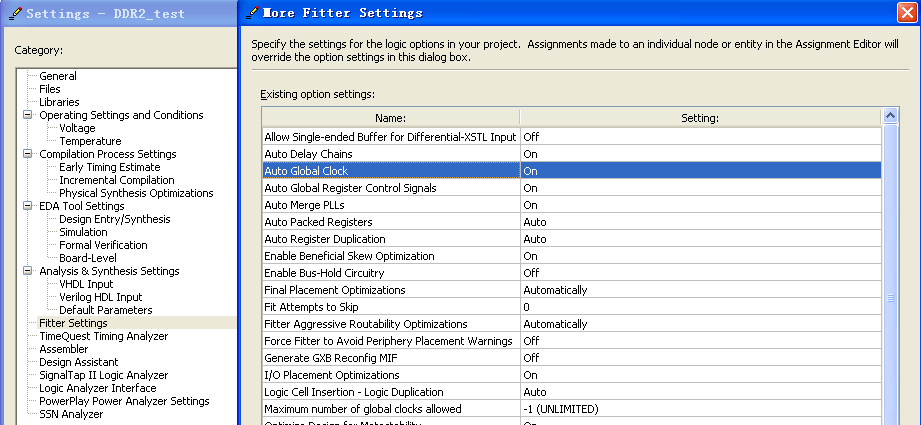

在Fitter中的More Setting中的Auto Global Clock选项打开的话,工具会在布局布线的时候自动的把一些高扇出的信号布在全局时钟网络上;Auto Global Register Control Singals打开的话,会把一些高扇出的寄存器控制信号布在全局网络上,包括清零、置位和时钟使能等。

扇出控制可以控制信号的延时,扇出越小,走线延时就越小,可以再Assignment Editor中设置扇出。

用户可以再QuartusII中设置,使得工具打平设计中的层次结构,使得模块的边界充分优化。

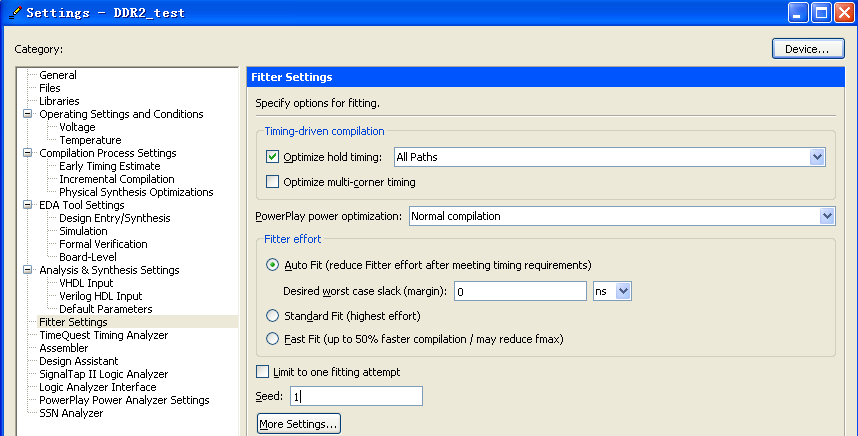

采用时序驱动编译。

采用区域的Logic Lock的方法去锁定相关的或者是关键的资源部分,达到优化走线,提高系统的Fmax。

/4

/4

文章评论(0条评论)

登录后参与讨论