Altera ALTMEPHY DDR2详细介绍(一)

KevinWan

在Cyclone IV 器件中用于外部存储器接口的数据管脚中,用于写数据的管脚称为D,

读数据的管脚称为Q,共享读写数据的管脚称为DQ。读数据选通或者读时钟称为DQS

管脚。Cyclone IV 器件支持双向数据选通以及单向读取时钟。根据外部存储器标准,

DQ和DQS均为双向信号(在DDR2和DDR SDRAM中)

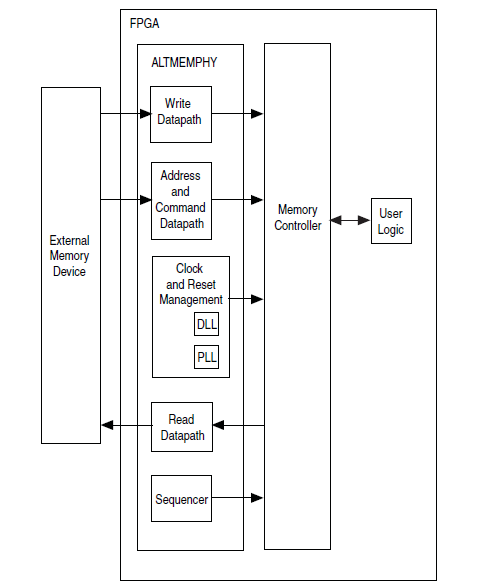

ALTMEMPHY 是一个自校准的宏功能,这个模块得到了增强使其简化了不同存储器接口中读数据路径的实现。ALTMEMPHY 的自校准功能在工艺、电压和温度(PVT) 变化范围内对时钟相位及频率进行优化, 从而实现了易于使用的特性。通过使用ALTMEMPHY 宏功能,可以节省 Cyclone IV 器件中的全局时钟资源( 因为DQS 被忽略来实现读捕捉)。

重同步的问题不会出现,因为不会发生从存储器域时钟(DQS) 到系统域的数据传输(

该数据传输用于捕捉数据DQ)。

一些DDR2 SDRAM 和DDR SDRAM 器件支持错误纠正编码(ECC) 功能, 它一种在数据传输中检测错误并自动纠正错误的方法。在72-bit DDR2 或DDR SDRAM 中有8 个ECC 管脚和64 个数据管脚。将DDR2 和DDR SDRAM ECC 管脚连接到Cyclone IV 器件中单独的DQS 或者DQ 组。存储控制器需要额外的逻辑对ECC 数据进行编码和解码。

地址信号和控制/ 命令信号通常以同一数据速率发送。您可以使用Cyclone IV 器件

I/O 块上的任意用户I/O 管脚来生成存储器件的地址和控制/ 命令信号。

在DDR2 和DDR SDRAM 存储器接口中,存储器时钟信号(CK 和CK#) 用于捕捉地址信号和控制/ 命令信号。同样,QDR II SRAM 器件使用写时钟(K 和K#) 来捕捉地址和命令

信号。生成的CK/CK# 和K/K# 信号通过使用Cyclone IV 器件中的 DDIO 寄存器来对写

数据选通进行模仿(resemble)。

Cyclone IV 器件在纵向及横向I/O 块中支持校准后的片上系列终端(RS OCT)。如要使

用校准后的OCT, 则必须将RUP 和RDN 管脚用于每一个 RS OCT 控制模块( 在器件的每侧各一个)。 您可以使用任意一个OCT 校准模块对采用同样的VCCIO 的对应侧的某种终端进行较准。

当与外部存储器连接时,PLL 用于生成存储器系统时钟、写时钟、捕捉时钟以及逻辑内核时钟。系统时钟生成DQS 写信号、命令及地址。写时钟从系统时钟偏移-90°,并在

写操作期间生成DQ 信号。您可以使用PLL 重配置功能来校准读捕捉相移,从而平衡建

立和保持裕量

PLL 在ALTMEMPHY 宏功能中被例化。当例化ALTMEMPHY 宏功能来连接外部存储器时,将使用PLL 的所有输出。PLL 重配置在ALTMEMPHY 宏功能中使用,以校准并跟踪读捕捉相位,从而保持最佳裕量。

ALTMEMPHY功能框图:

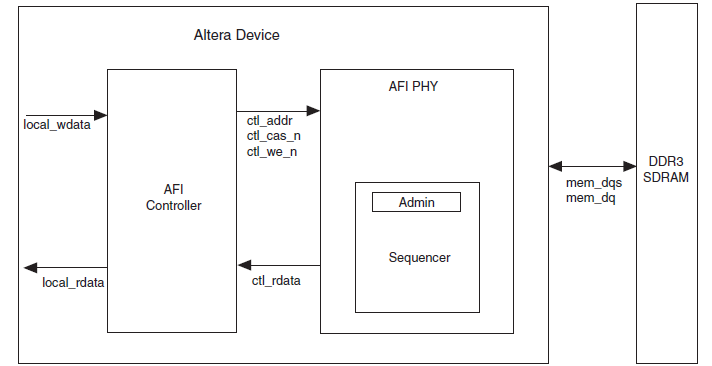

AFI框图:

/3

/3

文章评论(0条评论)

登录后参与讨论