高速接口中的PRBS模块的设计

KevinWan

在高速设计中为了测试高速串行通道传输的误码率,通常通过发送PRBS码来进行测试。

原理:用生成函数产生一段随机码流,然后按周期循环。

PRBS码的周期长度与其阶数有关,常用的阶数有7、9、11、15、20、23、31。

对于n阶PRBS码,每个周期的序列长度为2^n-1。

在每个周期内,“0”和“1”是随机分布的,并且“0”和“1”的个数相等。

连续个“1”的最大数目为n,连续个“0”的最大数目为n-1(反转后就是n-1个连“1”和n个连“0”)。

在对高速信号链路进行误码测试时,基本上都是利用PRBS码流来模拟真实的线网码流环境,因为在线网中,所有的数据都是随机出现的,没有任何规律可言,而PRBS码流在一定程度上具有这种“随机数据”特性,二进制“0”和“1”随机出现,其频谱特征与白噪声非常接近。PRBS码流的阶数越高,其包含的码型就越丰富,就越接近真实的线网环境,测试的结果就越准确。

一个PRBS序列可以串/并转换成多路(2、4、8、16…路),每路输出的速率降低,但仍然保持原序列的一切特征;反之,同一时钟源低速率多路(2、4、8、16…路)同一n数的PRBS可以经并/串转换成高速率的n阶PRBS。

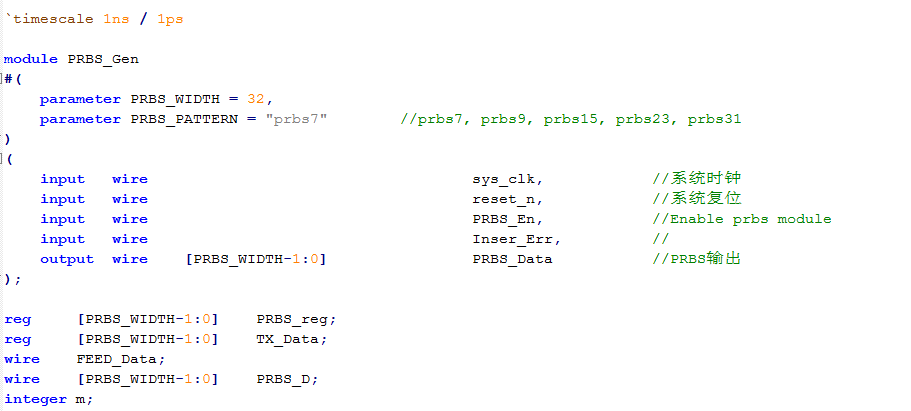

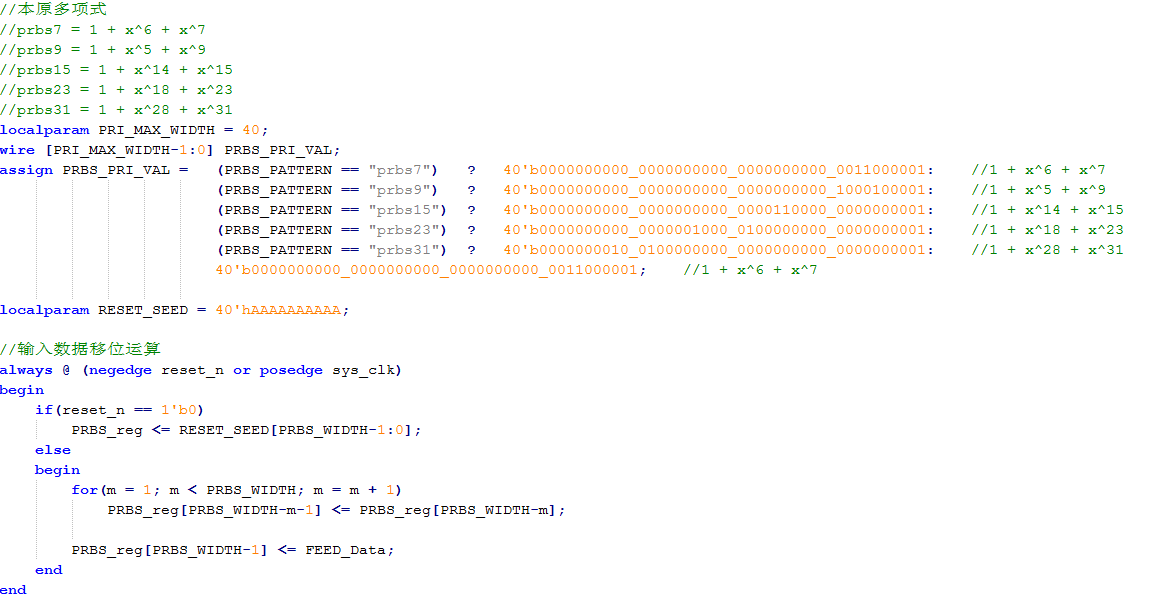

本文采用Verilog来设计PRBS模块,可以通过外部的参数配置输出prbs7, prbs9, prbs15, prbs23, prbs31

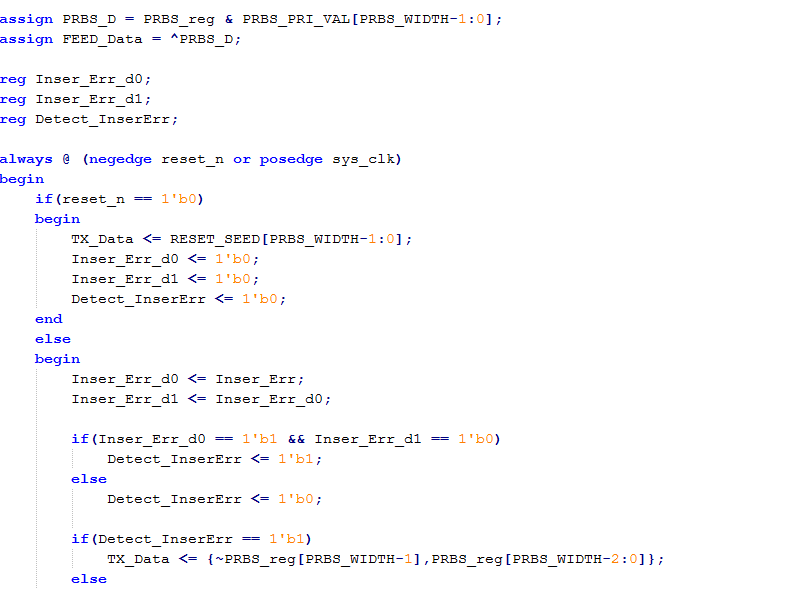

TX_Data <= PRBS_reg[PRBS_WIDTH-1:0];

end

end

assign PRBS_Data = TX_Data;

endmodule

/4

/4

文章评论(0条评论)

登录后参与讨论