verilog assign语句的用法未解之谜<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

下面是功能相同但写法不同的两段代码:

(1)module assign_test (

clk,

lhold,

lholda

);

input clk;

input lhold;

output lholda;

reg lholda;

always @(posedge clk)

if (lhold)

lholda<=lhold;

else

lholda<=0;

endmodule

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

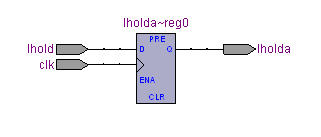

未加入assign的综合结果

(2)module assign_test (

clk,

lhold,

lholda

);

input clk;

input lhold;

output lholda;

reg lholda_r;

always @(posedge clk)

if (lhold)

lholda_r<=lhold;

else

lholda_r<=0;

assign lholda=lholda_r;

endmodule

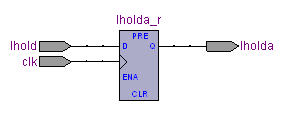

加入assign风格的综合结果

结论:两相比较,几乎没有差别。可又为什么经常采用(2)的风格来编写类似代码?

一些verilog书上说assign用在连续型赋值的场合,摘自某书籍——

“连续赋值语句用来驱动线型变量,这一线型变量必须已经事先定义过。只要输入端操作数的值发生变化,该语句就重新计算并刷新赋值结果。我们可以使用连续赋值语句来描述组合逻辑而不需要用门电路和互连线。在前面一节中已经对连续赋值做了介绍,关键词assign用来区分连续赋值语句和过程赋值语句,下面一条语句将线型变量int1和int2相与,并用这一结果去驱动out信号:

wire out ;

assign out= int1 & int2 ;”

现在我不解的是,为什么在使用寄存器赋值的场合(过程赋值)也用到了

“assign 端口=寄存器 ;”

望飘过的神仙、大牛、小牛们帮小弟解解惑,不胜感激了!

/4

/4

文章评论(0条评论)

登录后参与讨论