4通道数字下变频-> CIC抽取滤波器-> FIR滤波器-> CIC插值滤波器->数字上变频<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

1.数字下变频

NCO采用ALTERA的IP核,NCO的设置如下:

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

图 NCO IPcore设置

NCO IPcore在ModelSim中仿真如下:

图 在ModelSim中进行NCO IPcore仿真

2.数字下变频+CIC 64倍抽取模块

通道1 NCO中频设为28.8MHz,通道2 NCO中频设为26.88MHz,NCO输出位宽16bit,通道信号输入ch_in位宽16bit,I&Q信号按如下公式产生:

I = ch_in * cos(wt)

Q = ch_in * sin(wt)

乘法器位宽为32bit,I&Q信号为16bit,截取乘法器输出的[30:15]。

为仿真方便,输入设为一常量:32767。

主时钟频率为122.88MHz,CIC滤波抽取后数据速率为1.92MHz,抽取倍数为64,级数4,每级延迟1。输入数据位宽16bit,内部位宽为[40 40 40 40 40 40 40 40],输出位宽为16bit,截取[39:24]。CIC抽取在QUARUTS中的仿真图如下:

图 CIC抽取滤波器QUARTUS仿真图

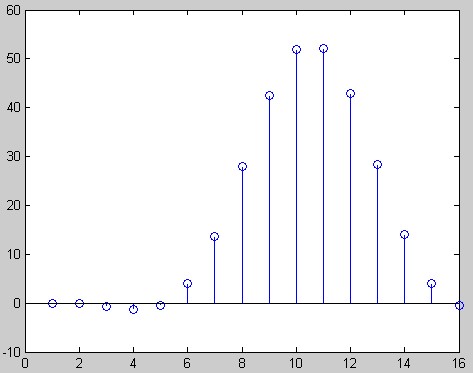

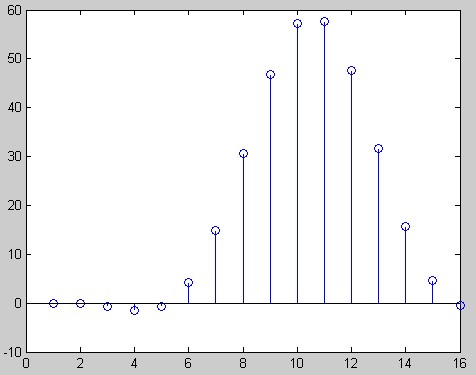

CIC抽取滤波器在MATLAB中仿真如下:

图 通道1 CIC抽取滤波器MATLAB仿真图

图 通道2 CIC抽取滤波器MATLAB仿真图

结论:经数据对比,结果正确。

3.FIR滤波器

主时钟频率122.88MHz,每通道采样频率为1.92MHz,滤波器阶数为16阶,如果采用串行累加结构实现FIR滤波器,则每通道完成一次滤波需要16个时钟,122.88/1.92=64,因此可以4通道分时复用1乘法器。FIR滤波器一般先在MATLAB FDATool中进行设计,然后从MATLAB中导出FIR滤波器的系数,再在FPGA中实现。

在MATLAB FDATool中设置FIR滤波器参数如下图所示:

图 在MATLAB中设置FIR滤波器的参数

4通道FIR滤波器在FPGA中的仿真如下:

图 4通道FIR滤波器 FPGA仿真

4通道FIR滤波器在MATLAB中的仿真如下:

图 通道1 I&Q信号 FIR滤波后输出MATLAB仿真图

图 通道2 I&Q信号 FIR滤波后输出MATLAB仿真图

4.CIC插值滤波器

CIC插值前数据速率为1.92MHz,插值后速率为122.88MHz,插值倍数为64,级数4,每级延迟1。输入数据位宽16,内部位宽[17 18 19 19 19 24 29 34],最后输出位宽为16,截取高16位[33:18]。

CIC插值滤波器在QUARTUS中的仿真如下:

图 CIC插值滤波器QUARTUS仿真图

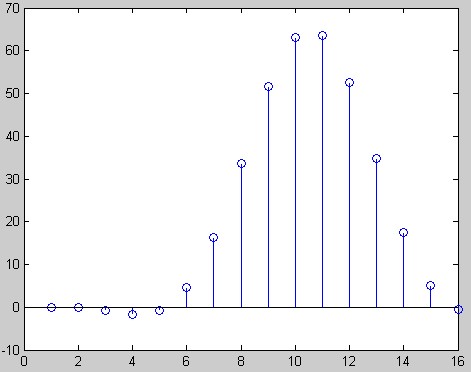

产生相同的输入数据,在MATLAB中的仿真如下(2路I&Q信号输出都相同):

图 CIC插值滤波器MATLAB计算结果

数据对比:

QUARTUS MATLAB

0 0

0 0

0 0

0 0

-1 -1

-4 -4

-10 -10

-20 -20

-35 -35

…… ……

结论:结果正确。

5.数字上变频

每路I&Q信号,上变频都要做复数乘法,公式为:

Real = I*cos(wt) + Q*sin(wt)

Imag = Q*cos(wt) - I*sin(wt)

cos(wt)和sin(wt)共用数字下变频时的NCO,I、Q信号输入为16bit,正余弦信号16bit,则每进行一次复数乘法需要4个乘法器。乘法器输出为32bit,进行加减法后位宽取32bit,输出位宽取16bit,截取[30:15]。

图 数字上变频QUARTUS仿真图

/5

/5

文章评论(0条评论)

登录后参与讨论