在使用我们的最新模数转换器 (ADC) 和数模转换器 (DAC) 设计系统时,我已知道了很多有关 JESD204B 接口标准的信息,这些器件使用该协议与 FPGA 通信。此外,我还在 E2E 上的该栏目下阅读了各种技术文章及其它博客文章,明白了为什么 JESD204B 是 LVDS 和 CMOS 接口的后续产品。

有一个没有深入讨论的主题就是解决 ADC 至 FPGA 和 FPGA 至 DAC 链路问题的协议部分,这两种链路本来就是相同的 TX 至 RX 系统。作为一名应用工程师,我所需要的就是了解其中的细微差别,这样才能充分利用 JESD204B 通过现有 LVDS 和 CMOS 接口提供的优势。

有了 JESD204B,您无需再:

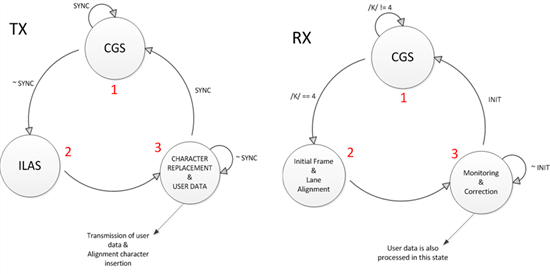

我们来考虑一种由 ADC 等数字源向 FPGA 发送数字数据的简单情况。在正确发送或接收数据之前,有几件事必须要做,如图 1 所示以及下文所说明的那样。

图 1. JESD204B 协议状态图

1. 代码组同步 (CGS) — 不需要接口时钟,因此 RX 必须将其数位及字边界与 TX 串行输出对齐。RX 可向 TX 发送 SYNC 请求,让其通过所有信道发送一个已知的重复比特序列,本例中每字符每 K 是 K28.5。确切的字符比特序列可在标准中找到。RX 将移动每个信道上的比特数据,直到找到 4 个连续的 K28.5 字符为止。这时,它不仅将知道比特及字边界,而且已经实现了 CGS。随后,它会取消对 SYNC 的断言,而 TX 和 RX 则都会进入下一个状态:初始信道对齐序列 (ILAS)。

2. ILAS — JESD204B 协议的一个良好特性可实现通过 RX 模块中的一些 FIFO/缓冲器吸收信道偏移。在实现 CGS 后,TX 可在每个信道上发送已知的字符帧集合,称为信道对齐序列(以每字符每 R K28.0 开始,以每字符每 A K28.3 结束)。收到对齐序列后,RX 会对数据进行 FIFO 缓冲,直到所有信道都收到完整的对齐序列。由于已经知道了整个序列,因此信道随后可重新对齐,这样每个信道上的任何信道偏移都可通过 FIFO 存储器吸收,而且,信道随后还可在相同的时间点、在 RX 模块内释放该数据。这可缓解为串行解串器信道提供匹配布局的需求,因为信道偏移可通过 FIFO 存储器吸收。

3. 用户数据 — 在代码组同步及信道对齐后,就可正确接收用户数据。如果在该最后状态时用户数据无效,则需要重新启动本过程,RX 会发送一个 SYNC 请求重新开始该过程。

第一次使用新技术可能会令人生畏。如果您正考虑在下个项目中使用该接口,希望我对 JESD204B 中协议的简单介绍能帮助您缓解这种不适。

您是否希望进一步了解 JESD204B 的优势?我在这里列出了一些其它资源:

原文请参见: http://e2e.ti.com/blogs_/b/analogwire/archive/2014/07/30/jesd204b-understanding-the-protocol.aspx

/3

/3

文章评论(0条评论)

登录后参与讨论