接第三章

Page Protection

After a virtual address is determined to be within a page covered by the valid PTE,则访问是被存储器保护机制确认的,如果保护机制限制了访问,data page fault exception会产生。

存储器保护机制分别允许supervision and user模式进行读写访问,而页保护机制提供了在所有页面级粒度的保护。

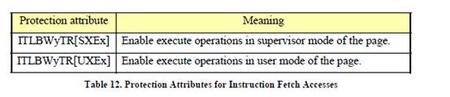

图12列出了ITLBWyTR寄存器中定义的页保护属性,For the individual page appropriate strategy out of seven possible strategies programmed with the PPI field of the PTE。由于OR1200没有实现IMMUPR,翻译PTE[PPI]到合适的protection位必须由软件写入DTLBWyTR。

ITLB entry reload

OR1200并不支持硬件进行ITLB entry reload,采用软件为正确的PTE(page table entry)搜索page table及拷贝其到ITLB。软件负责管理在page table中的accessed和dirty bits。

当LSU计算load/store有效地址的时候,但其物理地址在ITLB还没有的时候,ITLB miss异常会发出。

ITLB reload过程必须load正确的PTE到正确的ITLBWyMR中。

ITLB entry invalidation

目的寄存器ITLBEIR必须写入有效地址,相应的ITLB entry在本地的ITLB中将会无效。

Locking ITLB Entries

由于所有的ITLB entry采用软件load,因而无硬件locking ITLB entry。采用软件的方式可以避免一些entry被替换掉。

Page attribute-dirty(D)

Dirty attribute在OR1200DTLB中并未实现,It is up to the operating system to generate dirty attribute bit with page protection mechanism。

Page attribute-accessed(A)

Accessed attribute在OR1200DTLB中并未实现,It is up to the operating system to generate dirty attribute bit with page protection mechanism。

Page attribute-weakly ordered memory(WOM)

由于存储器访问是顺序的,WOM在OR1200中也并未实现。

Page attribute-write back cache(WBC)

由于data cache仅仅进行write-through模式的操作,因而WBC在OR1200中并未实现。

Page attribute-Caching-Inhibited (CI)

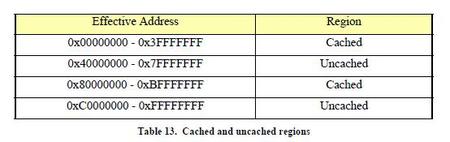

Cached和uncached边界是以30bits作为有效地址划分的,因而CI在OR1200中也并未实现。

当所有的I/O寄存器采用存储器映射时,必须采用uncached访问,必须采用直接读写外部接口的方式,而不是访问data cache。

由于不支持多处理器环境及data cache仅进行write-through模式,因而cache coherency attribute并未在OR1200中进行实现。

Page attribute-Caching-coherency (CC)

CCattribute在PTE中,但在IMMU中并未使用。

Programmable interrupt controller

PICMR特殊目的寄存器用于mask or unmask最多30个可编程中断源。PICMR特殊目的寄存器用于为30个可编程中断源分配低或者高的优先级。

PICMR特殊目的寄存器用于决定每个中断输入的状态,PICMR中的bit位代表中断输入的状态,实际的中断必须清楚在设备中的未决(未解决的中断)中断源。

Tick Timer

采用TTMR[M]位可以对Tick timer设备进行使能,TTCR随着每个时钟周期增加,无论何时当TTCR的低28bits和TTCR[TR]及TTMR[IE]匹配存在时,Tick timer的更高级的优先权将会产生。

当TTMR[m]位设置为0x01时,TTCR将会复位为0重新计数,如果设置为0x02时, TTCR将停止计数,当事件匹配发生时,TTCR重新开始计数,当设置为0x03时,即使发生事件匹配,TTCR仍然保持计数。

Power Management

Clock gating and frequency changing versus cpu stalling

如果系统不支持门控时钟及将系统频率降低不可实现,cpu can be stalled for certain of clock cycles。功耗降低的效率将会变得很低,但是仍然会降低功耗消耗

Slow down mode

Slow down mode采用软件控制4bit寄存器PMR[sdf],值越低表明希望获得更好的处理器核的性能,通常PMR[sdf]是在操作系统idle历程中动态设置的,能够监控处理器核的使用情况。

PMR[sdf]在信号pc_clksd信号上进行广播,外部的时钟产生模块应该调整时钟以适应pm_clksd的值。准确的slow down 参数并未定义,but 0xF should go all the way down to 32.768 KHz。

当pm_clksd等于0xF时,可以检测到pm_lvolt信号。这表示的是外部电源提供了更低的电压。

Doze mode

通过设置PMR[DME]可以切换模式到doze mode,一旦可编程中断控制器收到一个中断后,pm_wakeup信号被激活,外部时钟产生电路应该使能所有的时钟。一旦时钟跑跑起来,risc切回到正常模式,PMR[dme]信号被清除。

当doze模式使能后,pm_dc_gate,pm_ic_gate,pm_dmmu_gate,pm_immu_gate及pm_cpugate信号被激活,这样除了clk_tt时钟信号,其它时钟信号应该被外部的时钟产生电路进行门控管理。

Sleep mode

通过设置PMR[sme]可以切换模式到sleep mode,一旦可编程中断控制器收到一个中断后,pm_wakeup信号被激活,外部时钟产生电路应该使能所有的时钟。一旦时钟跑跑起来,risc切回到正常模式,PMR[sme]信号被清除。

当sleep模式使能后,pm_dc_gate,pm_ic_gate,pm_dmmu_gate,pm_immu_gate及pm_cpugate信号被激活,这样除了clk_tt时钟信号,其它时钟信号应该被外部的时钟产生电路进行门控管理。

在sleep模式中,pm_lvolt信号被激活,这表示的是外部电源提供了更低的电压。

Clock gating

门控时钟在or1200功耗管理单元中并未实现。

Disabled unit force clock gating

Units that are disabled in special-purpose register SR, have their clock gate signals asserted. Cleared bits SR[DCE], SR[ICE], SR[DME] and SR[IME] directly force assertion of pm_dc_gate, pm_ic_gate, pm_dmmu_gate and pm_immu_gate.

Debug unit

Debug 单元可以通过开发接口进行控制,可进行独立的可编程操作及可以用risc内部的调试软件进行控制。

Watchpoints

OR1200调试单元并没有实现watchpoints的功能。

Breakpoints

断点DMR2[WGB]位指定观察点调用断点异常,靠调用断点异常,可以实现内建调试器。可以在开发接口上的dbg_bp_o信号上进行断点的广播。

Development interface

更为详细的可能连接到or1200上的development及debug接口ip核的详细信息可以参见利用ieee1149.1(jtag)协议标准调试器。

Debugging through development interface

DSR特殊目的寄存器指定了一些会造成处理器停止执行异常操作的一些异常情况,反过来交给开发接口进行控制。这些异常可以通过内建的调试软件或者开发接口进行可编程处理。

DSR特殊目的寄存器指定了一些会造成处理器停止可编程流操作的一些异常情况,反过来交给开发接口进行控制。这些异常可以通过内建的调试软件或者开发接口进行可编程处理。

DIR特殊目的寄存器并未实现。

Reading pc;load/store EA,load data,store data, instruction

一些重要的信息像program counter(pc),load/store effective address(lsea),load data,store data 及采用流水线执行的current instruction可以利用开发接口进行异步读操作。

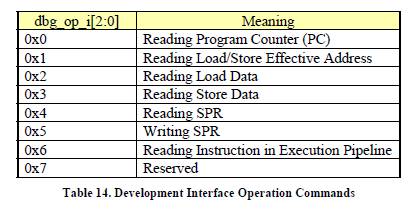

表14列出了可以通过开发接口进行读写操作的操作命令。除了sprs的读写操作,其它的读操作都是异步的。

Reading and writing sprs through development interface

对于读写sprs,dbg_op_i必须分别设置为0x4和0x5。

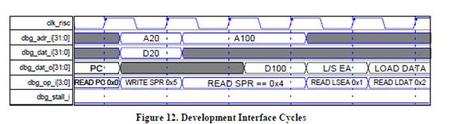

图12给出了开发接口的时序图,写操作应该同步于risc时钟,并且在上升沿进行采样且花费一个时钟周期。由于访问同步cache lines或者TLB entries需要一个周期的延时,因而读周期需要两个周期。

Tracking data flow

外部调试器可以监控及记录risc中的数据流用于调试和文件分析,这些可以通过监控load/store unit, load/store effective address and load/store data及其它可能的开发接口状态进行实现。

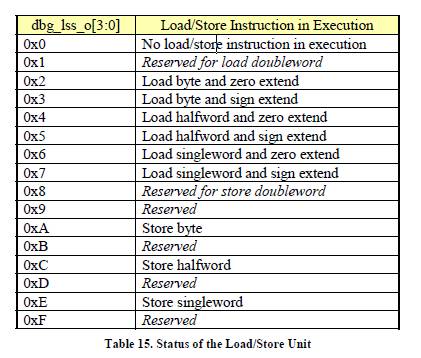

外部trace buffer可以通过分析load/store unit中dbg_lss_o信号的状态捕获所有关心的数据流事件。表15列出了load/store unit不同状态的译码。

Tracking data flow

外部调试器可以监控及记录risc中的数据流用于调试和文件分析,这些可以通过监控instruction unit,pc,取指令字及其它可能的开发接口状态进行实现。

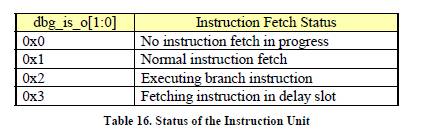

外部trace buffer可以通过分析load/store unit中dbg_is_o信号的状态捕获所有关心的数据流事件。表15列出了load/store unit不同状态的译码。

Triggering external watchpoint event

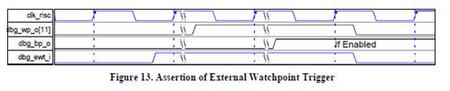

图13给出了开发接口如何捕获dbg_ewt_I信号而造成的watchpoint事件,如果可编程,外部watchpoint事件会造成一个断点异常。

/3

/3

文章评论(0条评论)

登录后参与讨论