第四章 寄存器(Register)

本部分将会描述在or1200核中用到的所有寄存器,向左移位GPR11位加上REG number计算每个特殊目的寄存器的地址。从软件的角度看所有的寄存器都是32bits。USER mode和supv mode指定USER mode和supv mode中每个寄存器有效访问类型。R/W代表读写访问,R仅代表读访问。

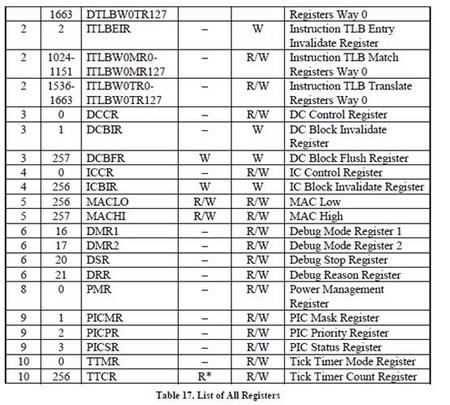

表17列出了所有OR1000特殊目的寄存器中在OR1200中已经实现了的。寄存器VR和UPR在下面描述。如果需要对其它寄存器有更多的认识,请参考OR1000系统架构手册。

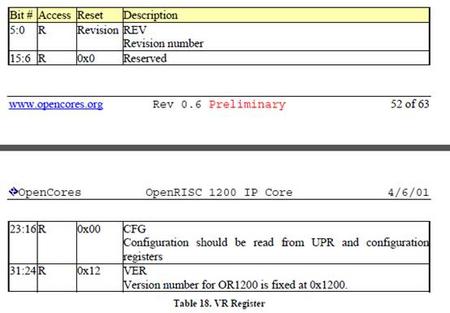

Register VR description

特殊目的寄存器VR定义了OR1200处理器的版本(version)和版本标识(reversion),也定义了实现时所采用标准模板。

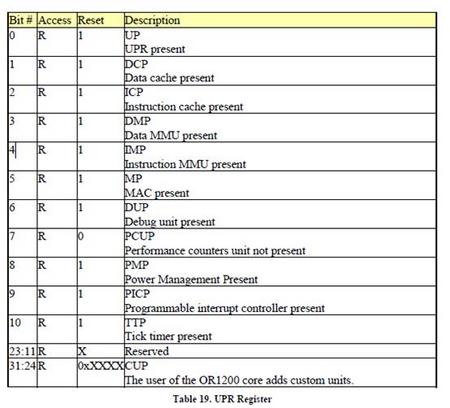

Register UPR description

特殊目的寄存器UPR定义了出现在处理器中的单元,每个实现单元或功能都对应一个bit。低16bits代表在OR1000架构中定义的单元,高16bits定义代表当前的通用单元。

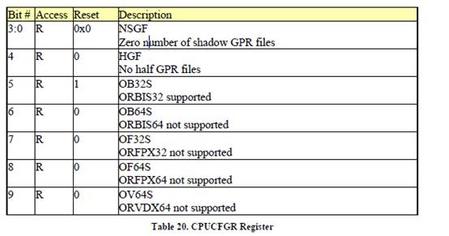

Register CPUCFGR description

特殊目的寄存器CPUCFGR定义了cpu的功能和配置。

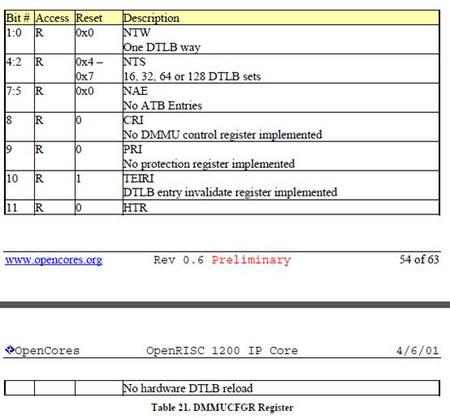

Register DMMUCFGR description

特殊目的寄存器DMMUCFGR定义了DMMU的功能和配置。

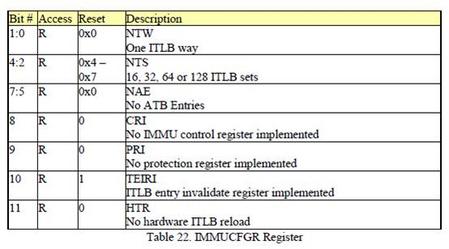

Register IMMUCFGR description

特殊目的寄存器IMMUCFGR定义了DMMU的功能和配置。

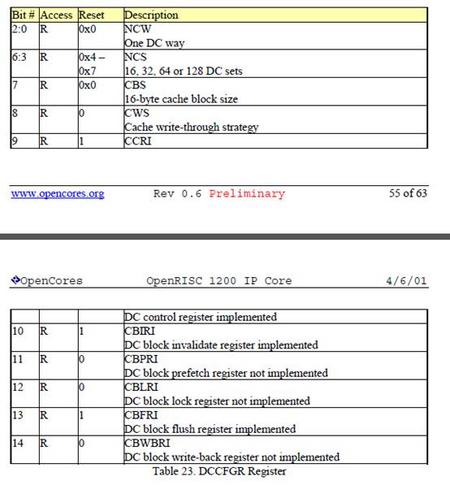

Register DCCFGR description

特殊目的寄存器DCCFGR定义了data cache的功能和配置。

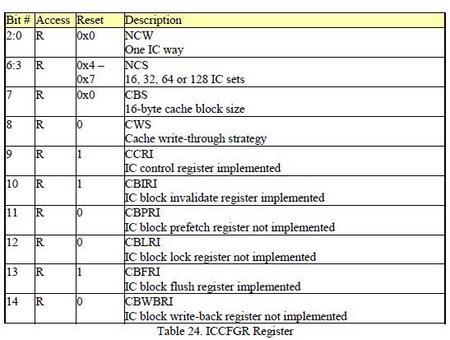

Register ICCFGR description

特殊目的寄存器ICCFGR定义了instruction cache的功能和配置。

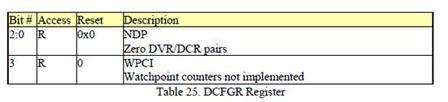

Register DCCFGR description

特殊目的寄存器DCFGR定义了debug unit的功能和配置。

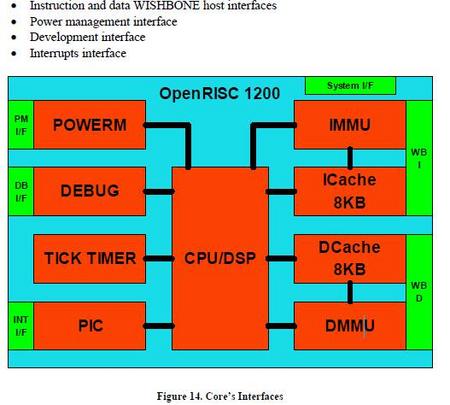

第五章 IO ports

OR1200IP核中有一些接口,图14给出了所有的接口类型:

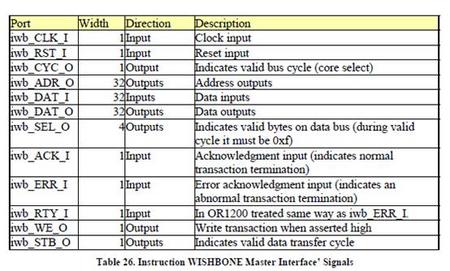

Instruction wishbone master interface

OR1200有两种master wishbone版本兼容接口,指令接口用于连接Or1200和到存储器子系统用来取指令或者指令行(instructions or instruction cache lines)。

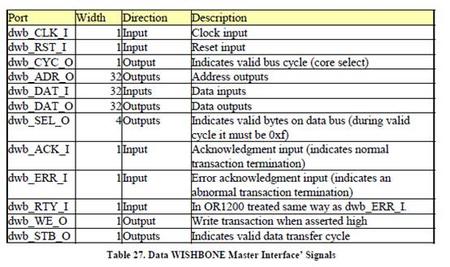

Data wishbone master interface

OR1200有两种master wishbone版本兼容接口,数据接口用于连接Or1200和到存储器子系统及外围设备用来读写数据及数据行(data or data cache lines)。

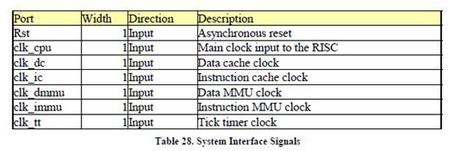

System interface

系统接口连接复,时钟及其它系统信号到OR1200处理器核。

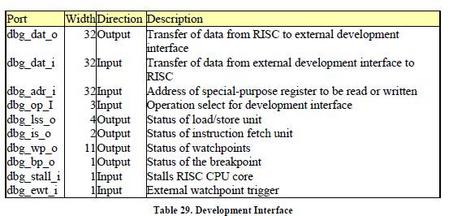

Development interface

开发接口用于连接外部开发接口到RISC内部调试设备中,调试设备允许控制在RISC中执行编程调试,设置断点和观察点,数据流和指令流的跟踪调试。

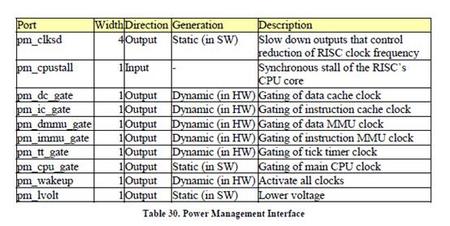

Power management interface

功耗管理接口提供外部功耗管理单元电路的信号接口用于连接RISC核。外部功耗管理电路单元需要实现基于指定工艺的一些功能,在OR1200核中没有进行实现。

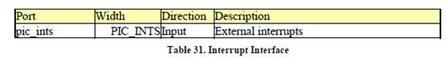

Interrupt interface

中断接口有中断输入用于连接外部设备的中断输出到RISC核。所有的中断输入都在主时钟上升沿进行有效采样。

/2

/2

文章评论(0条评论)

登录后参与讨论