前一阵子因项目需要,积极寻找一款尺寸小,功率低,接口适配,性能中等的FPGA芯片用作图像的采集、处理和传输,最终锁定了Lattice的下一代CrossLink系列器件CrossLinkNX。

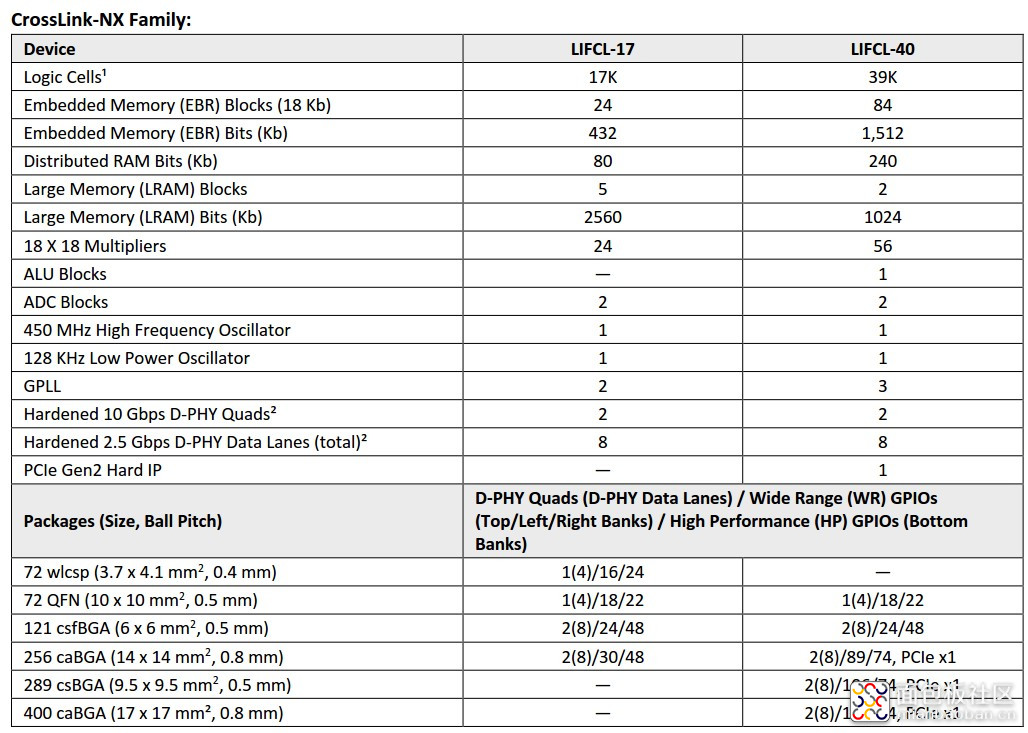

这个系列的器件有两个子类,分别是17K逻辑的LIFCL-17和39K逻辑的LIFCL-40子类。其中LIFCL-17封装最小的是wlcsp72-3.7mm*4.1mm,最大的是caBGA256-14mm*14mm,内部EBR RAM容量432Kb,Large RAM容量2560Kb,1~2个2.5Gbps MIPI DPHY硬核,不支持PCIe;LIFCL-40封装最小的是QFN72-10mm*10mm,最大的是caBGA400-17mm*17mm,内部EBR RAM容量1512Kb,Large RAM容量1024Kb,1~2个2.5Gbps MIPI DPHY硬核,支持PCIe硬核和DDR。下图1是CrossLink NX系列器件的资源截图。

图1 CrossLink NX系列器件资源列表

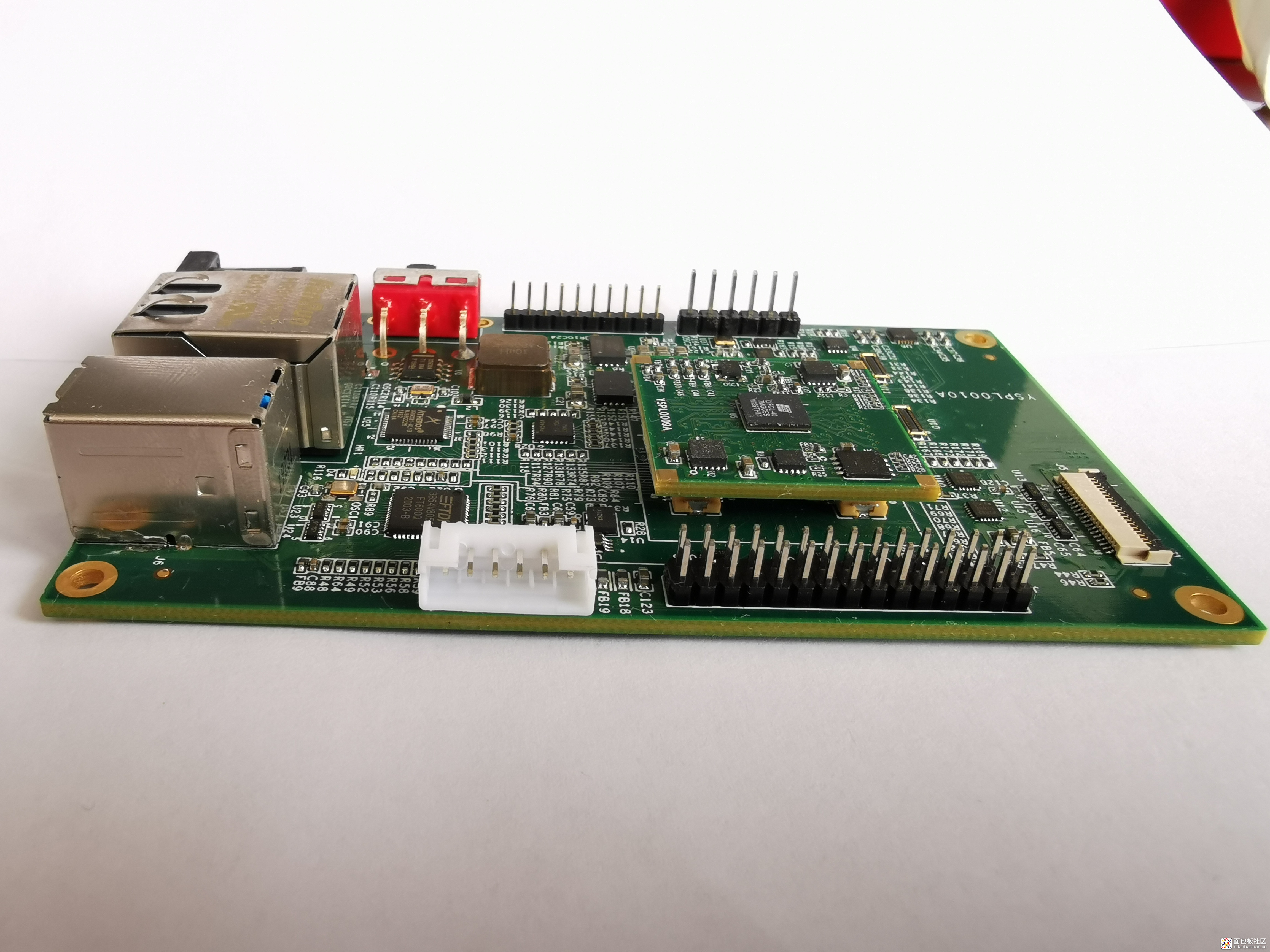

我的应用很简单,采集一路或2路1080P/720P的CMOS 成像帧率高点儿的Sensor图像进来,接口可以是MIPI DPHY或者LVDS(及兼容的SubLVDS或Hispi),经过RAW图像域处理或者简单ISP处理后做一些算法,通过USB3.0或千兆以太网输出预览图或者处理结果,这个FPGA集成了SGMII CDR,可以无需其他外设就实现千兆以太网协议。因为要装在空间受限的位置,所以我考虑的就是小封装的器件,带PCIe这种根本就用不上,最终用了caBGA121-6mm*6mm LIFCL-40,RAM、乘法器和逻辑资源、接口刚刚够。因此对这种要体积小,功耗低,性能和接口都需要中等偏上,成本适中的应用来说,是一种较为合适的选择。下图2是我的一个原型验证电路(正式产品的体积是24mm*24mm*35mm,比这个核心板22mm*22mm的尺寸大一点儿)。

图2(a) 核心板

图2(b)验证载板

总的来说,个人认为CrossLink NX系列FPGA主要还是面向以下领域:

(1)视频桥接:延续上一代Crosslink系列器件的特点,升级MIPI DPHY硬核到支持2.5Gbps/Lane速率,升级真差分IO支持LVDS电平1.25Gbps。在汽车影音系统、多屏或多画面显示需要用到多路MIPI拼成1路MIPI或一路MIPI到多路MIPI的分发,LVDS和MIPI之间的转换缩放以及挂在一些纯计算类的处理器作为前端接口等应用,无疑是比较适合的选择;

(2)工业相机:升级了MIPI速率、LVDS速率和逻辑运行时钟速率之后,无疑可以干很多事情,可以支持更大幅面和更高帧率的工业采集和处理,再加上体积小,特别适合一些对体积有要求的比如焊缝跟踪系统、基于视觉的复杂无损探伤系统、复杂的机器视觉系统前端等等,体积、功耗低、速率高是一大优势。

(3)消费级应用:因为芯片在价格等各方面还算适中,所以在消费级领域还是有一定的市场,wlcsp72这类小封装的器件甚至可以做到手机里面去用于做一些时序控制,多协议视频图像流的桥接转换等等,当年IPhone手机就用了lattice的小封装器件。一些消费产品配套可编程逻辑器件确实增加了产品的灵活性。

说了这么这么多,吐槽一下开发工具,我是用Radiant来做的,这个软件的体验和Quartus、Vitis/Vivado/ISE以及他自家的Diamond比,还是差了一大截,比较的一言难尽,想不通为啥还要从Diamond里面独立出来这么一个来。

另外就是这个器件截止发博日,只有部分器件量产,还有一些是工程样片阶段,在功能上还有一些BUG(lattice会出具一份告知文件),周期上也不短。因此要选用这个器件,需要实现跟FAE沟通清楚。

以下图片是微信公众号和QQ技术交流群的二维码,欢迎一起讨论交流。

作者: panda君, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3403128.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论