本入门分享一共三篇,目的是为了帮助新手利用Lattice Radiant Software创建第一个新工程、使用在线调试器和使用RSIC-V软核。基本的软硬件配置如下:

(1) 软件开发平台:Lattice Radiant Software 2.0.1.281.2和Lattice

Propel1.1。

(2) 评估板:CrossLinkNx Base(编号YSPL0010A,公司自制)

(3) 器件 :LIFC-40-7MG121C(ES器件)

(4) 调试器:Lattice HW-USBN-2B

2 创建第一个工程本章介绍如何创建第一个CrosslinkNX工程。

2.1 创建新工程目标:创建一个新工程,使用内部的osc产生50MHz的时钟作为系统的工作时钟,利用计数器产生50Hz的方波,生成bit文件并将bit文件烧写到SPI Flash中。

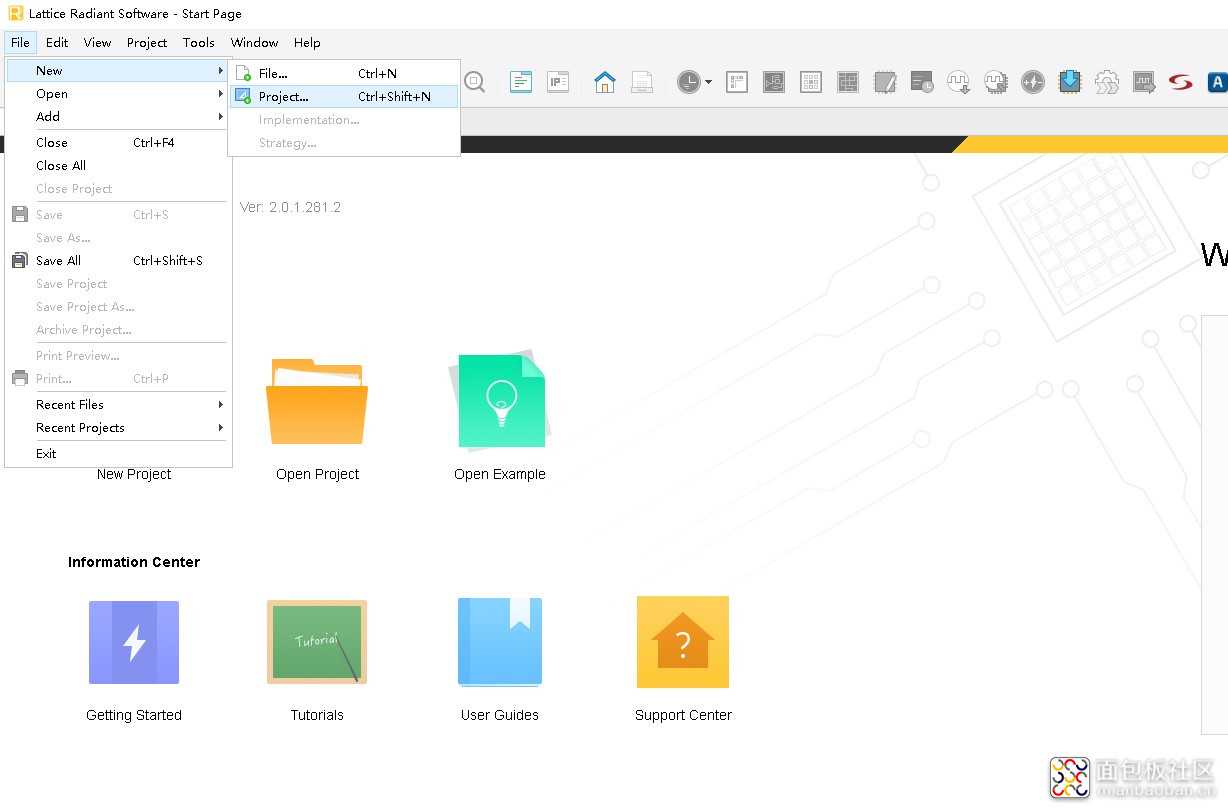

Step1:打开 Radiant软件,选择File->New->Project。

图1 创建新工程界面

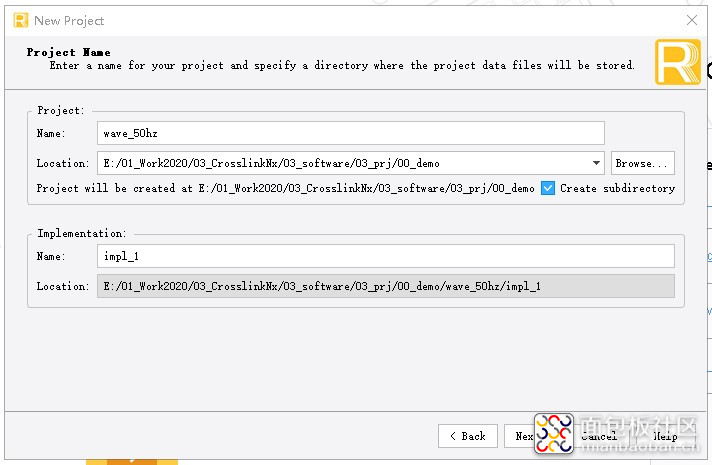

Step2:选择工程路径和工程名,这里命名为wave_50hz。

图2 选择新工程路径和命名

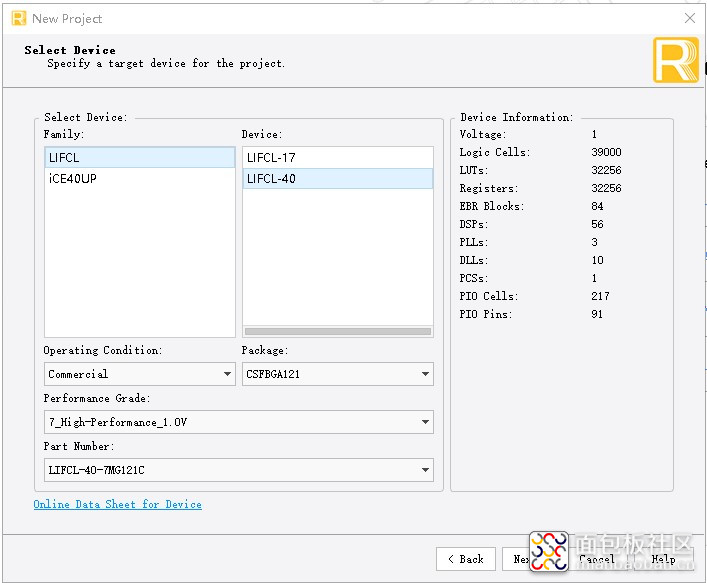

Step3:一路下一步,根据自己用的芯片选择器件,我的板子上是LIFCL-40-7M121C,如下图

图3 选择器件

Step4:一路下一步,直到工程创建完毕。

2.2 添加和编译文件一个完整的工程,至少具备顶层文件、约束文件和若干IP,本例生成一个简单的50Hz方波,因此需要一个OSC IP来产生时钟、一个约束文件来指定IO[使用内部时钟,时钟约束文件已经自动产生,因此不需要在约束文件里面特别指定]、一个顶层vhd文件。

2.2.1 生成OSC IPLattice CrossLink NX FPGA内部有一个450MHz时钟单元,通过IP来例化调用。

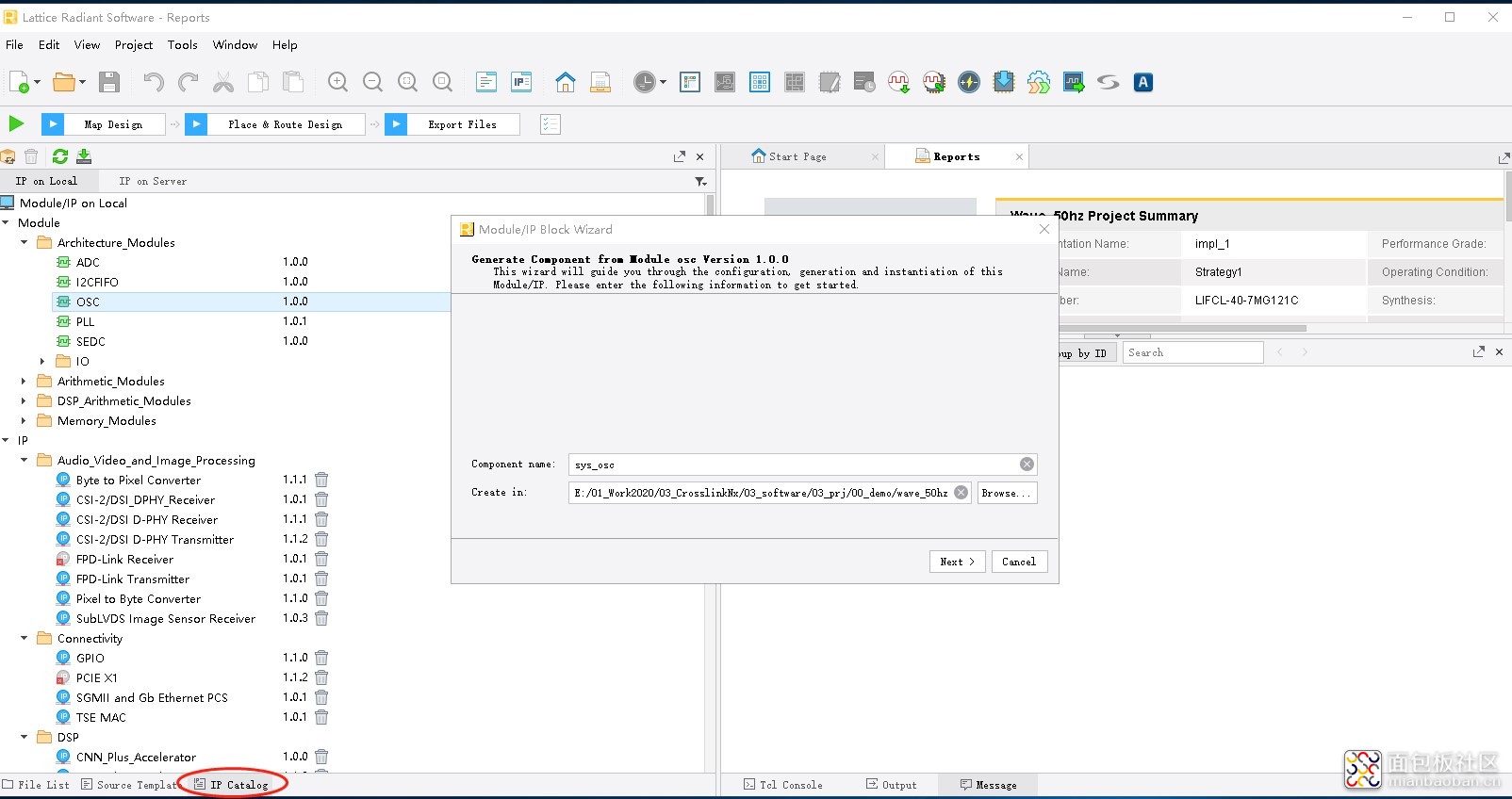

Step1:选择IP Catalog,双击OSC IP核,并将之命名为sys_osc。

图4 生成OSC IP

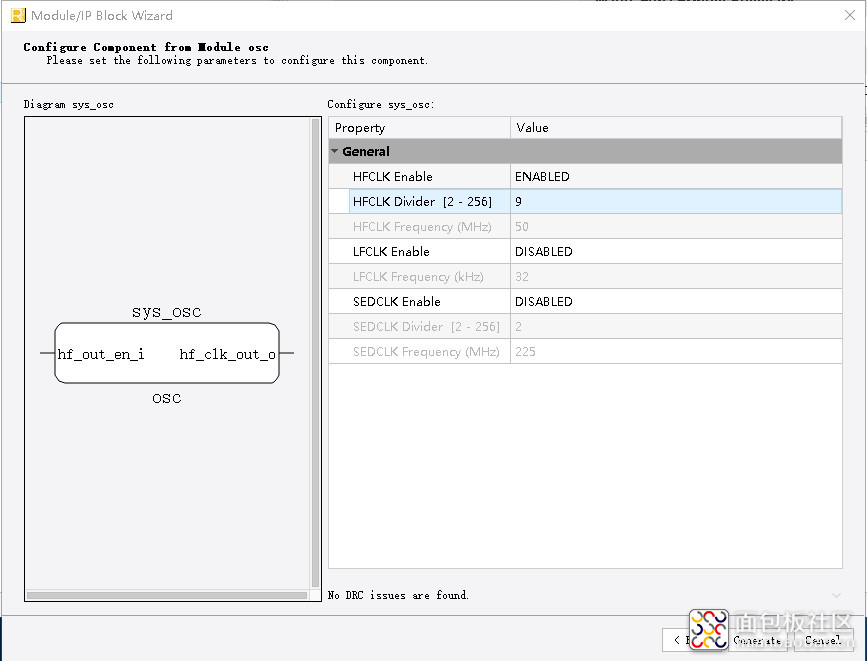

Step2:选择Next,配置HFCLK Divider参数为9,点击Generate。

图5 配置OSC IP

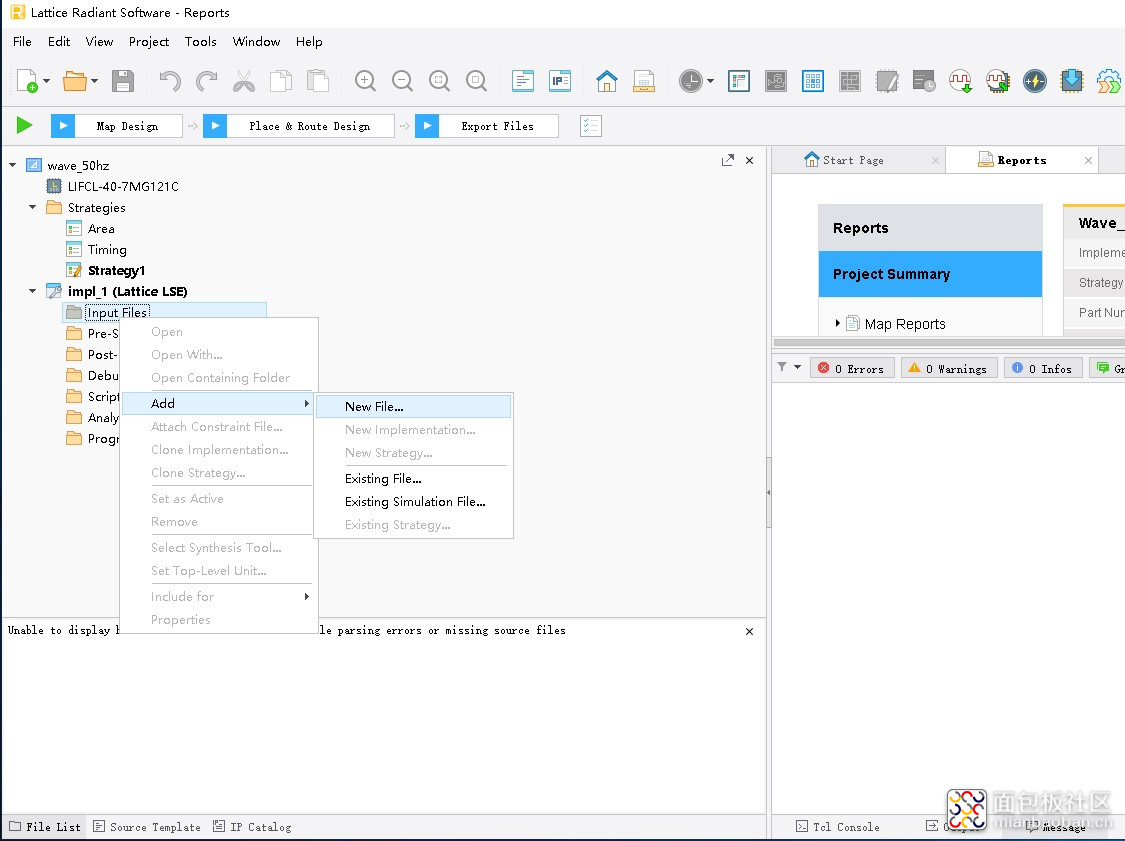

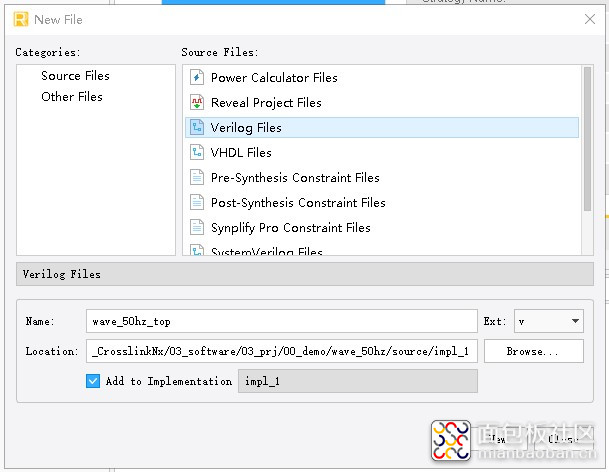

2.2.2 编写顶层文件Step1:在File List下,选择input File->Add->New File建立一个新文件,选择类型为Verilog Files,命名为wave_50hz_top,点击new完成创建。

图6 创建HDL文件

图7 选择新创建文件属性

Step2:编写文件

为形成良好的编码习惯,一个verilog文件里面需要包含注释、仿真精度和实体模块等信息,本文件例化之前生成的sys_osc,并编写产生方波的文件,示例如下:

//------------------------------------------------------------

//File Name: wave_50hz_top

//

//Project : top moudle of generate 50Hz sqrt wave

//

//Module : top

//

//Content : none

//

//Description : 50MHz clock generate by intel OSC

//

//Spec. : none

//

//Author : Hello,Panda

//------------------------------------------------------------

//History :

//20200804: V1.0 -Initial Creation

//------------------------------------------------------------

`timescale 1ns / 1ps

module wave_50hz_top(

output wire o_wave_50hz //output port

);

reg [15 : 0] r_chip_cnt = 16'd0 ;

reg r_chip_rstn = 1'b0 ;

reg [9 : 0] r_low_cnt ;

reg [9 : 0] r_high_cnt ;

reg r_wave ;

wire w_chip_clk_50m;

/***************************************************************/

//part1:osc genrate clock

/***************************************************************/

sys_osc u_sys_clk_inst(

.hf_out_en_i (1'b1 )

,.hf_clk_out_o (w_chip_clk_50m )

);

always @ (posedge w_chip_clk_50m)

begin

r_chip_cnt <= (&r_chip_cnt) ? r_chip_cnt : (r_chip_cnt + 1'b1);

r_chip_rstn <= (r_chip_cnt >= 16'd32768) ? 1'b1 : 1'b0;

end

/***************************************************************/

//part2:generate wave

/***************************************************************/

always @ (posedge w_chip_clk_50m)

begin

if(~r_chip_rstn) begin

r_low_cnt <= 10'd0;

r_high_cnt <= 10'd0;

r_wave <= 1'b0 ;

end

else begin

if(r_low_cnt >= 10'd999) begin

r_low_cnt <= 10'd0;

r_high_cnt <= (r_high_cnt >= 10'd999) ? 10'd0 : (r_high_cnt + 1'b1);

end

else begin

r_low_cnt <= r_low_cnt + 1'b1;

r_high_cnt <= r_high_cnt ;

end

r_wave <= (r_high_cnt >= 10'd499) ? 1'b1 : 1'b0;

end

end

assign o_wave_50hz = r_wave;

endmodule

备注:50Hz频率的周期为20ms,50MHz的周期为20ns,即需要计数器计满1000*1000个节拍为20ms。

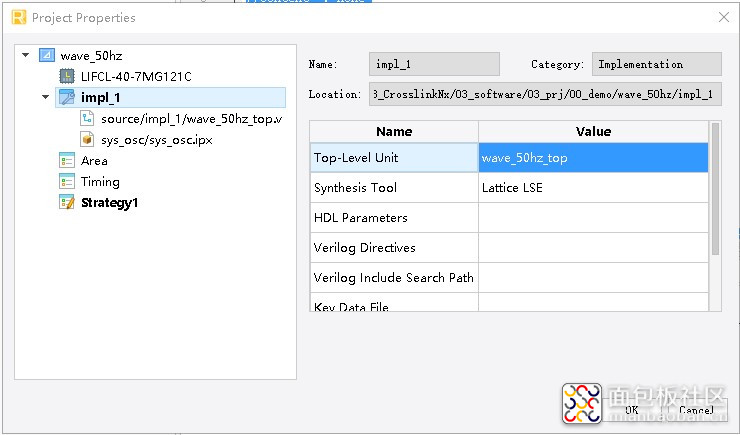

Step3:添加wave_50hz_top为顶层文件

右键inpl_1选择Set Top level Unit,将wave_50hz_top指定为顶层文件。

图8 设置顶层文件

2.2.3 编写约束文件本例中约束文件包括IO、使能JTAG和使能MASTER_SPI_PORT原语。约束文件既可以先行写好添加,也可以通过综合以后在Device Constraint Editor、Timing Constraint Editor等图形界面添加,本例选择第一种,约束文件的语法请参考Lattice的官方文件,也可在软件Tools->Source Templates里看到一部分。

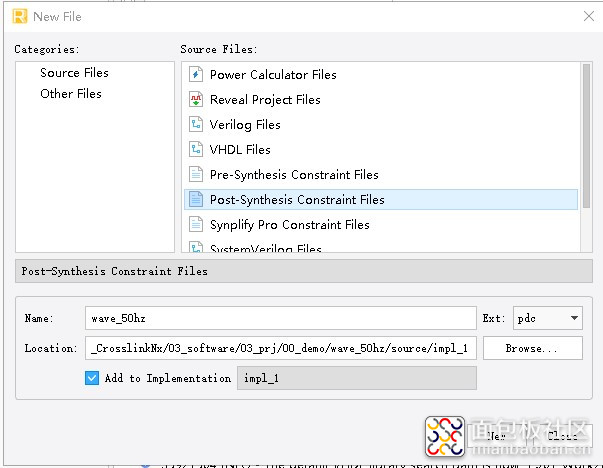

Step1:新建一个Post-Systhesis约束文件,命名为wave_50hz.pdc,点击new。

图9 创建约束文件

Step2:编写约束

(1) 指定IO:指定IO引脚号为G1,电平标准1.8V LVCMOS和其他属性;

(2) 使能JTAG:使能JTAG;

(3) 使能MASTER_SPI_PORT,并指定其工作时钟频率为3.5MHz。

ldc_set_location -site {G1} [get_ports o_wave_50hz]

ldc_set_port -iobuf {IO_TYPE=LVCMOS18H SLEWRATE=SLOW} [get_ports o_wave_50hz]

ldc_set_sysconfig {MASTER_SPI_PORT=SERIAL BOOTMODE=SINGLE CONFIGIO_VOLTAGE_BANK0=1.8 CONFIGIO_VOLTAGE_BANK1=1.8 MCCLK_FREQ=3.5 CONFIG_IOSLEW=FAST}

ldc_set_sysconfig {JTAG_PORT=ENABLE}

2.3 布局布线和导出文件点击Export Files按钮,软件可以一键完成综合、布局布线、生成bit文件等工作。

2.4 Bit文件下载有两种类型,一种是下载到FPGA的配置SRAM,掉电即丢失,适合调试时使用。一种是烧写到SPI Flash进行程序固化,上电加载到FPGA运行。

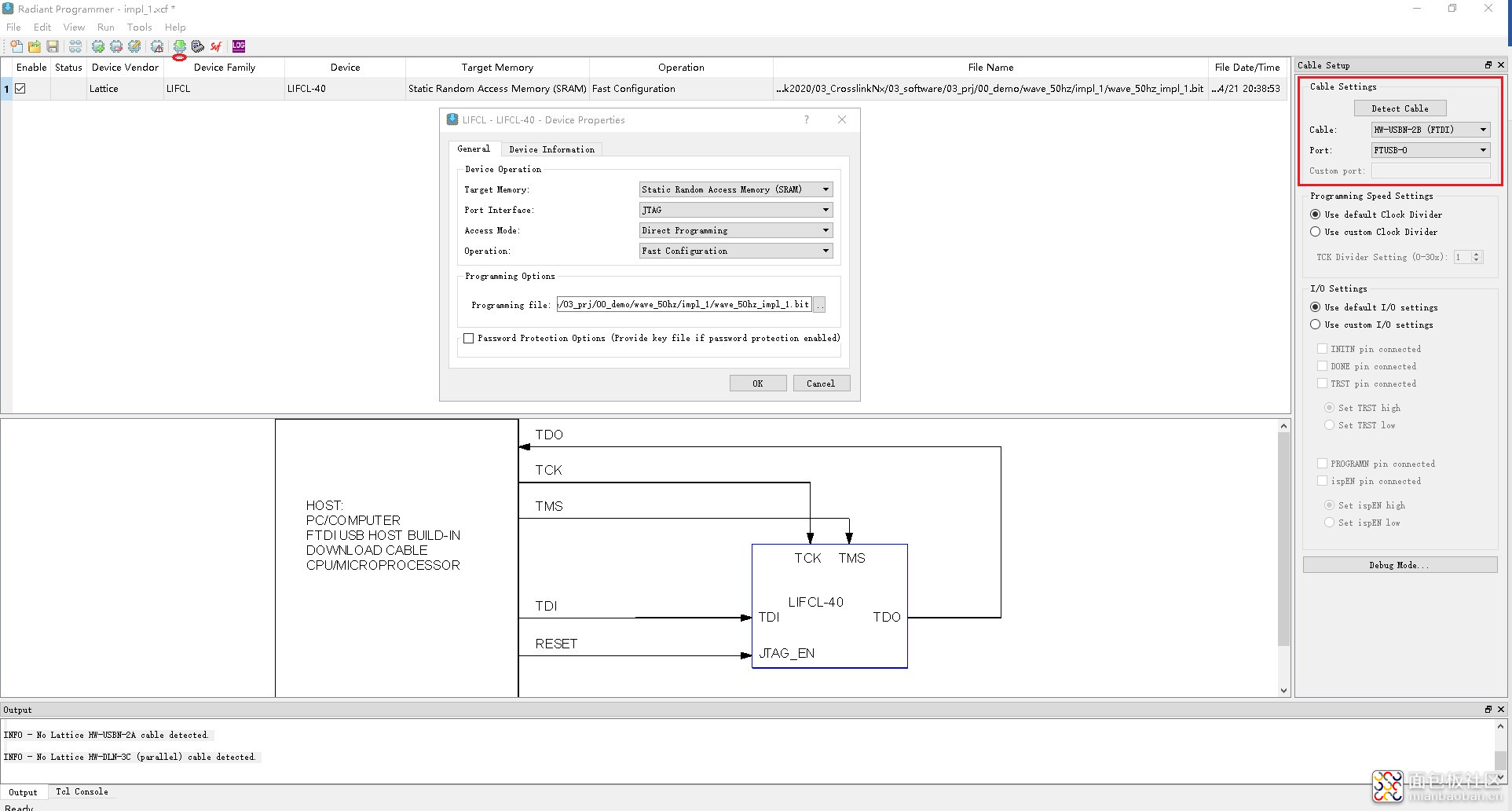

首先,点击Tools->Programer按钮,进入烧写工具界面。

2.4.1 下载到FPGA SRAM如下图所示,双击Target Memory或Operation下面的复习项弹出配置菜单,根据实际硬件情况选择JTAG的类型、选择Target Memory为SRAM是,File Name选项指定到bit文件所在位置,Port Interface选择为JTAG,Acess Mode选择为Direct Programing,Operation为Fast Configuration。

图10 下载到FPGA SRAM配置界面

点击绿色的下载按钮,等待下载完成,完成后下方的output栏会提示successful。

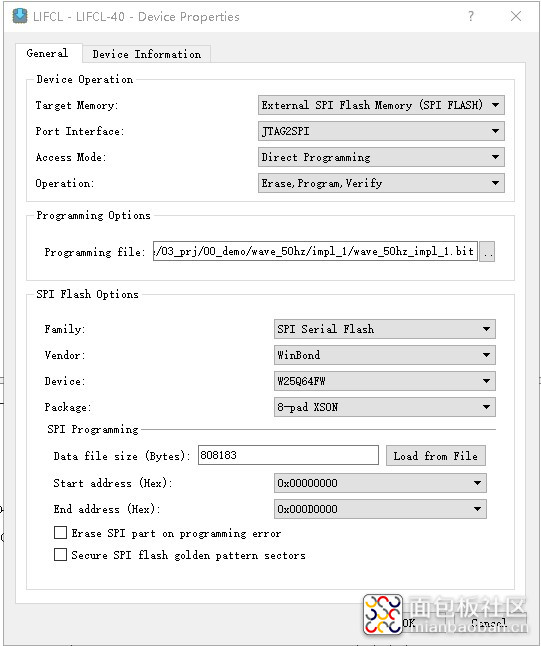

2.4.2 固化到SPI Flash将bit文件固化到spi flash,首先应将其下载到fpga的sram使能MASTER_SPI_PORT使JTAG2SPI命令可以正常工作。烧写到SPI Flash的文件既可以是bit文件,也可以是mcs文件,本例选择直接烧写bit文件。

如下图所示,选项如下:

(1) Target Memory:Extern SPI Flash Memory ;

(2) Port Interface:JTAG2SPI;

(3) Operation:Erase,Program,Verify;

(4) Programming File路径指向bit文件所在位置;

(5) 选择SPI Flash的型号;

(6) 根据bit文件的大小设置烧写到Flash的起始地址。

设置完成后点击绿色的下载按钮,等待下载到SPI Flash完成,output栏会提示进度和完成状态。

图11 固化到SPI Flash配置界面

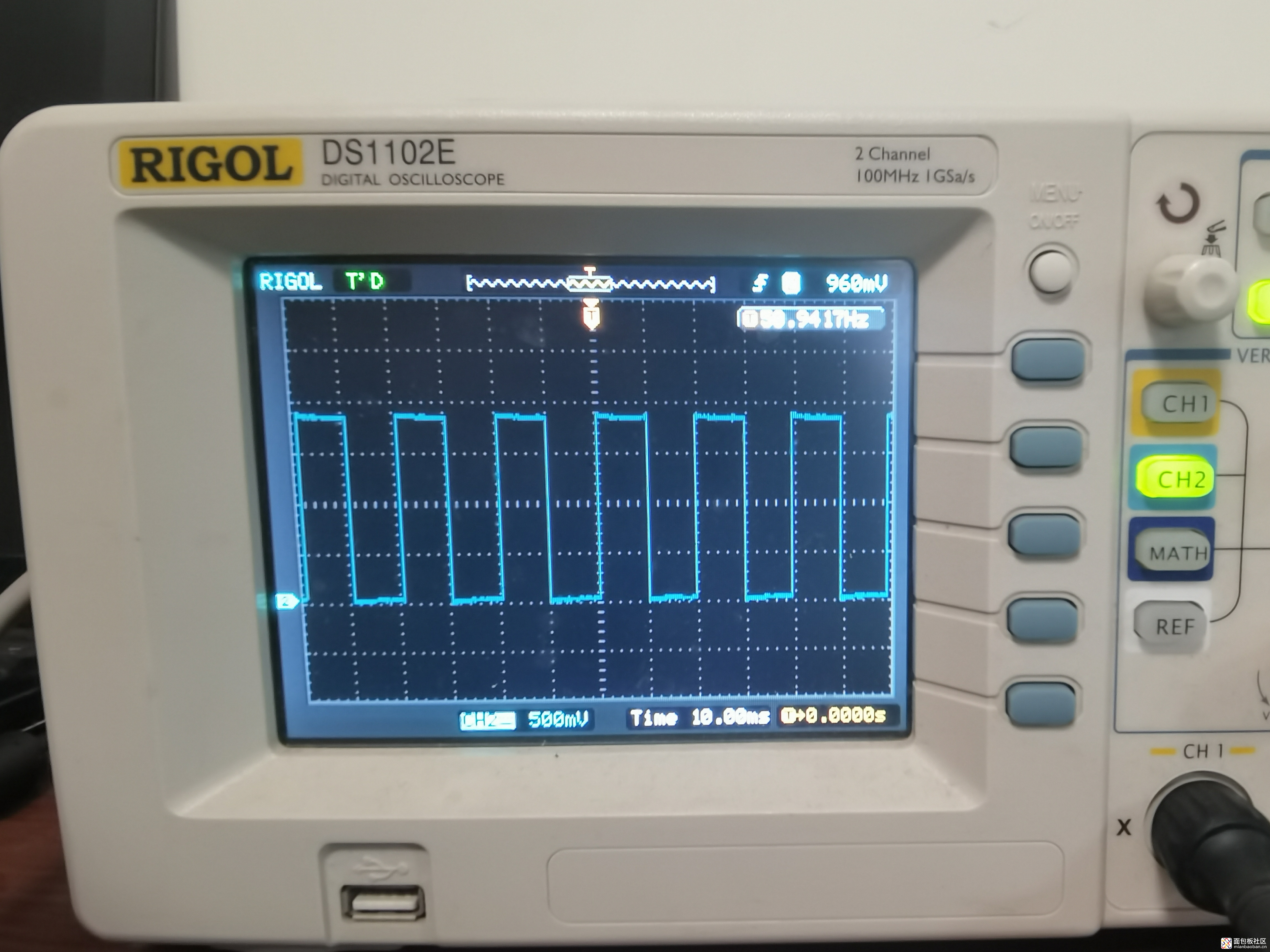

2.5 功能确认用示波器测量输出引脚,可以看到频率为50Hz,幅度为1.8V的方波。

作者: panda君, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3403128.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

curton 2021-1-15 17:28

欢迎点击

论坛> >机器人/工业电子> >工业电子与自动化

https://mbb.eet-china.com/forum/topic/85437_1_1.html