一、问题描述:

(1)器件:Lattice Crosslink-NX LIFCL-40-7MG121I ;

(2)软件:Radiant 3.1;

(3)MIPI_DPHY IP核版本:1.4.0;

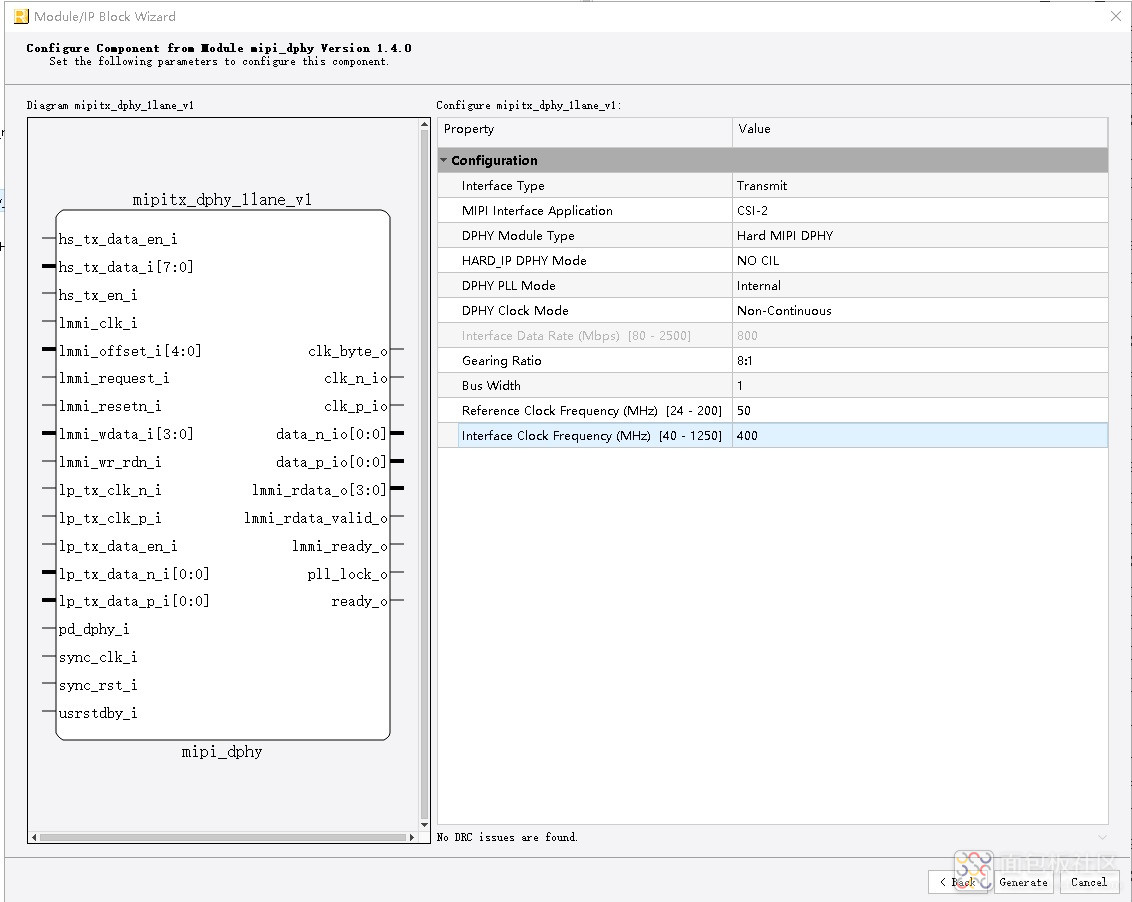

(4)IP核的配置:1-lane MIPI发送,无CIL,非连续时钟模式,见下图。

存在的问题是:MIPI CSI层控制以下信号无法产生正确的非连续时钟发送时序。

hs_tx_en_i, hs_tx_data_i, hs_tx_data_en_i, lp_tx_data_p_i, lp_tx_data_n_i, lp_tx_data_en_i,

lp_tx_clk_p_i, lp_tx_clk_n_i。

二、问题查找

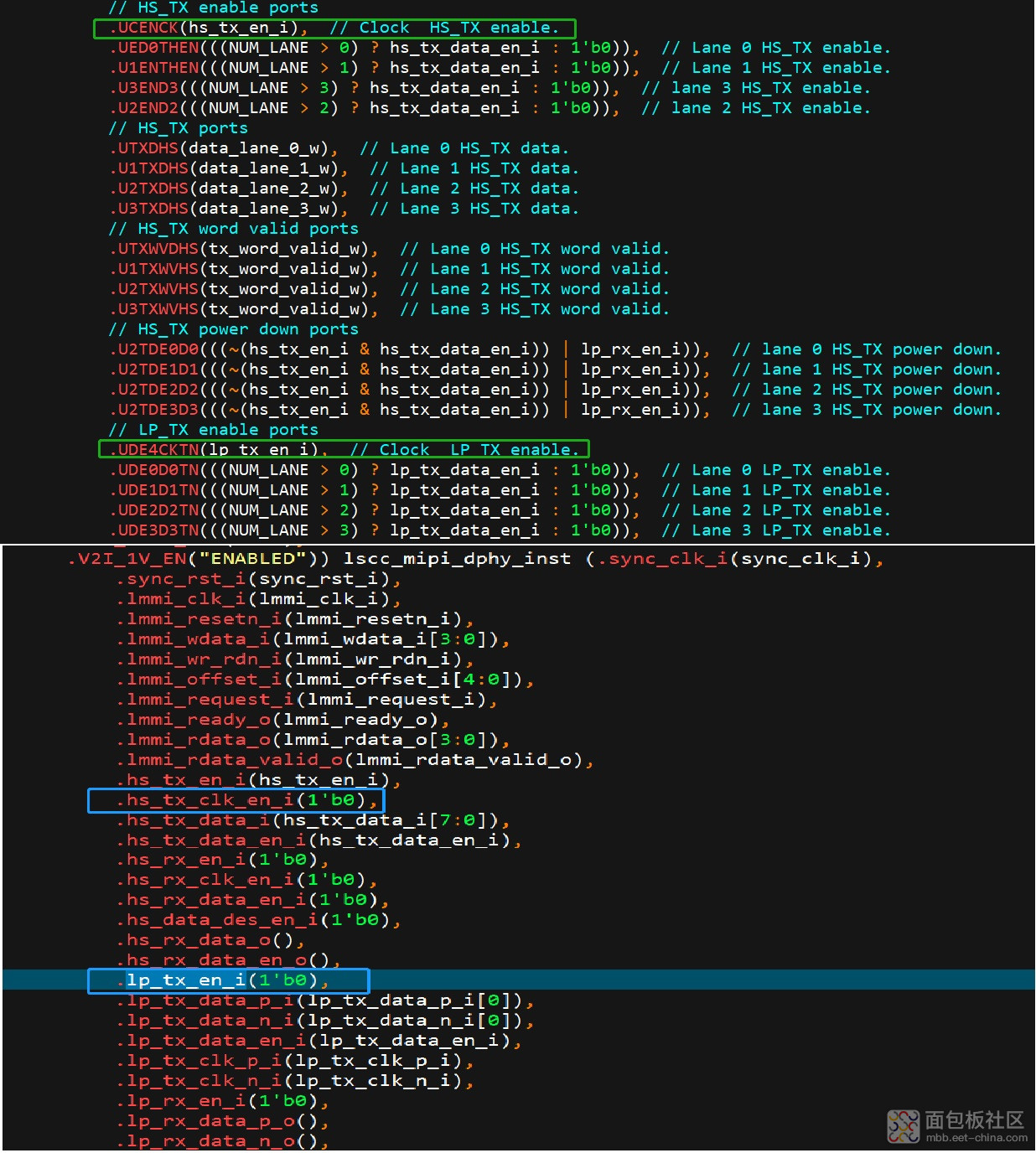

对封装的模块逐层追踪发现,DPHY原语里面,时钟HS_TX的使能信号直接接到了hs_tx_en_i,

时钟的LP_TX使能信号接到lp_tx_en_i,但是这个lp_tx_en_i在顶层例化的时候却直接赋值为“0”,这就导致在非连续时钟模式下,CLK通道无法发出LP状态信号。

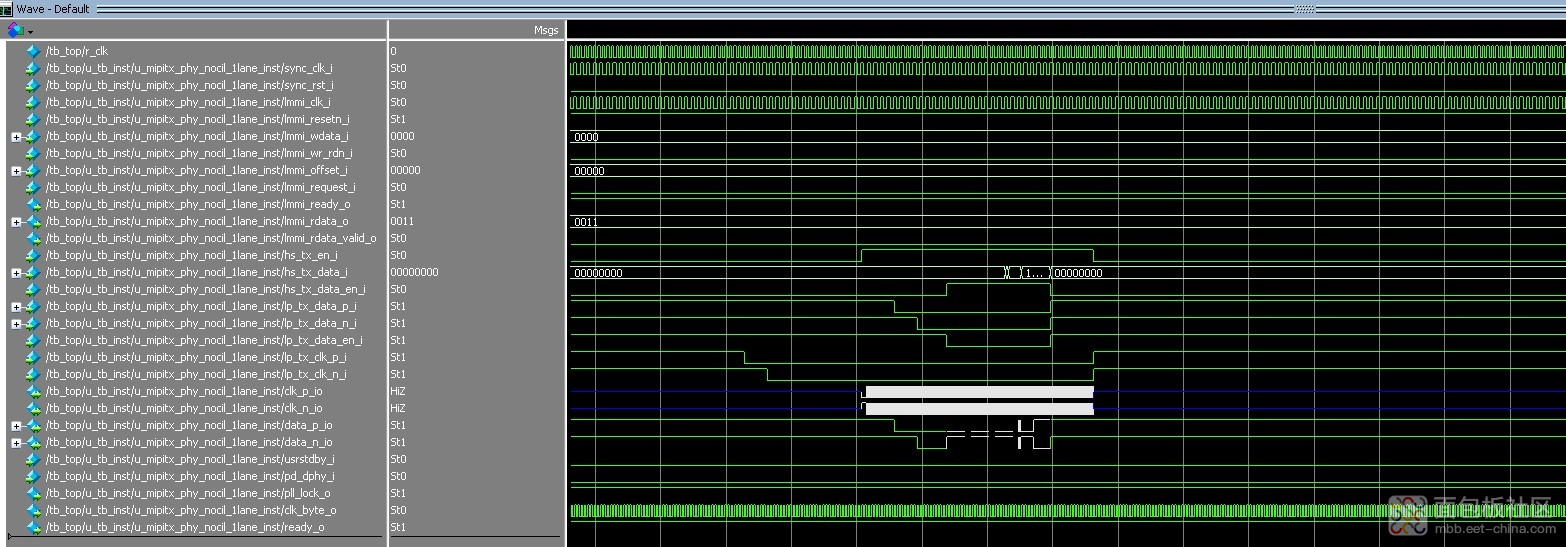

配置为非连续时钟并操控IP核引出的控制接口,实际得到的波形如下,时钟通道的LP状态为高阻,没有LP11->LP01->LP00->HS的状态变化过程:

三、解决办法

将Radiant软件自动生成的只读IP Verilog文件复制出来,重新命名,将需要的lp_tx_en_i引出给CSI层控制用于产生正确的LP信号。

hs_tx_en_i可以用来控制产生HS时钟,hs_tx_en_i和hs_tx_data_en_i相与可以使能HS数据发送。为了便于直观操作,也可以将UCENCK单独引出hs_tx_clk_en_i进行控制。

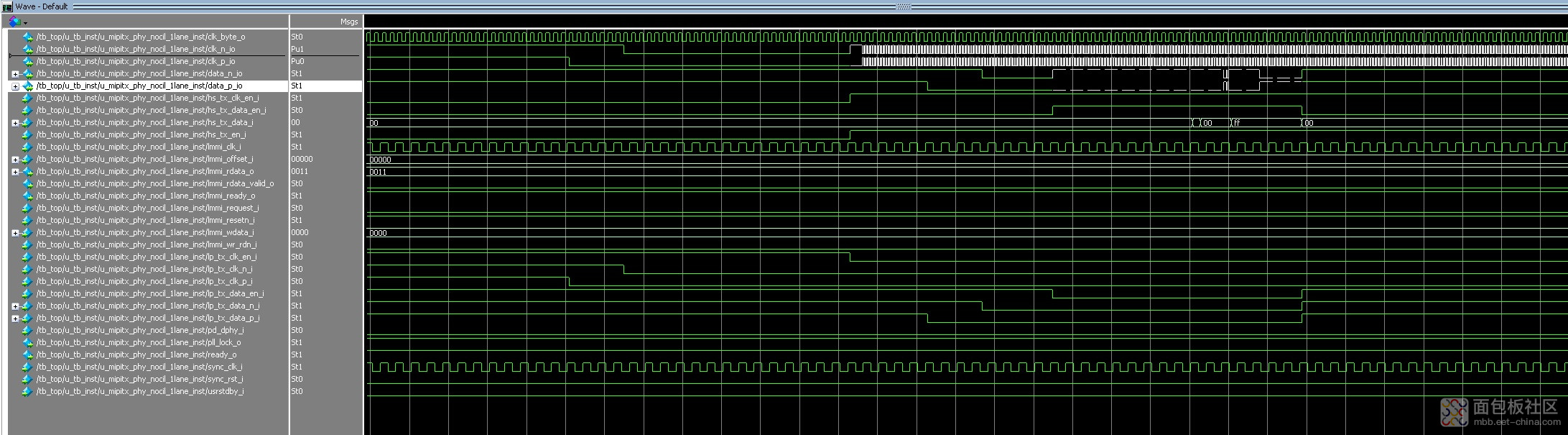

将复制并修改好的文件添加进去,写好正确的控制逻辑,并删除掉IP生成的文件,可以得到如下图所示的正确时序。

作者: panda君, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3403128.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

panda君 2022-10-20 16:43