一、案例需求

使用LIFCL-40 FPGA的MIPI DSI硬核接口驱动7寸LCD显示器:

(1) 显示器:7寸,1024*600横屏,60Hz;

(2) MIPI物理层:4-Lane,600Mbps/lane(最大可支持3840*2160分辨率30Hz,1920*1200分辨率120Hz,最大支持2.5Gbps/lane速率);

(3) DSI:支持突发模式,24-bpp RGB数据;

(4) 代码:全手写,不使用Lattice官方IP核。

二、硬件电路

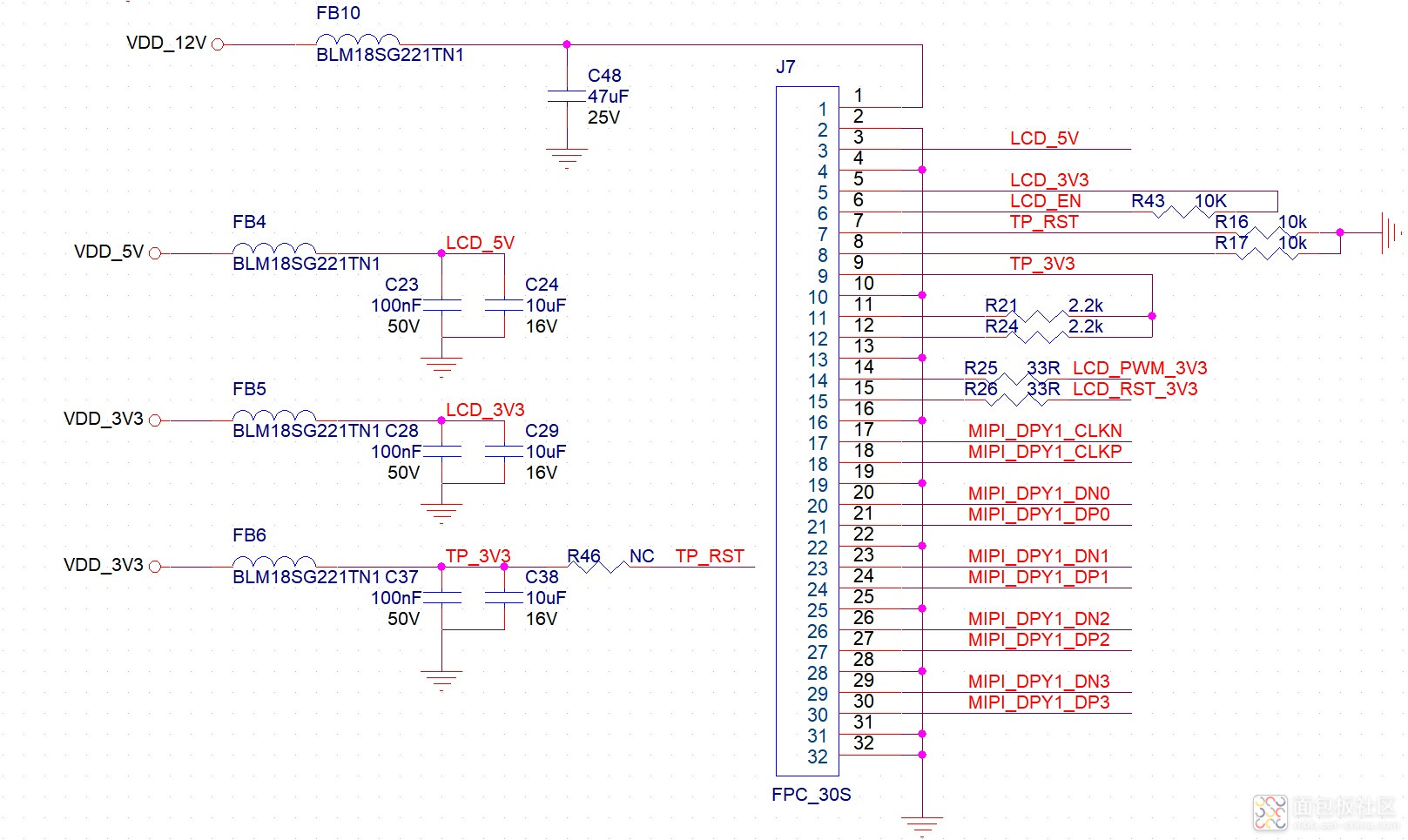

采用LIFCL-40基础视觉开发平台,由FPGA产生本地测试图像,接口电路见下图1所示。

图1 MIPI DSI LCD驱动接口

如上图所示,MIPI DSI数据通道为4-lane MIPI D-PHY,LCD_RST_3V3为LCD复位信号,低电平复位;LCD_PWM_3V3为背光驱动信号,10~20KHz PWM信号。

三、 软件设计

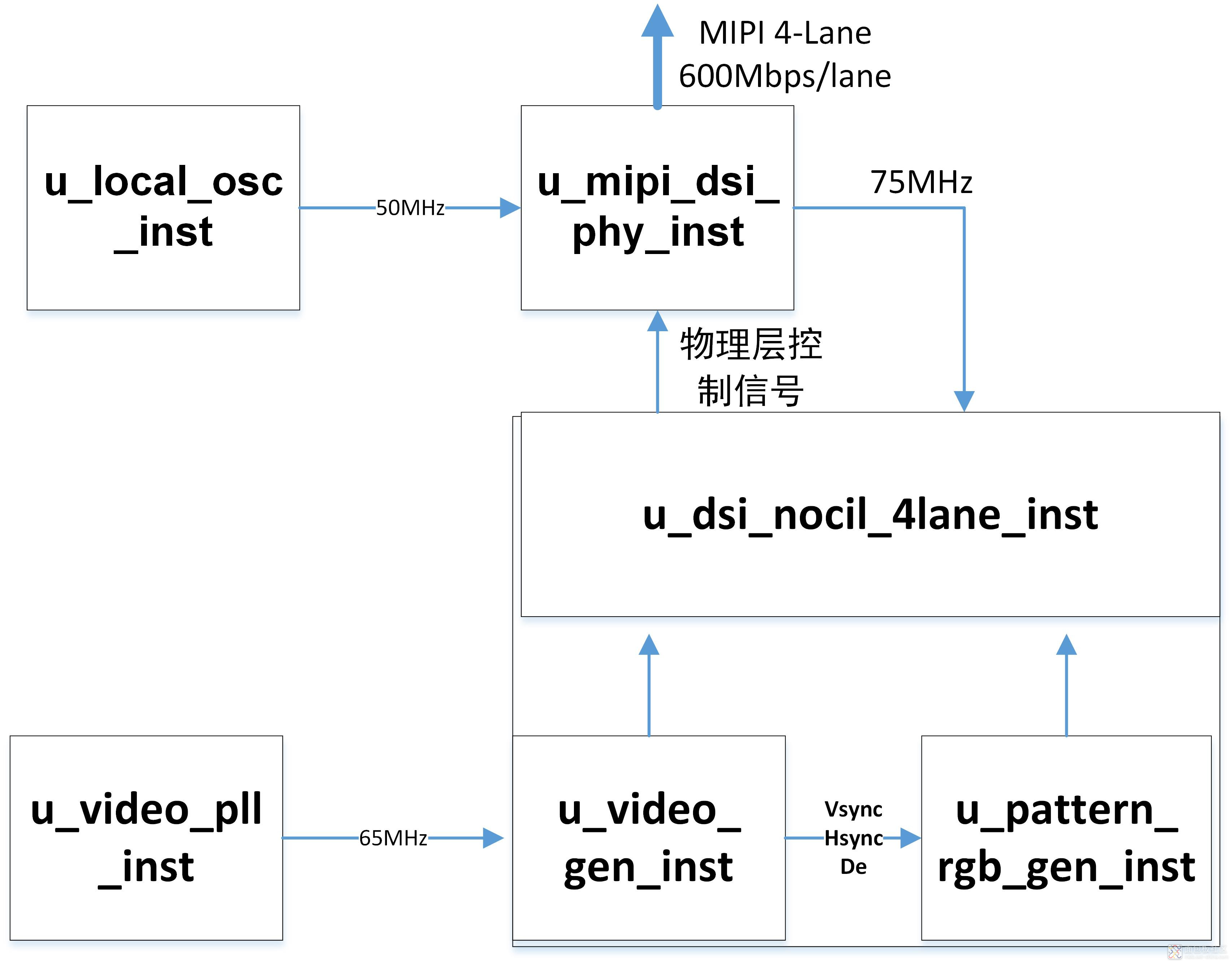

软件使用Radiant3.2开发,软件的整体结构如下图2所示。

图2 驱动LCD软件结构

(1) 片上晶振产生50MHz时钟给MIPI D-PHY物理层内部的PLL产生300MHz的源同步时钟和75MHz的字节时钟;

(2) 核心板外部50MHz产生65MHz视频时钟,用于产生1024*600 60Hz的视频时序和产生测试数据;

(3) 产生的数据经FIFO后给u_dsi_nocil_4lane_inst模块发送到MIPI物理层模块u_mipi_dsi_phy_inst进行串行化发出;

(4) DSI模块u_dsi_nocil_4lane_inst用于产生符合MIPI D-PHY物理层规范的长短包发送时序。

在开机后,延时200ms以上等待LCD显示屏初始化完毕后再发送Turn On Peripheral Command和Color Mode Off Command短包命令打开设备并进入正常显示模式。

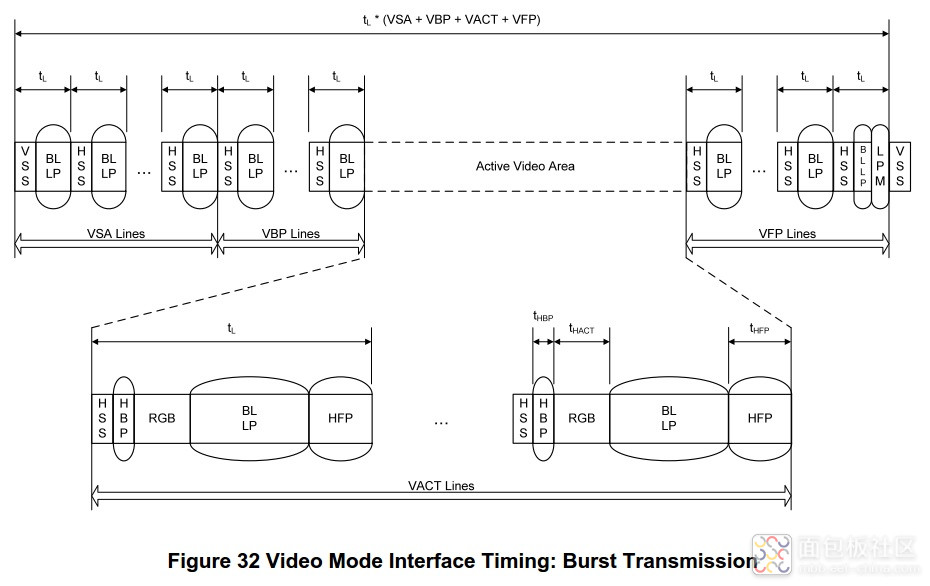

MIPI DSI数据发送模式选择为Burst Mode,如下图3所示。一帧发送一个VSS(帧起始)短帧,其他行发送HSS(行)起始短包,显示数据区域(VACT)行发送实际的RGB-24bpp打包的像素长包数据,其他区域VSA、VBP、VFP区域发送Blanking数据。

图3 Burst模式时序图

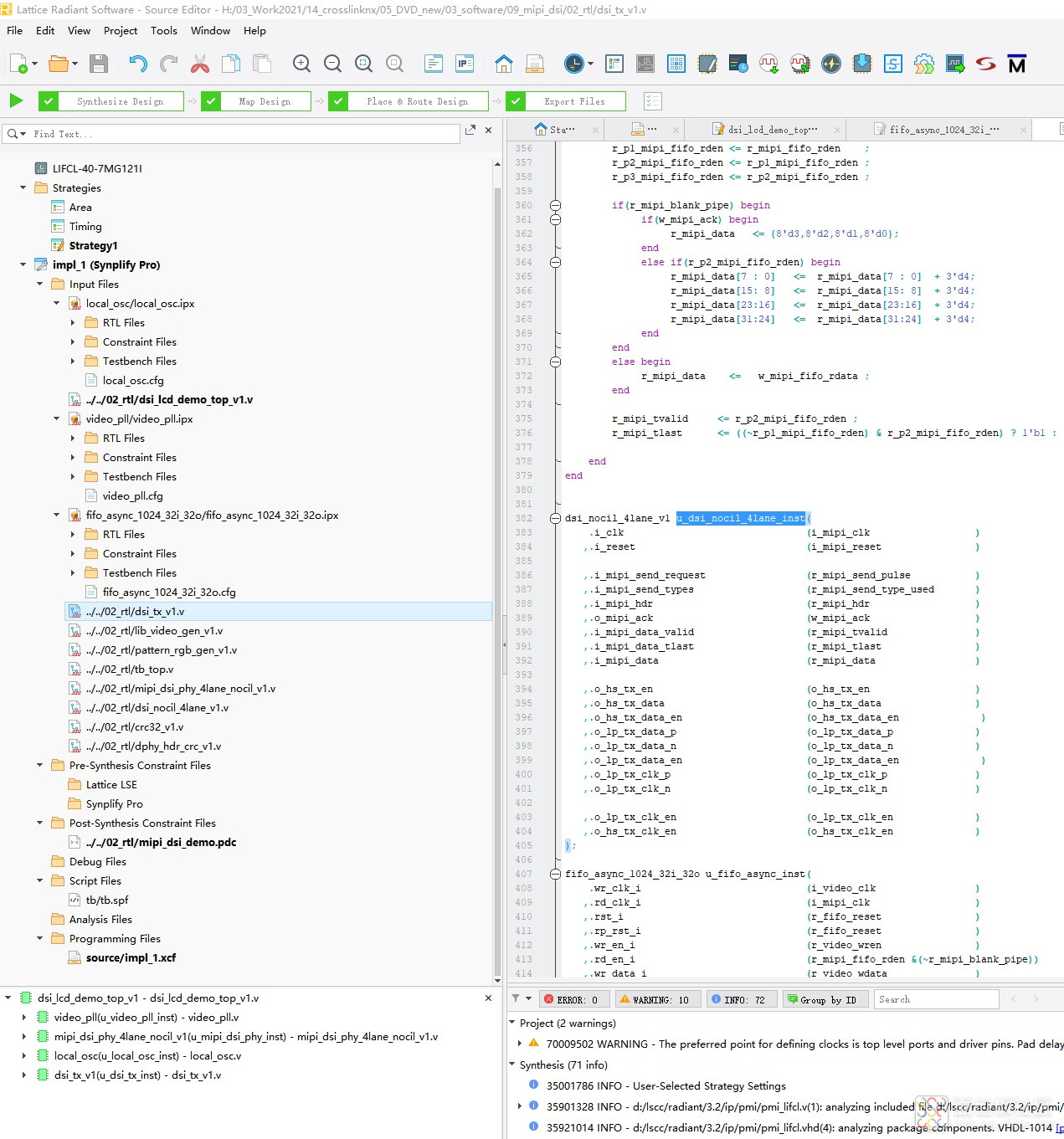

整个工程的代码结构见下图4所示:

图4 工程代码结构

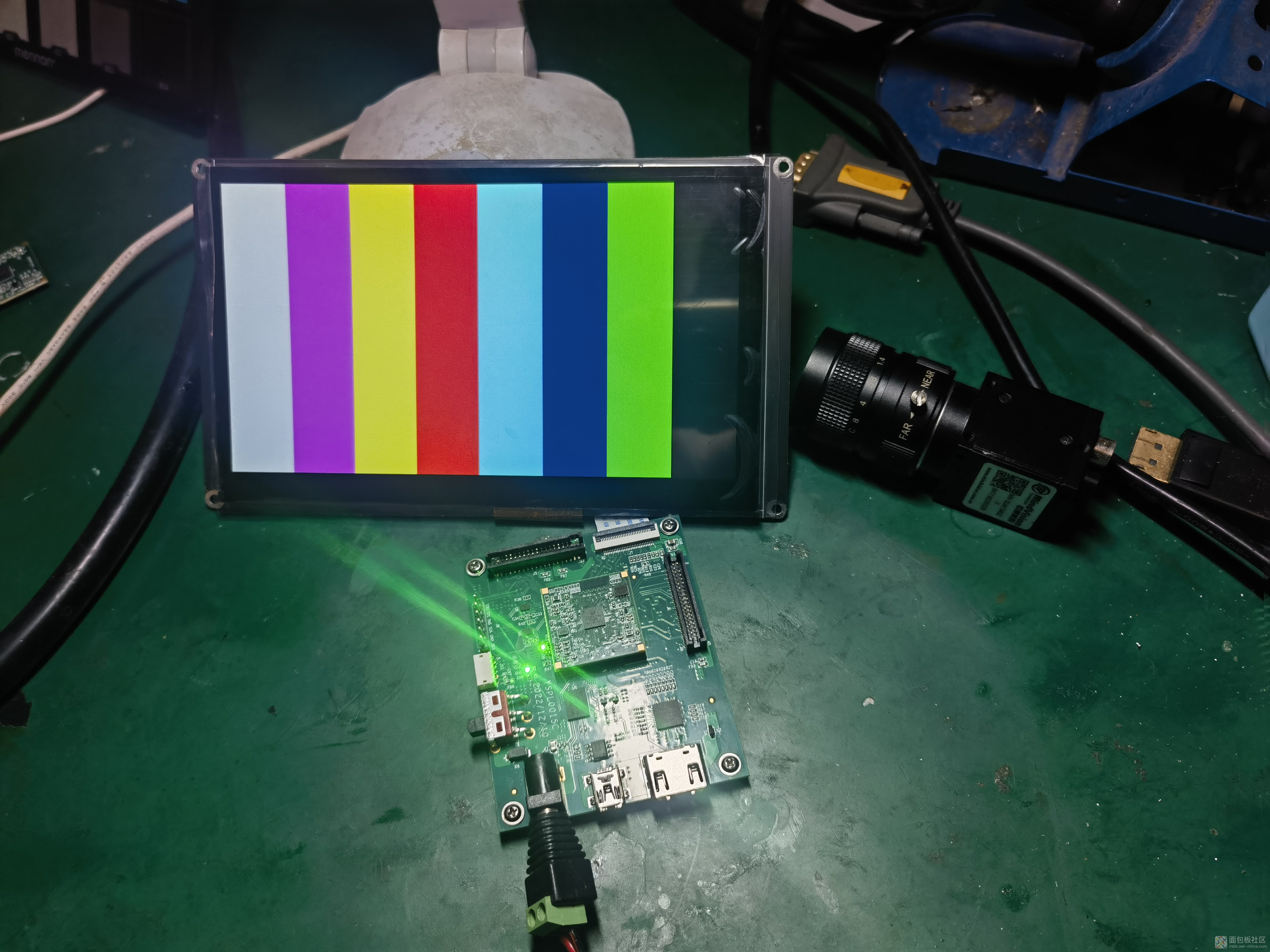

四、 显示效果

如下图所示,将显示器的软排线连接到板子的J7连接器,将bit文件烧入flash,重新上电显示效果见下图5:

图5 显示效果图

作者: panda君, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3403128.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

文章评论(0条评论)

登录后参与讨论