Lattice系列工具使用在线调试器的方法比Xilinx要复杂,和Altera的类似,但还是要稍微复杂一些。本例在上一个产生50Hz方波的工程基础上进行说明。

3.1添加Logic Analyzer核首先,需要将工程布局布线通过生成网表。

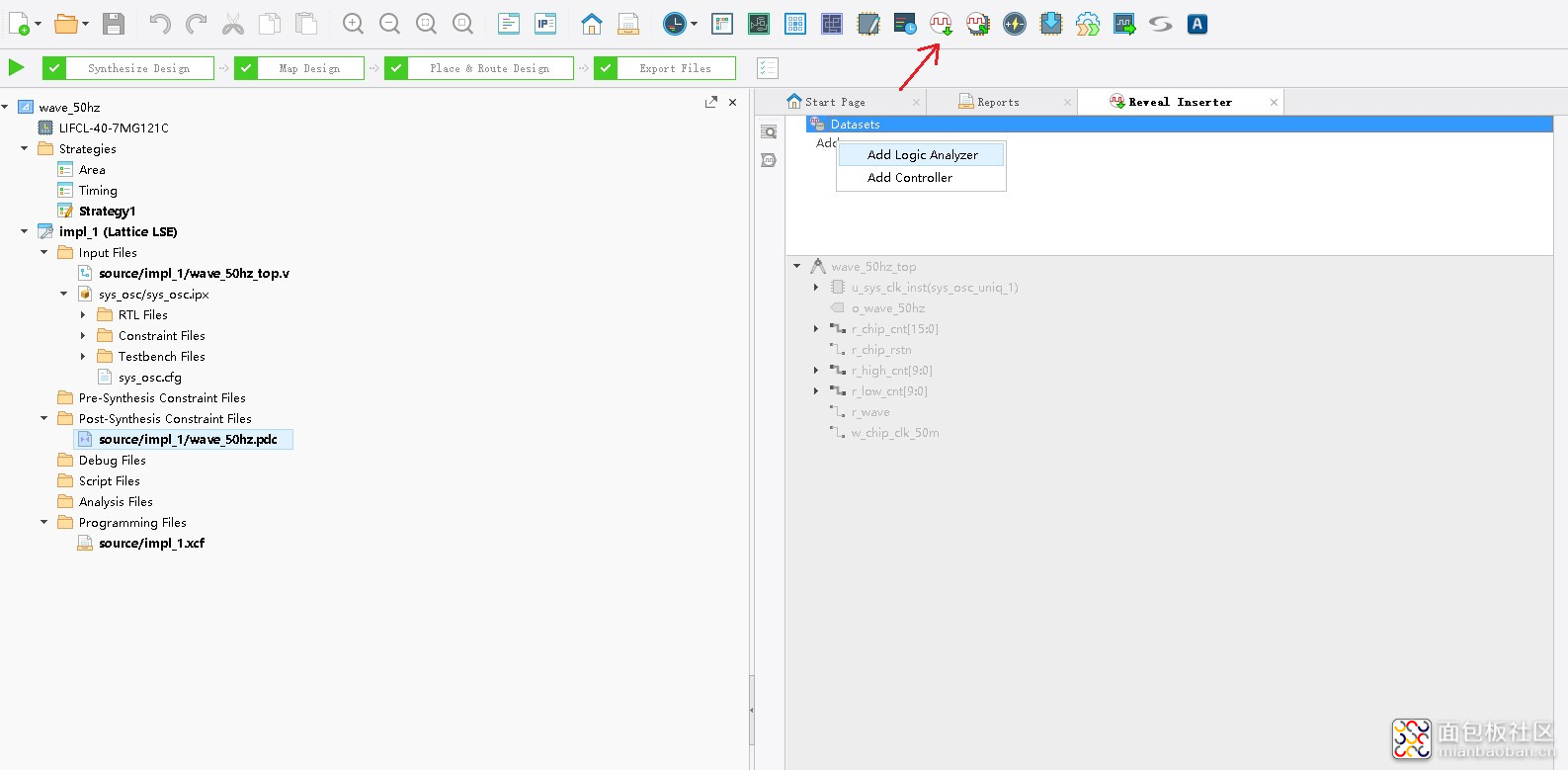

Step1:点击Tools ->Reveal Inserter按钮或点击快捷按钮,选择Add Logic Analyzer。

图1 选择逻辑分析仪

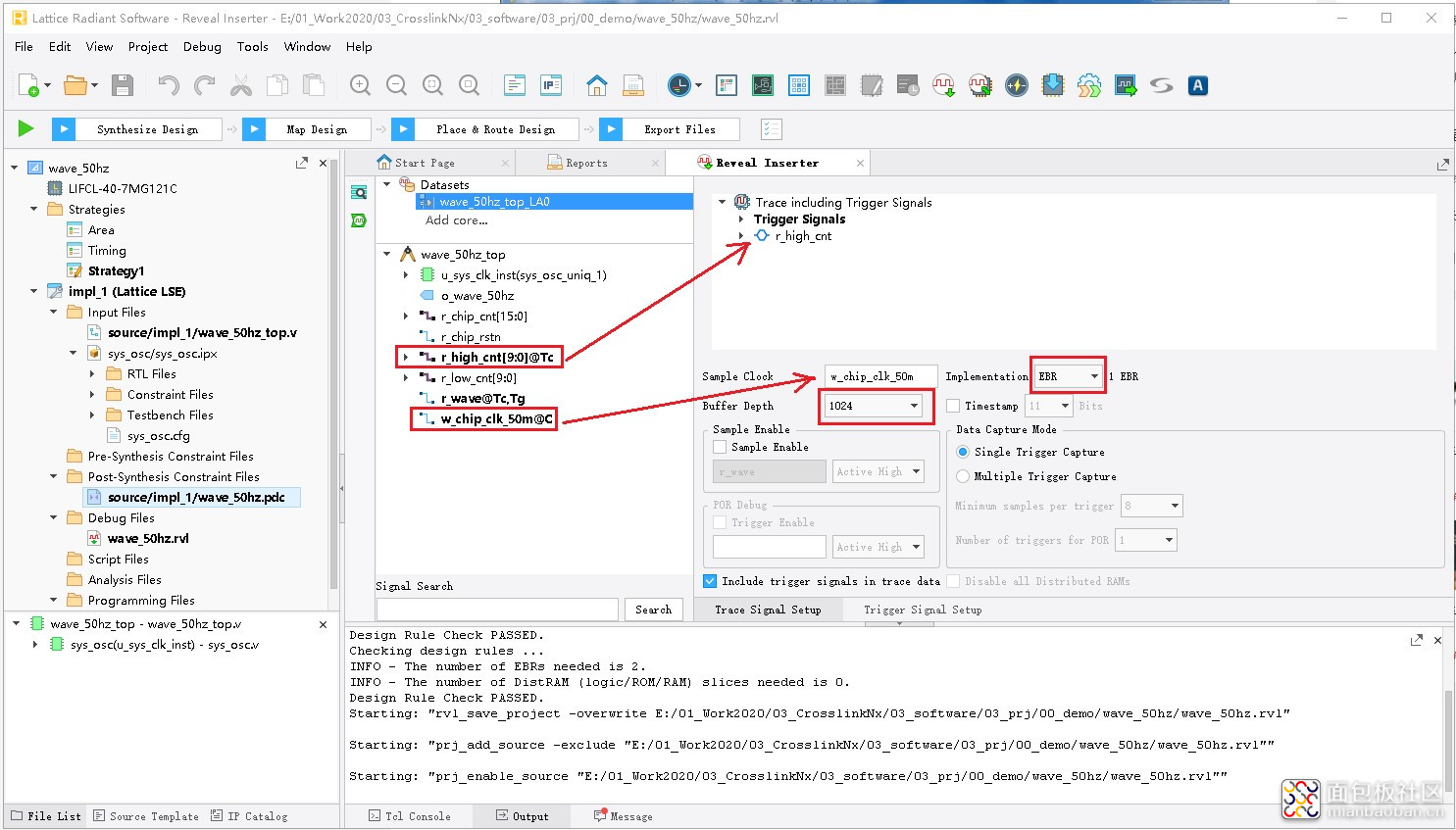

Step2:添加采样时钟、采样深度、待观测信号等。如下图所示,将左边的时钟信号拖到sample clock位置,将需要观测的信号拖到Trace下的空白处。配置采样深度为1024和实现的资源为EBR。

图2 配置Trace Signal

Step3:配置触发信号、触发条件等

如下图所示,将触发信号添加到Tigger Unit单元下并设置触发条件,然后进行“规则检查”,规则检查无误后点击“添加到工程”按钮并保持工程。

图3 配置触发信号、触发条件等界面

Step3:生成新的bit文件。

Step4:将新生成的bit文件下载到FPGA。

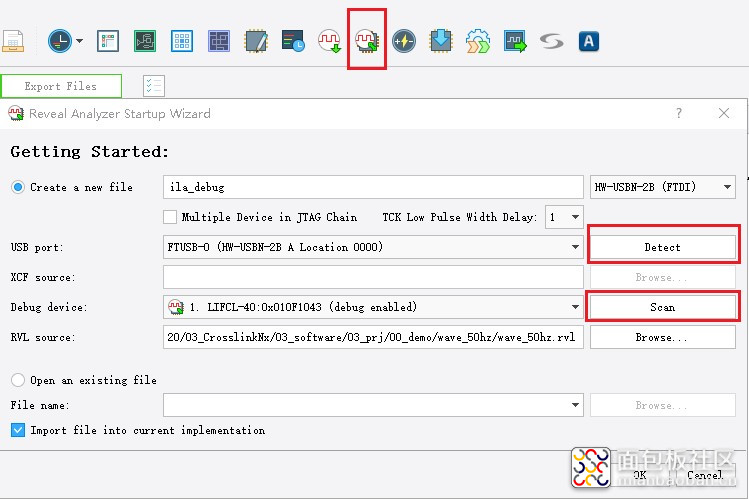

1.2 在线调试将包含Logic Analyzer的bit文件下载到FPGA以后,选择Toos-> Reveal Analyzer/Controller或者点击快捷按钮,按下图红框处所列找到USB Port和Debug Device,点击OK确认。

图4 启用Analyzer/Controller

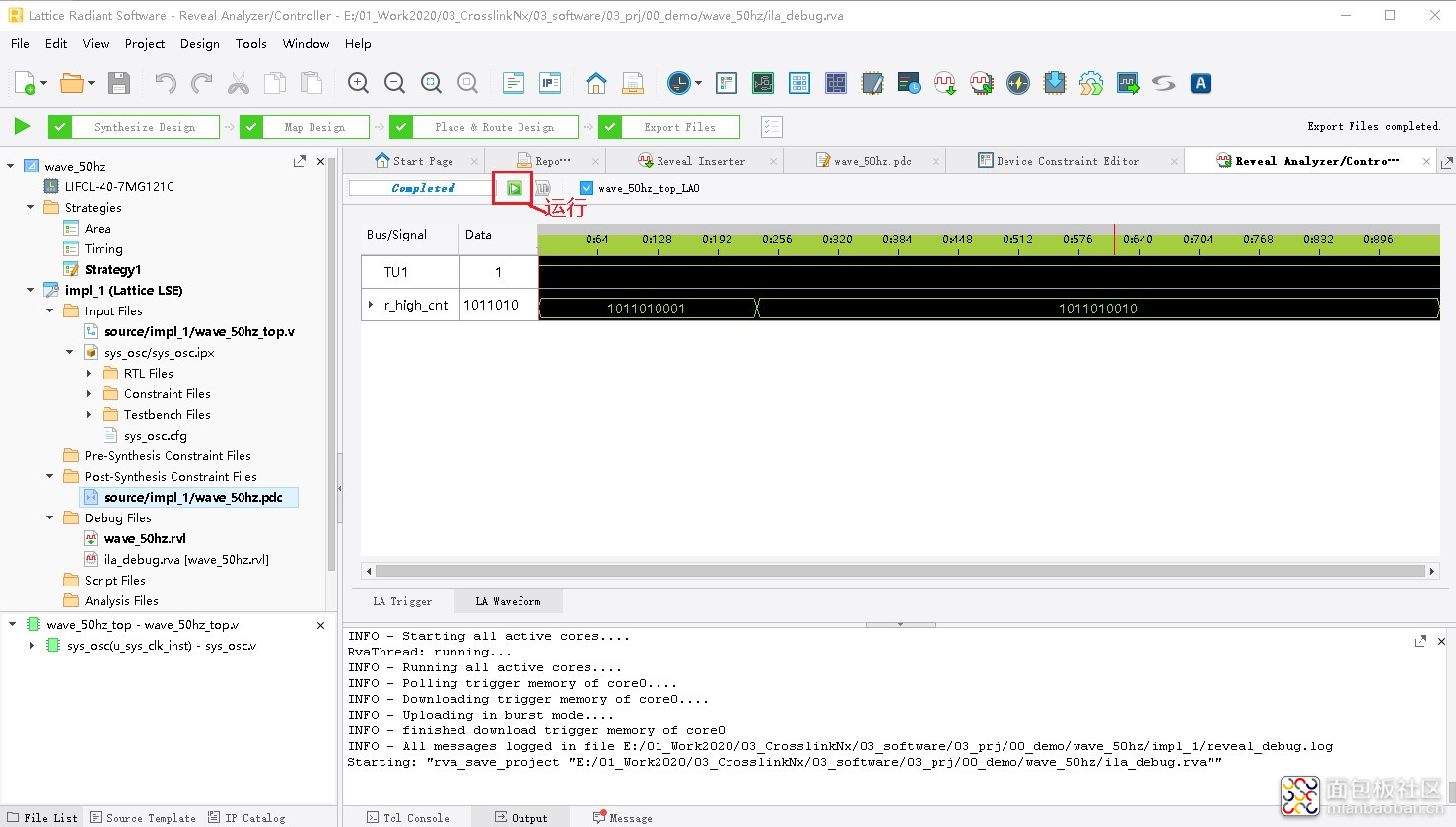

如下图所示,点击运行按钮,点击“run”运行按钮,等待触发完成即可看到如图所示的波形,可以根据自己的需要鼠标右击波形根据选项调整波形的显示格式属性。

图5 触发显示波形

作者: panda君, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3403128.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

curton 2021-1-16 14:47

欢迎点击

论坛> >机器人/工业电子> >工业电子与自动化

https://mbb.eet-china.com/forum/topic/85437_1_1.html