Lattice CrosslinkNX内部集成了RISC-V指令集,可以支持RISC-V软核处理器,因此能够进行SoC的开发。RISC-V软核可以运行C程序,实现一些控制、调度以及接口驱动的功能,相比纯FPGA而言更加的方便,特别是在图像采集、处理应用上,可以很便捷的配置CMOS、运行一些ISP的如自动曝光、自动白平衡的控制代码。

4.1创建SoC工程Lattice提供了SoC开发环境Propel,其中Propel Builder用于搭建硬件工程,Propel用于开发RISC-V的C代码。本例创建一个示例工程,包括RSIC-V软核及其运行必须的RAM和定时器、中断,一个GPIO外设和一个UART外设。

Step1:新建工程

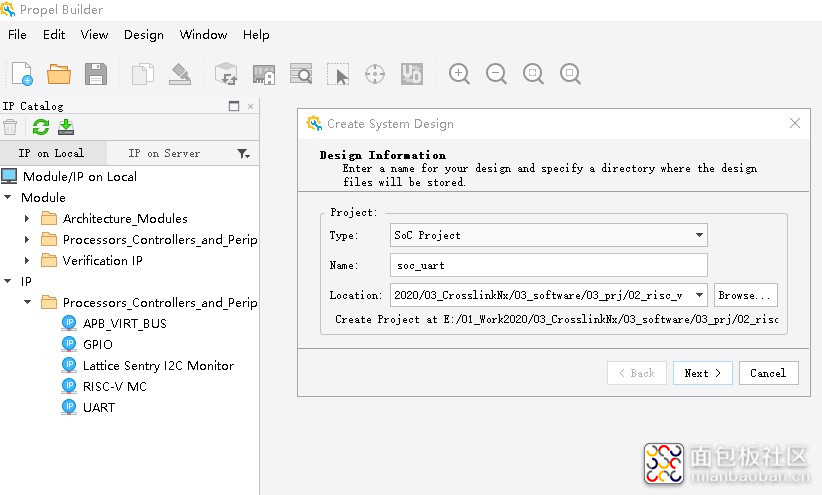

打开Propel,选择File->New Design,将工程命名为soc_uart,并指定好保存路径。

图1 新建SoC工程

Step2:配置工程

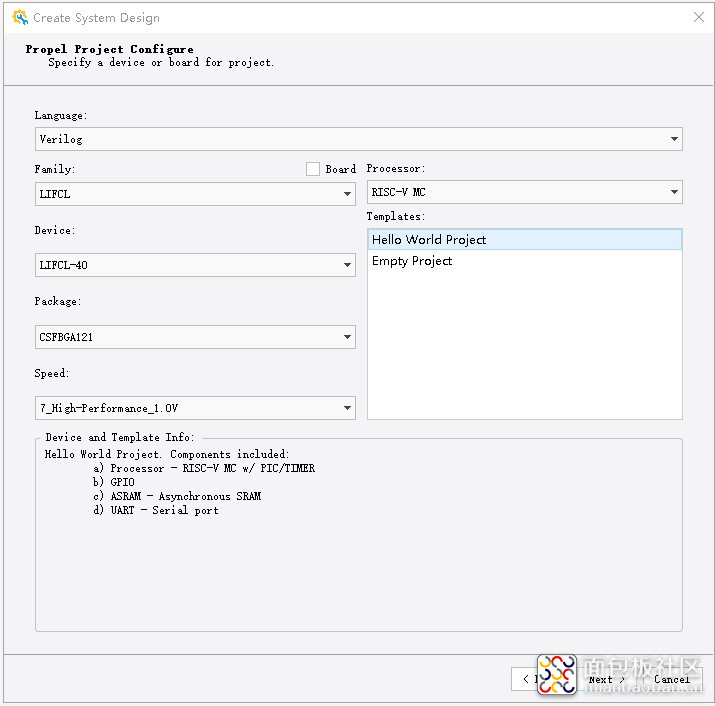

如下图所示,选择器件为LIFCL-40,处理器类型为RISC-V MC,为了快速实现,选择“Hello World Project”工程模板,这里面包含了最小工程所必须的配置和外设。

图2 配置工程

Step3:配置其他模块

工程默认时钟频率为112.5MHz(450MHZ OSC四分频),实际布局布线能跑80MHz左右,因此按照前篇所述方法将OSC的输出频率改为最接近的75MHz。

同时,双击原理图中的uart模块,将输入时钟改为75MHz,以准确产生115200的波特率。

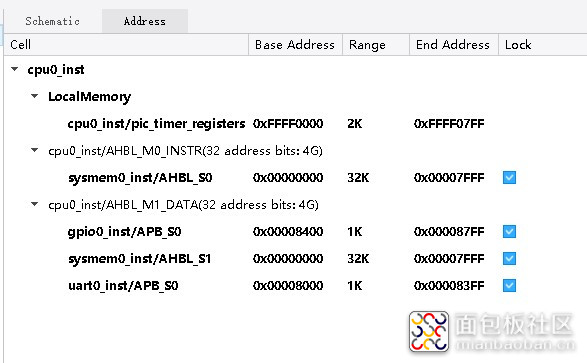

Step4:确认地址空间

点击原理图左上角的Address选项,如果地址没有冲突,则将地址lock项打√,如下图所示。

图3 检查地址是否有冲突

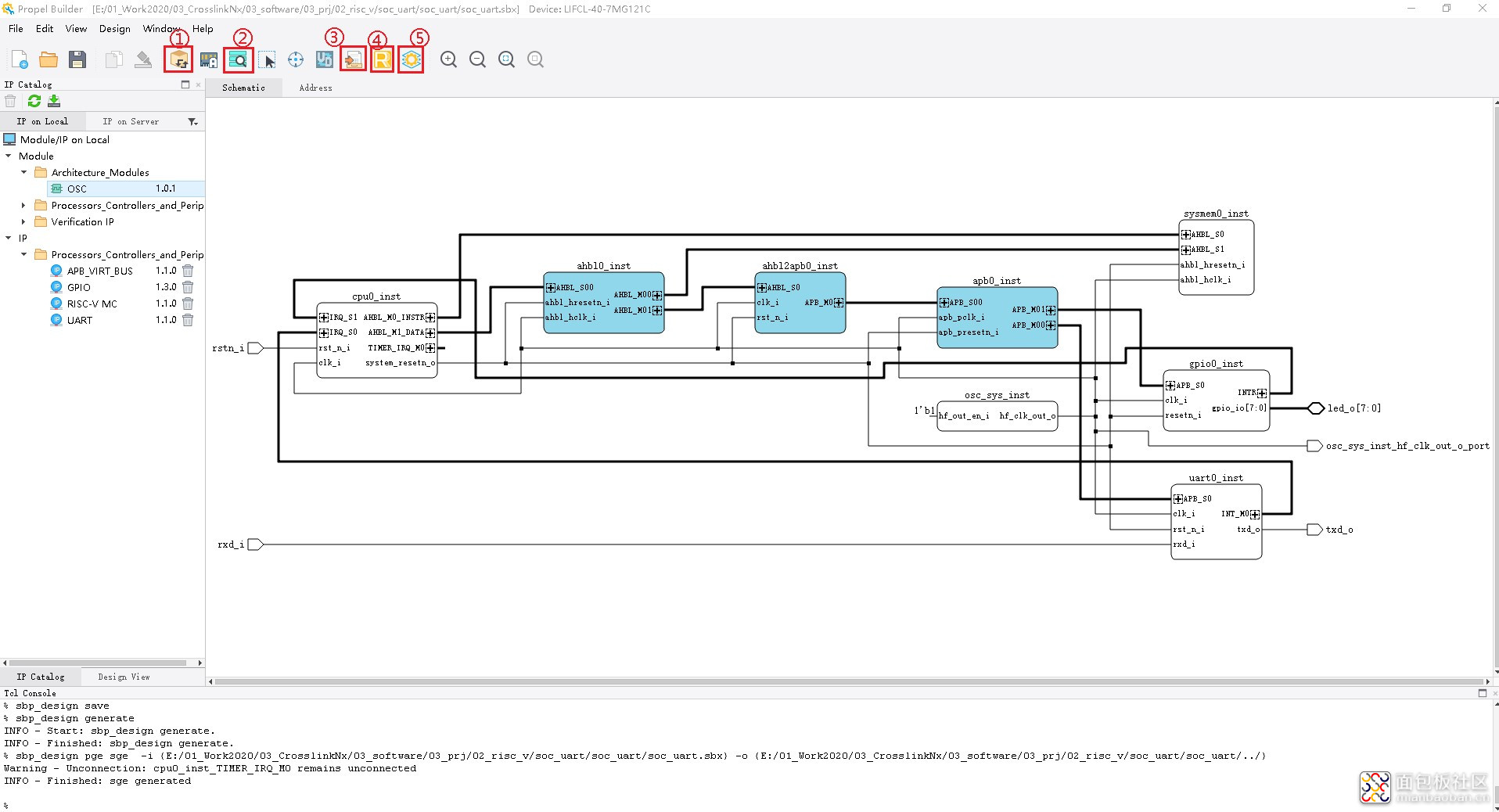

Step5:规则检查和生成文件

如下图所示,标号①所在图标为生成文件,标号②所在图标为规则检查,标号③所在图标为生成地址报告(包含外设的寄存器地址和定义),标号④为调用Radiant,标号⑤为调用Propel SDK。

在规则检查无误后点击Generate生成输出文件,然后调用Radiant对工程进行综合和布局布线。

图4 图形化工程界面

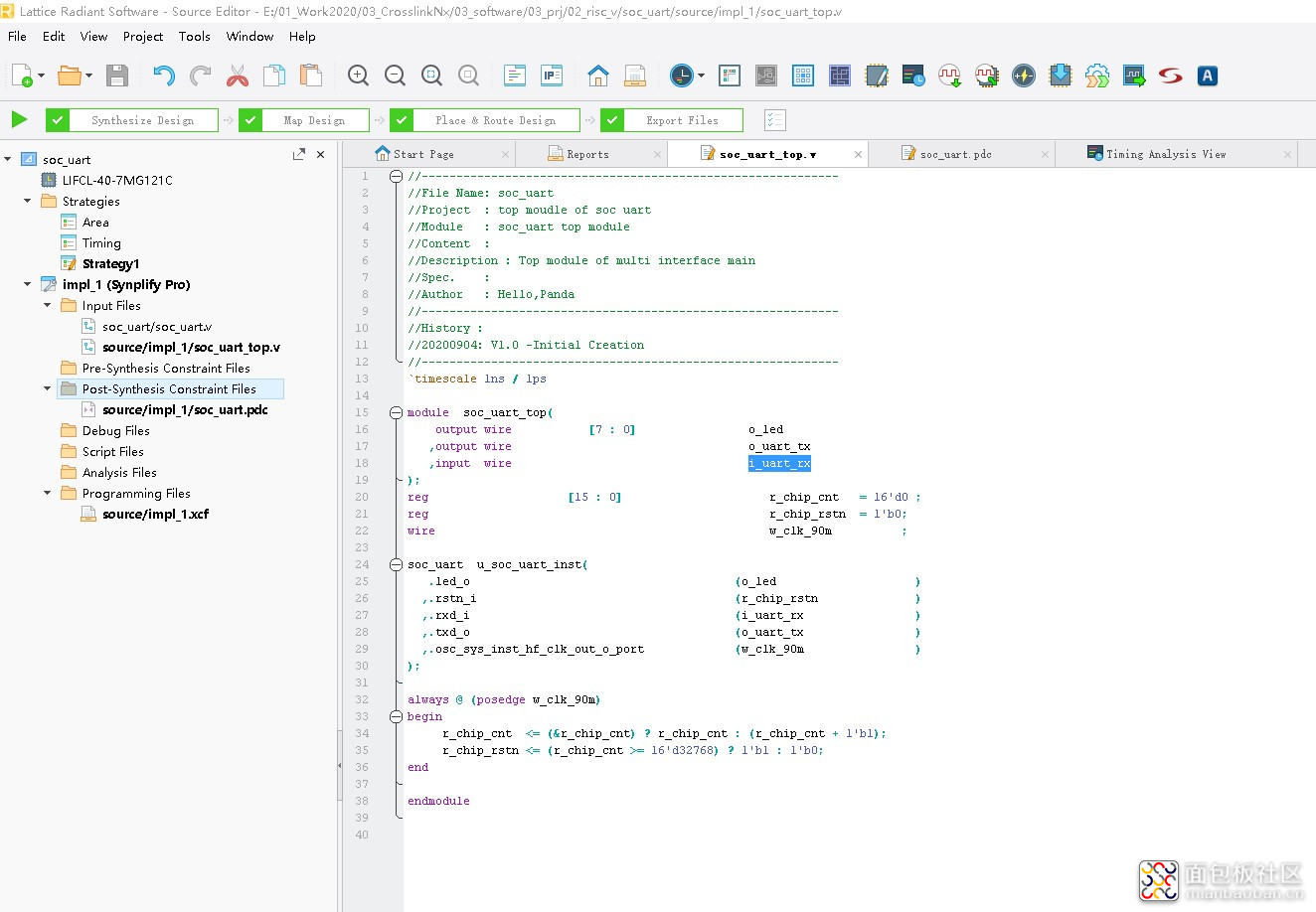

Step6:Radiant编译

点击图4所示的标号④按钮进入Radiant集成开发环境,按照前偏介绍的方法编写顶层文件调用生成的SoC工程,编写pdc约束文件,一切准备好后Export Files生成bit文件。

图5 Radiant工程

将bit文件下载到FPGA即可进行RISC-V软核C代码调试。

4.2 RISC-V软核调试RISC-V 软核C代码调试在Propel SDK下进行,具有单步Debug、查看内存数据等功能。

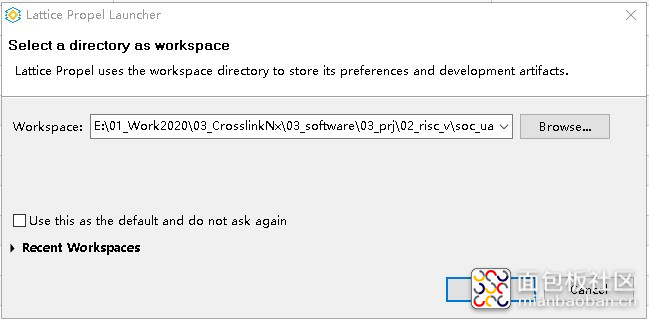

Step1:分配工作区

点击图4所示标号⑤图标按钮,给Propel软核分配一个工作空间。

图6 分配工作区

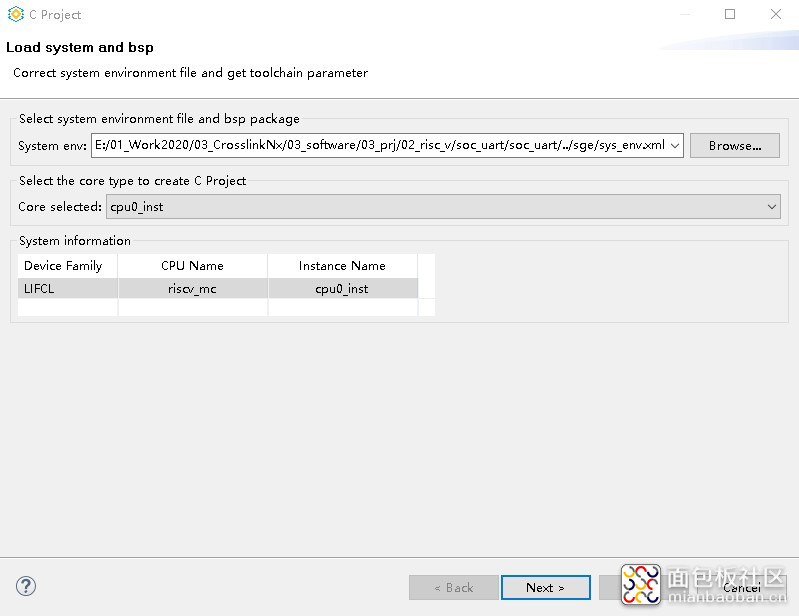

Step2:配置系统环境

内存分配、外设等相关信息均包含在sys_env.xml文件中,选择先前工程生成的该文件以及目标CPU,点击NEXT。

图7 配置系统环境

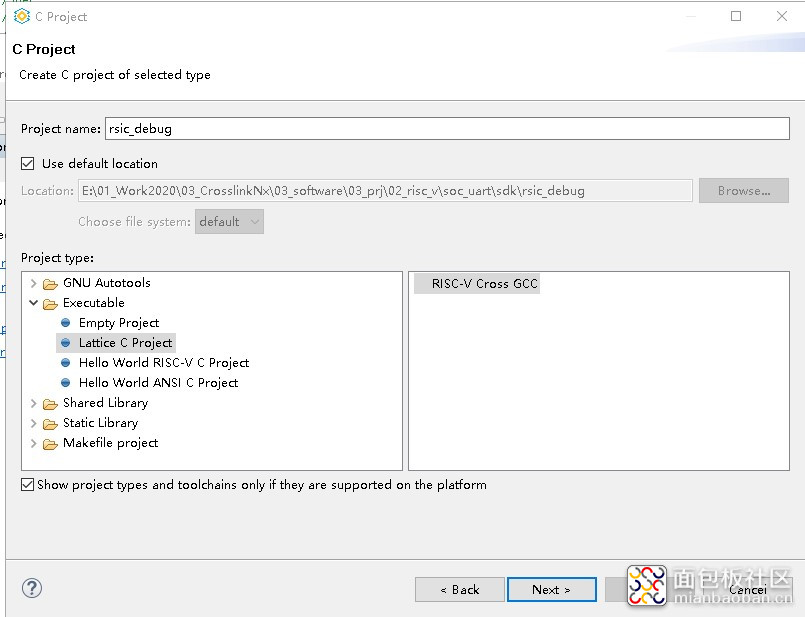

Step3:配置工程类型

如下图所示,给工程命名,并配置工程类型为“Lattice C Project”,然后一路Next创建好工程。

图8 设置工程类型

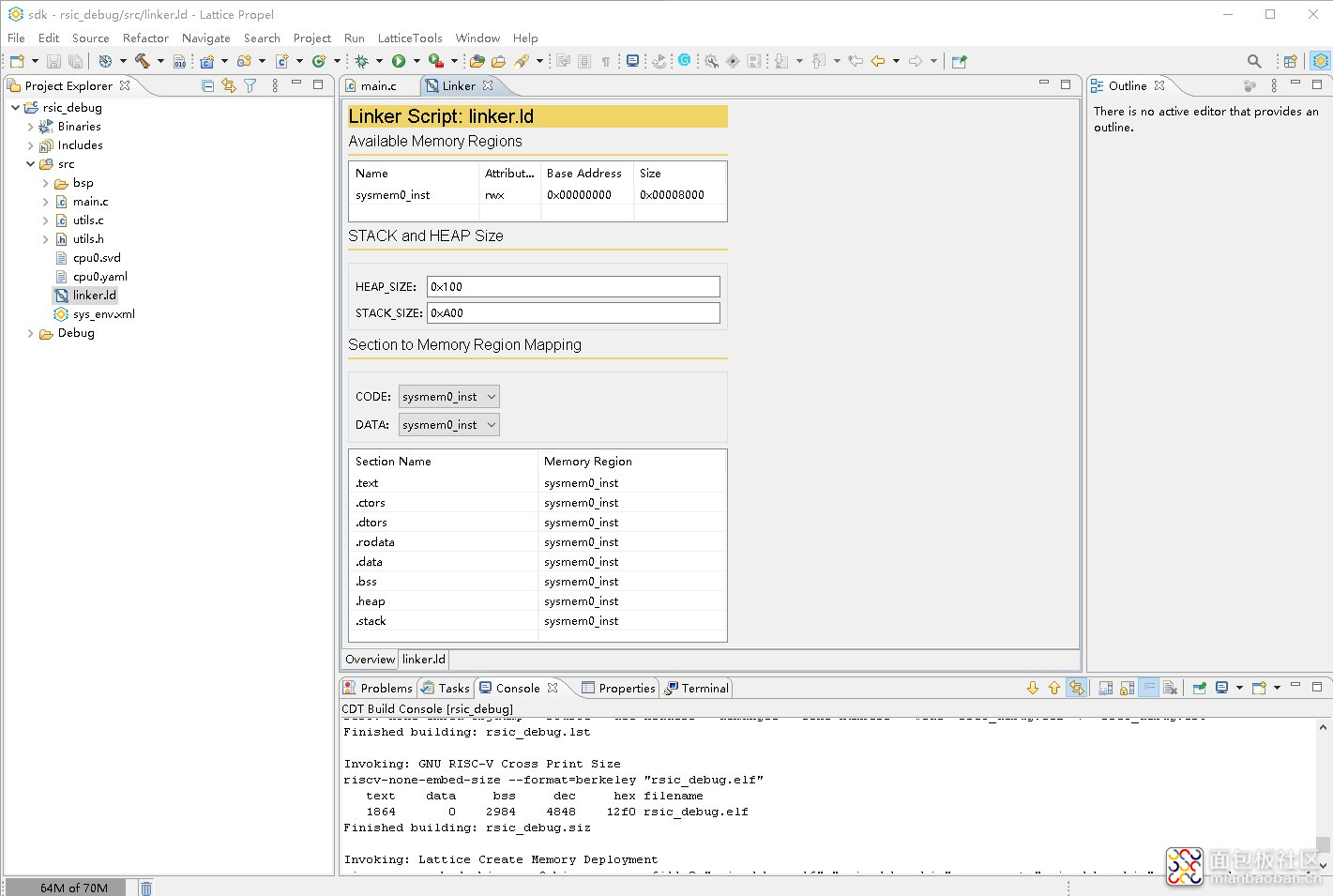

Step4:修改链接脚本

可根据系统的资源来修改链接脚本,本例中代码区和数据区在同一处SRAM,因此默认就行,仅将堆栈区做修改。

图9 修改链接脚本

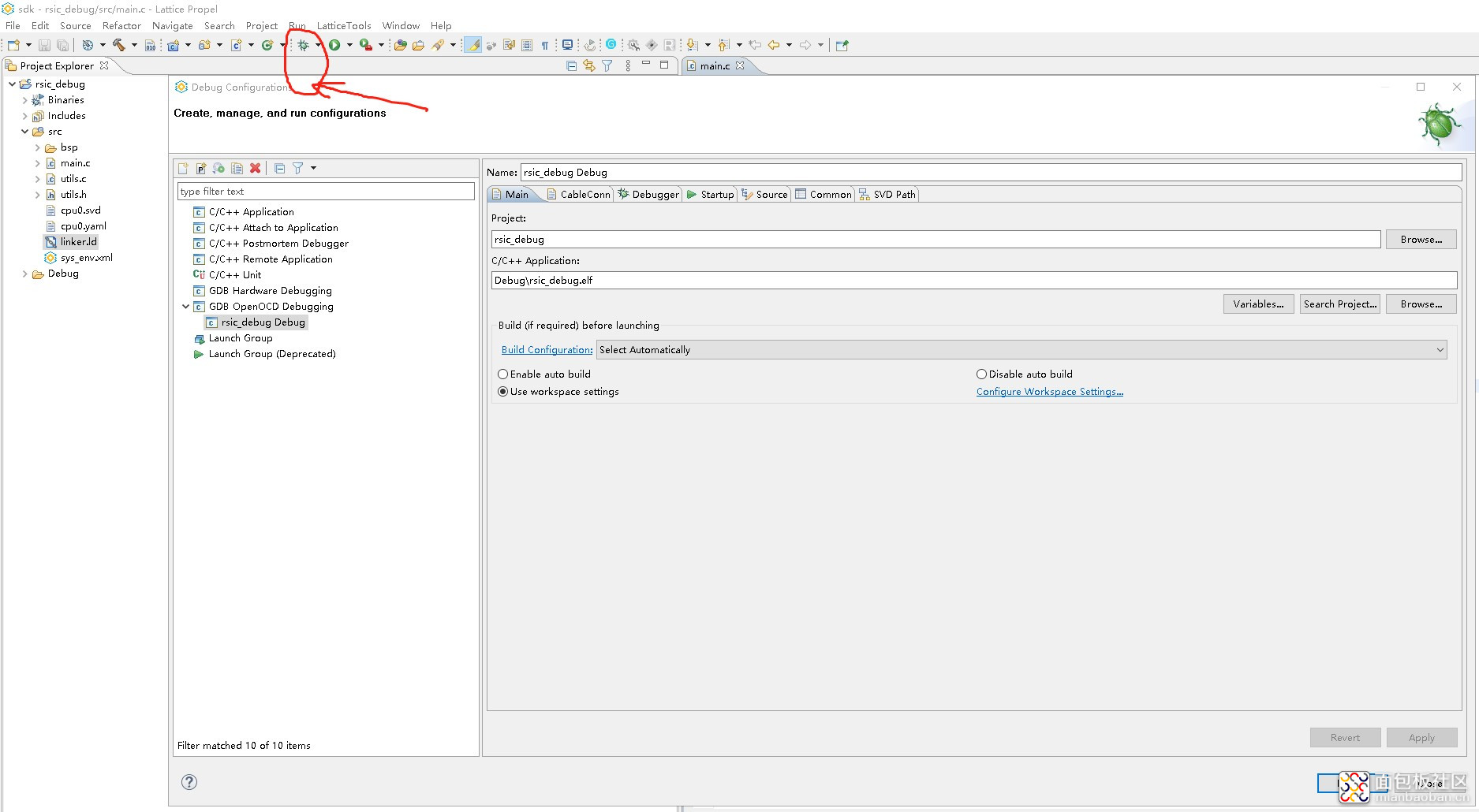

Step5:配置Debug选项

如下图10,选中画圈的虫子,选择Debug Configurations,选择GDB OpenOCD Debugging,取好名字。

图10 配置Debug选项

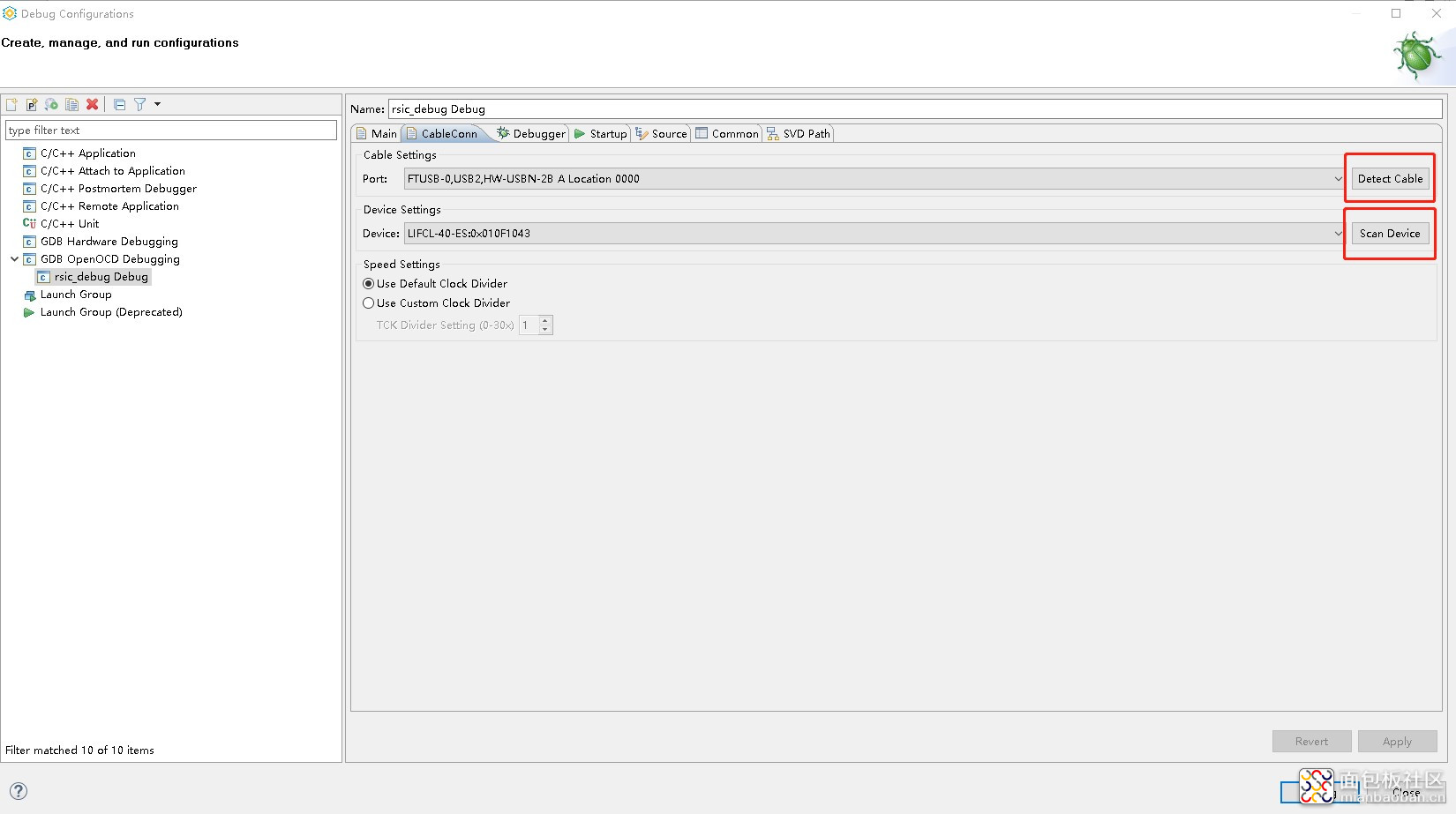

Step6:扫描器件

在线调试之前一定要先将bit文件下载到FPGA,然后在GDB OpenOCD Debugging的CableConn下,侦测Cable和扫描器件,如下图所示,找到器件后点击Apply,如无特殊需求,其他的配置项可以不修改,点击Debug进入在线仿真。

图11 扫描器件

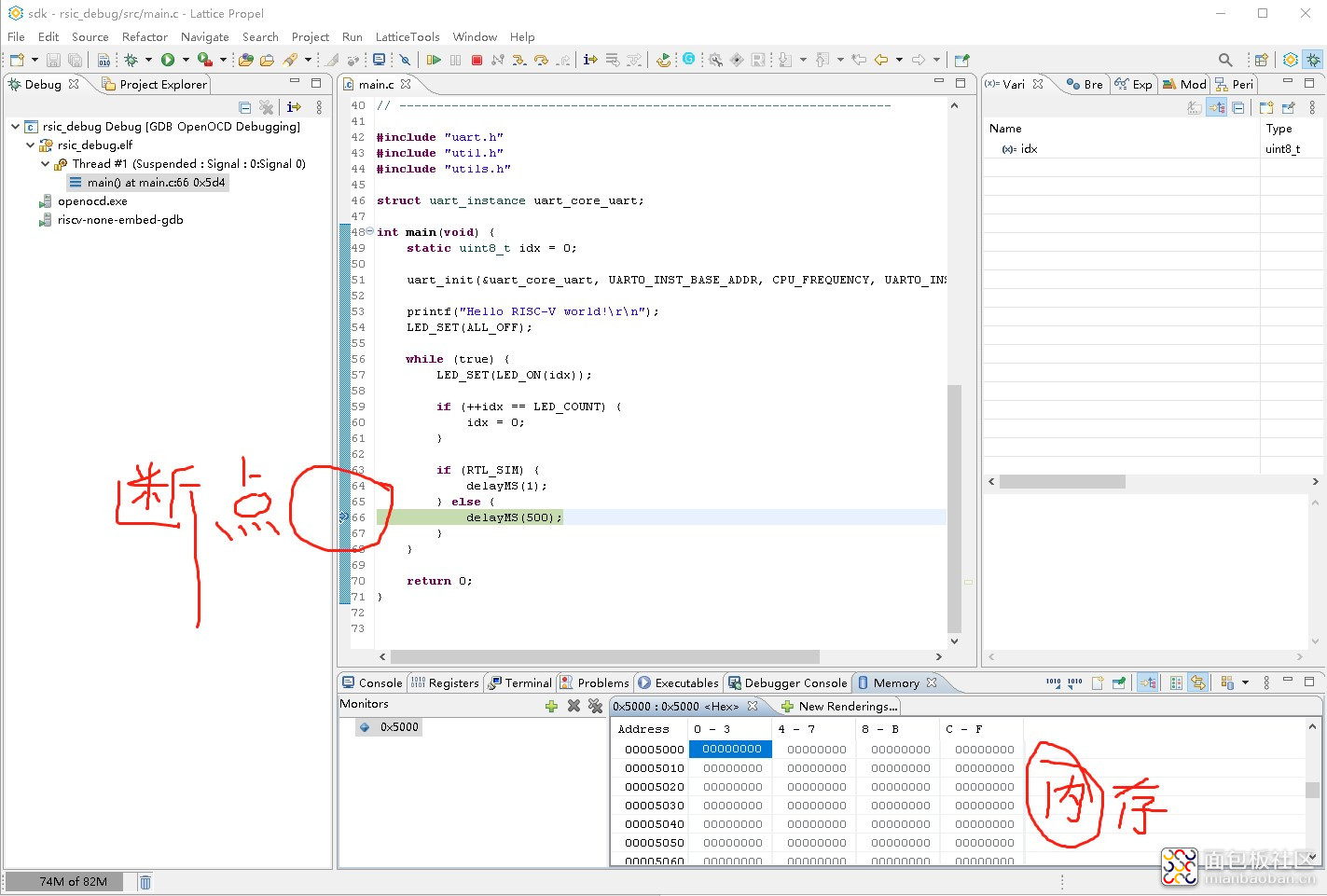

连接设备进行入Debug后,可设置断点、查看内存值等。

图12 在线调试界面

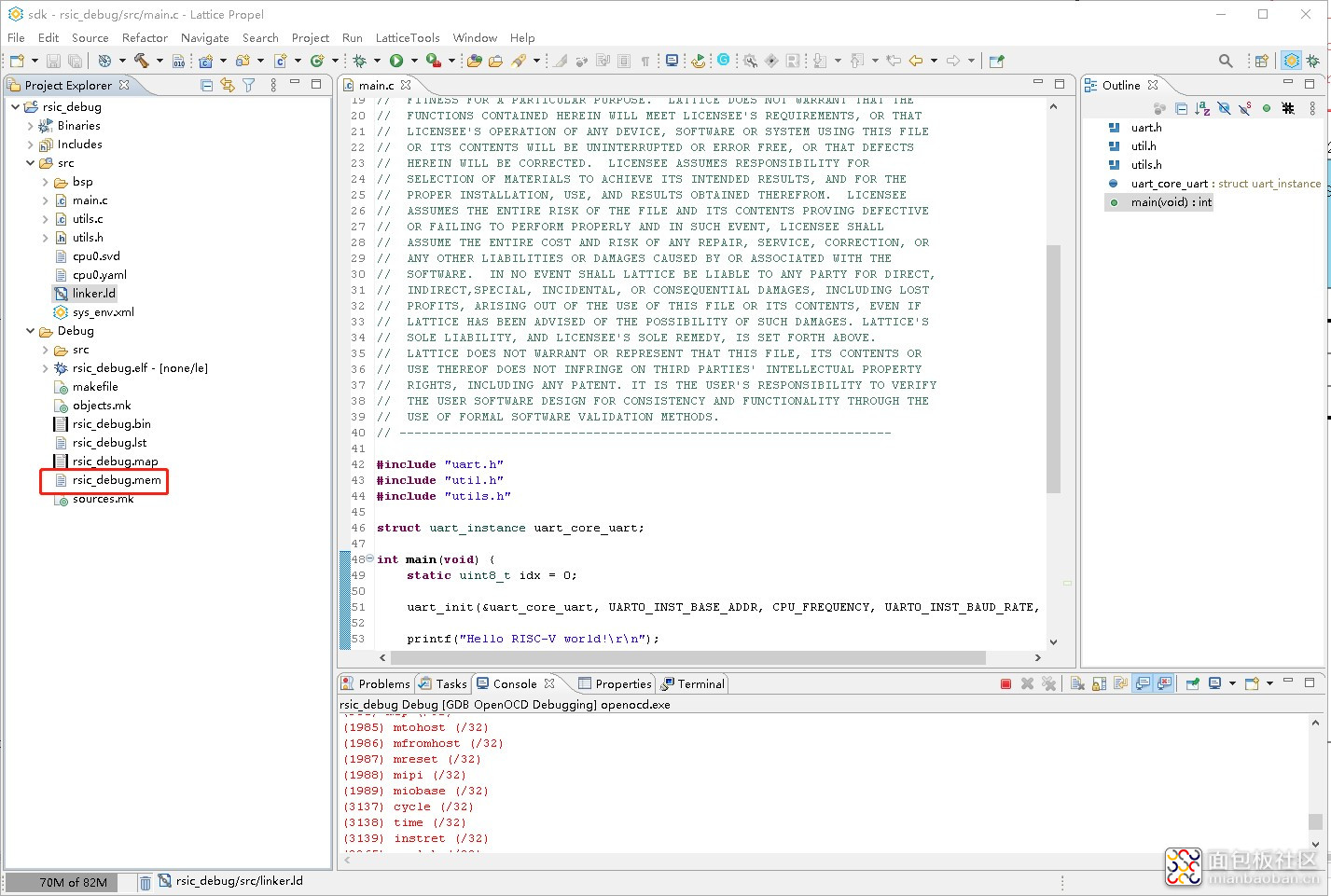

4.3 将Propel软件代码编译到SRAMRISC-V处理器的代码在器件内部的SRAM中运行,因此需要将Propel生成的C可执行代码以内存初始化文件的形式编译到SRAM中去。

Step1:添加初始化文件

如图13所示,在Propel SDK工程目录的Debug目录下,文件扩展名为.mem的就是C可执行Hex文件。

图13 可执行文件示意图

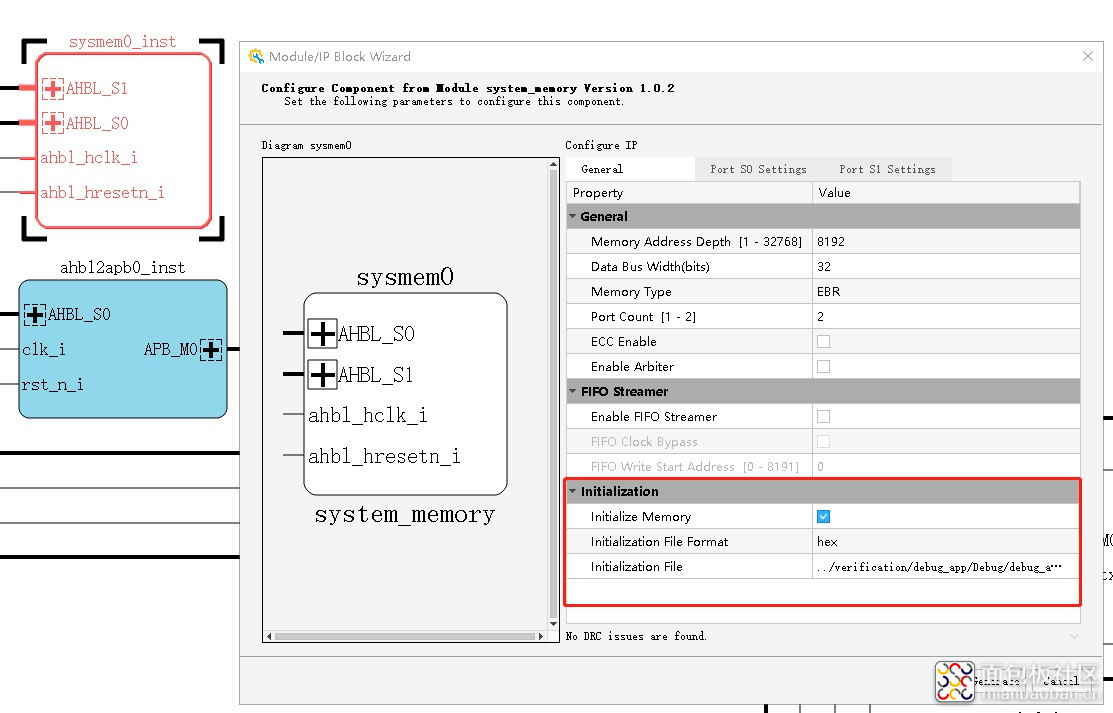

如图13所示,在Propel Bulider的图形化工程界面下,双击内存模块,将Initialize Memeroy勾选,并选择格式为hex,将初始化文件路径指向Propel下生成的.mem文件,Generate即可。

重复前文所述的规则检查、生成文件、Radiant编译生成bit流,将bit流文件烧写固化到SPI Flash,上电重启,RISC-V软件代码即可自动运行。

图14 添加可执行文件到SRAM

5.结语软件入门介绍到此结束,希望能够起到抛转引玉的作用。同时,也欢迎大家扫描下面的二维码加入QQ讨论群或微信公众号共同讨论,共同进步。

作者: panda君, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3403128.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/2

/2

curton 2021-1-16 14:47

欢迎点击

论坛> >机器人/工业电子> >工业电子与自动化

https://mbb.eet-china.com/forum/topic/85437_1_1.html