Open ADSP开源社区的ADSP-EDU-BF53X开发板教学视频第四集,主要讲了一下Blackfin的PLL和EBIU总线及应用,详细可到网站视频区去查看,或者点击以下链接:

http://www.openadsp.com/video.asp

http://v.youku.com/v_show/id_XMjg3Mjg1Njk2.html

http://player.youku.com/player.php/sid/XMjg3Mjg1Njk2/v.swf

PLL(Phase Locked Loop)是ADSP-BF53x的内核和时钟设置的机制,叫做锁相环。通过PLL配置当前处理器工作的内核和系统时钟。

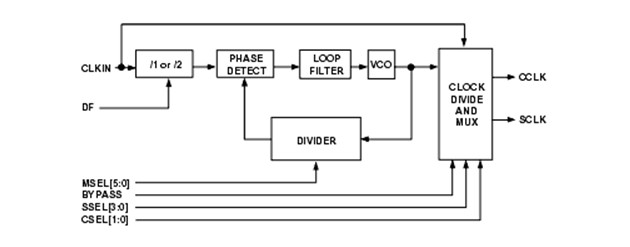

PLL机制如图:

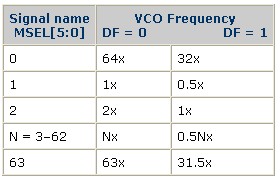

输入时钟送给ADSP-BF53x后,通过DF设置是否对输入时钟分频,然后将根据MSEL的值对时钟进行倍频,倍频后将时钟送给VCO,由VCO根据设置的分频系数,分出内核时钟和系统时钟。

MSEL占用6Bit,最大可设置64倍倍频。通常情况下,该倍频频率不要超过芯片允许的最大频率。

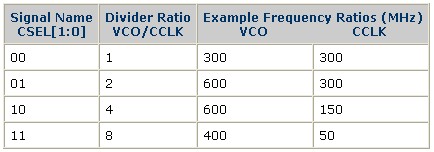

内核时钟分频系数占2Bit,最大可设置8倍分频,当为00时,内核时钟等于VCO时钟。设置的内核时钟不要超过芯片允许的最高频率。

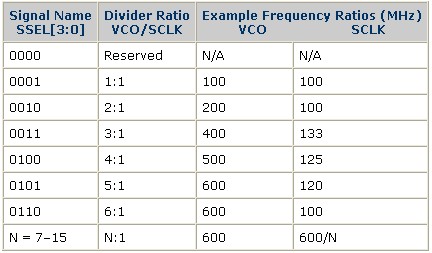

系统时钟分频系数占4bit,最大进行15倍的分频。设置的系统时钟不要超过133MHz。

|

寄存器 |

功能 |

|

PLL_DIV |

PLL分频寄存器,设置系统时钟和内核时钟分频系数 |

|

PLL_CTL |

PLL控制寄存器,设置VCO倍频系数和一些控制开关 |

|

PLL_STAT |

PLL状态寄存器,获取芯片当前工作的状态 |

|

PLL_LOCKCNT |

PLL计数器,用于设置计数时钟 |

*pPLL_DIV = pssel; //设置系统时钟分频系数,内核不做分频

asm("ssync;"); //系统同步

new_PLL_CTL = (pmsel & 0x3f) << 9; //将VCO倍频系数移位至需设置的位置

*pSIC_IWR |= 0xffffffff; //将系统中断唤醒使能

if (new_PLL_CTL != *pPLL_CTL) //判断是否已经配置过倍频系数

{

*pPLL_CTL = new_PLL_CTL; //配置倍频系数

asm("ssync;"); //系统同步

asm("idle;"); //将处理器设置为空闲

}

配置完PLL后,系统必须将系统设置为空闲后,系统再一次唤醒后,设置的值才会生效。

代码实现了将内核时钟配置为16倍倍频,将系统时钟配置为3倍分频。板卡上输入时钟为25MHz,所以VCO时钟配置后为25*16 =400MHz,内核时钟没有做分频,所以内核时钟等于VCO时钟,也为400MHz,系统时钟为400/3=133MHz。

运行代码后,处理器的内核时钟会运行在400MHz,系统时钟运行在133MHz。

EBIU接口是ADSP-BF53x的外部总线接口,ADSP-BF53x的EBIU接口共有16根数据线,19根地址线,支持同步的SDRAM接入和异步的总线外设接入,ADSP-BF53x的异步EBIU接口共有4个BANK,每个BANK 1MByte,支持各种总线接口设备。

EBIU接口采用指针方式访问,通过宏定义出要访问的地址,然后通过指针进行读写数据操作。

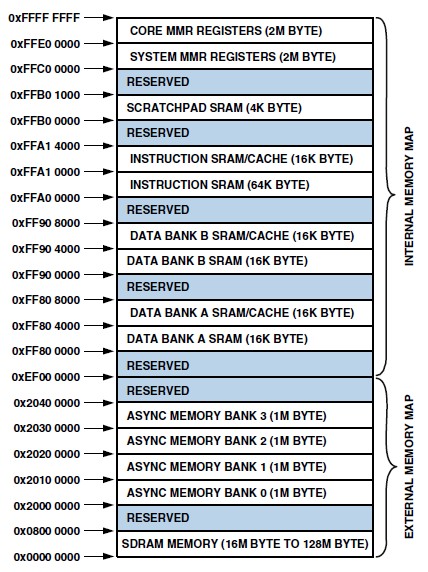

上图是ADSP-BF53x处理器的内存分配表,其中地址0~0x08000000为SDRAM地址,地址0x20000000~0x203fffff为EBIU的异步Bank地址。

|

寄存器 |

功能 |

|

EBIU_AMBCTL0 |

BANK0,BANK1时序配置寄存器 |

|

EBIU_AMBCTL1 |

BANK2,BANK3时序配置寄存器 |

|

EBIU_AMGCTL |

EBIU使能寄存器 |

#define pADDR (volatile unsigned short *)0x1000 //定义一个指针,地址指向0x1000

*pADDR = 0x1234; //向0x1000地址里写入数据0x1234

i = *pADDR; //读出该地址数据

printf("addr is %x\n",pADDR); //打印出当前访问的地址

printf("data is %x\n",i); //打印出当前地址中的数据

*pADDR = 0xaa55; //向0x1000地址里写入数据0xaa55

i = *pADDR; //读出该地址数据

printf("addr is %x\n",pADDR); //打印出当前访问的地址

printf("data is %x\n",i); //打印出当前地址中的数据

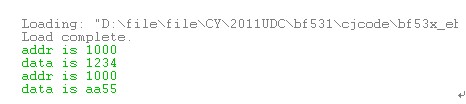

代码实现了通过EBIU接口访问SDRAM空间地址0x1000,向0x1000地址中写入数据并读出,打印出访问的地址和读出的数据。

优酷链接:http://v.youku.com/v_show/id_XMjg3Mjg1Njk2.html

清晰版下载地址:http://u.115.com/file/e6yal3r4 如需提取码,则是:e6yal3r4

开发板链接:http://item.taobao.com/item.htm?spm=1103Qmdt.3-3dfNy.h-1Akvus&id=9026190872&

/2

/2

文章评论(0条评论)

登录后参与讨论