笔者在网上找了很多关于上下拉电阻的资料,可是感觉说的还是很乱,依然很难理解。经过笔者的认真研究,现将自己所得所感写下来希望这只是个讨论的开始而绝非终结。

首先,想说上拉电阻几乎都是应运三极管电路而生的,但是本文基本上都属于定性的分析,避免对其定量分析,相信即使没有学过三极管晶体电路的同学还是可以基本理解的。

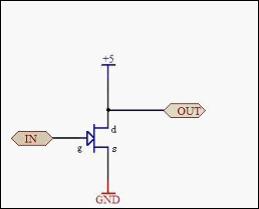

首先还要明确一个术语,所谓开漏(OD),开集(OC)电路就

是场效应管的漏极和三极管的集电极是断开的电路。如下图所示,这里希望大家不要纠结于我这个三极管用的是否正确只是想定性的解释一下什么是开漏(OD)或开集(OC)。

下面通过场效应管的漏极开路门电路的例子简单说明一下上拉电阻:

(1)如果没有上拉电阻(10k),将5V电源直接与场效应管相连。

当管子导通时,管子等效一电阻,大小为1k左右,因此5v电压全部加在此等效电阻上,输出端Vout=5v。

当管子截止时,管子等效电阻很高,可以理解为无穷大,因此5v的电压也全部加在此等效电阻上,Vout=5v。在这两种情况下,输出都为高电平,没有低电平。

(2)如果有上拉电阻(10k),将5v电源通过此上拉电阻与与场效应管相连。

当管子导通时,管子等效一电阻,大小为1k左右,与上拉电阻串联,输出端电压为加在此等效电阻上的电压,其大小为Vout = 5v * 管子等效电阻/(上拉电阻+管子等效电阻)=5v * 1/(10+1)=低电平。

当管子截止时,管子等效电阻很高,可以理解为无穷大,其与上拉电阻串联,输出端电压为加在此等效电阻上的电压,其大小为Vout = 5v * 管子等效电阻/(上拉电阻+管子等效电阻)=5v*无穷大/(无穷大+1)=高电平。

看到这里估计大家基本懂了七八分了吧,但是想必大家肯定还有一个疑问:难道P0口的高低电平输出与实际的输出是相反的吗?呵呵,现在让我们看一下8051单片机P0口的逻辑电路图:

其实,笔者一开始也纠结了很久,还专门查了一下场效应管的书,但是没有任何收获。这里请大家认真看一看P0.x 的D锁存器的输出端吧。没错问题就在这里D锁存器最终输出的是 ,根据D锁存器的原理,输出在这里经过了一次取反才又输出的,所以其本质是经过了两次取反才得到最终的外部输出的。不知这里跟大家讲清楚了没有。

现在让我们再来总结一下上拉下拉电阻的作用:

1、接电组就是为了防止输入端悬空 eg:上拉就是将不确定的信号通过一个电阻嵌位在高电平

2、减弱外部电流对芯片产生的干扰 eg:下拉电阻接到一个器件的输入端,多作 为抗干扰使用。因为输入端悬空时易受干扰或器件扫描时有间隙泄漏电压而 影响电路的性能。

3、保护CMOS内的保护二极管,一般电流不大于10mA

4、改变电平的电位,常用在TTL-CMOS匹配

5、增加高电平输出时的驱动能力 Eg:为OC、OD门提供电流。或者:如果该 器件需要高电压的话,而输出口的输出电压又不够,就需要加上拉电阻。

另外对于普通的P1,P2,P3接口,加上拉电阻可以提高抗干扰能力,抬高信号峰峰值,增强信号传输能力, 防止信号远距离传输时的线上反射,调节信号电平级别但是会增加负载。

下面再来探究一下关于电阻值的选择:

关于电阻的参数不能一概而定,要看电路其他参数而定,比如通常用在输入脚上的上拉电阻如果是为了抬高峰峰值,就要参考该引脚的内阻来定电阻值的!

|

1、一般LED的电流有几个mA就够了,最大不超过20mA,根据这个你就应该可以算出上拉电阻值来了。(5-0.7)/20mA=200ohm,差不多吧,保险起见考虑到功耗问题就用1~2k左右的电阻较为合适  以上4图表示的是上拉电阻从220欧到5.1K欧的LED亮度变化,当然实际还是有出入的,我们实验室开发板10K的电阻依然把LED点的很亮~(当然根据我们的计算电阻最小不要小于200欧姆,否则电流太大)

2、对于驱动光耦合器,如果是高电位有效,即耦合器输入端接端口和地之间,那么和LED的情况是一样的;如果是低电位有效,即耦合器输入端接端口和VCC之间,那么除了要串接一个1~4.7k之间的电阻以外,同时上拉电阻的阻值就可以用的特别大,用100k~500K之间的都行,当然用10K的也可以,但是考虑到省电问题,没有必要用那么小的。

3、对于驱动晶体管,又分为PNP和NPN管两种情况: a、对于NPN:毫无疑问NPN管是高电平有效的,因此上拉电阻的阻值用2K~20K之间的。具体的大小还要看晶体管的集电极接的是什么负载,对于LED类负载,由于发管电流很小,因此上拉电阻的阻值可以用20k的,但是对于管子的集电极为继电器负载时,由于集电极电流大,因此上拉电阻的阻值最好不要大于4.7K,有时候甚至用2K的。 b、对于PNP管,毫无疑问PNP管是低电平有效的,因此上拉电阻的阻值用100K以上的就行了,且管子的基极必须串接一个1~10K的电阻,阻值的大小要看管子集电极的负载是什么,对于LED类负载,由于发光电流很小,因此基极串接的电阻的阻值可以用20k的,但是对于管子的集电极为继电器负载时,由于集电极电流大,因此基极电阻的阻值最好不要大于4.7K。

4、对于驱动TTL集成电路,上拉电阻的阻值要用1~10K之间的,有时候电阻太大的话是拉不起来的,因此用的阻值较小。但是对于CMOS集成电路,上拉电阻的阻值就可以用的很大,一般不小于20K,通常用100K的,实际上对于CMOS电路,上拉电阻的阻值用1M的也是可以的,但是要注意上拉电阻的阻值太大的时候,容易产生干扰,尤其是线路板的线条很长的时候,这种干扰更严重,这种情况下上拉电阻不宜过大,一般要小于100K,有时候甚至小于10K。

5、关于I2C的上拉电阻:因为I2C接口的输出端是漏极开路或集电极开路,所以必须在接口外接上拉。上拉电阻的取值和I2C总线的频率有关,工作在standard mode时,其典型值为10K。在FAST mode时,为减少时钟上升时间,满足上升时间的要求,一般为1K。电阻的大小对时序有一定影响,对信号的上升时间和下降时间也有影响。总之一般情况下电压在5V时选4.7K左右,3.3V在3.3K左右.这样可加大驱动能力和加速边沿的翻转 I2C上拉电阻确定有一个计算公式: |

|

|

最后还要再补充一点内容:在51单片机中P0端口能驱动8个LSTTL负载。如需增加负载能力,可在P0总线上增加总线驱动器。P1,P2,P3端口各能驱动4个LSTTL负载。

所谓LSTTL百度解释为 Low-power Schottky TTL --低功耗肖特基而 LSTTL的功耗典型值为传统TTL的1/5。我们不对LSTTL进行任何分析,只是了解一下LSTTL的标准电平,0-5V,电流5-10mA左右。因此可以这样做出结论P0口的驱动能力是其他Px口的两倍左右。

最后提出一个问题:

在上拉电阻的第四个功能:改变电平的电位,常用在TTL-CMOS匹配 。这种电路是否是说上拉电阻于TTL和CMOS电路信号的传递电路中转换呢?具体电路应该如何接呢?还希望能一起讨论一下。

用户388268 2011-10-24 13:46

用户388268 2011-10-24 13:45

用户412991 2011-10-19 14:42

用户378040 2011-10-18 23:20

用户378040 2011-10-18 23:14