时序分析——Netlist的生成过程及有关的术语

Quartus II handbook 9.0 Volume 3

Page7-2 → Page7-7

1.时序分析流程:

↓

Create Timing Netlist(网表什么意思,具体指什么)

↓

Constrain the Design

↓

Update Timing Netlist

↓

Verify Static Timing Analysis Results(通过静态分析)

2.一些专业术语:

|

术语 |

解释 |

|

Cells |

Register、IOE |

|

Pins |

Input or Output of cells |

|

Ports |

Top-level module inputs or outputs; for example, device pins.从本质上说,ports也是pins,但是我们所说的pin是指某个寄存器的管脚,而port是指一个元器件(比如一个芯片)的管脚,即我们能看得到的管脚。 |

|

Netlist |

我们暂且称其为网表吧。当我们编译后Quartus会根据我们设计的功能模型,自动生成一个有关各个逻辑器件的网络布局图。 |

3.举例:

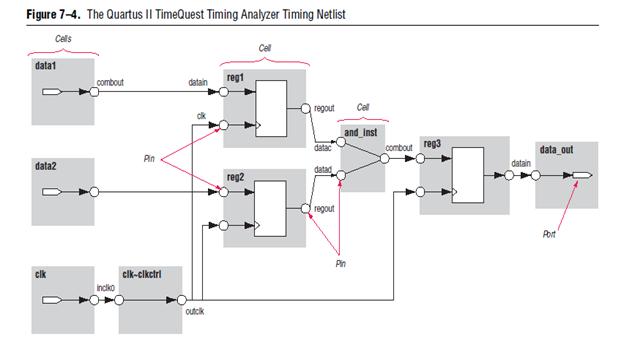

如果我们设计了一个如图1所示的电路,

图1 Sample Design

图1 Sample Design

经过编译后(未进行时序约束),Quartus会自动生成一个Netlist,如图2所示:

图2 Technology Map Viewer生成的Netlist

注:Technology Map Viewer的功能是“view the internal structure”.

从图中我们很清楚的看到我们所做的设计的内部连接情况,图中每一个用灰色突出的框都代表一个cell,每个celll上的圆圈都代表一个pin(可能不对,不过我认为应该是这样)。

上面的两个图(图1 和图2)是Quartus II 9.0 handbook上给出的,如果我们在quartus II 中写一个这样的程序,会生成什么样的RTL视图和Technology Map viewer中会有什么样的视图哪?

我编写了如下的程序:

module Netlist_test

(

clk,

rst_n,

data1,

data2,

data_out

);

input clk; //50M

input rst_n;

input data1;

input data2;

output data_out;

reg data1_r;

reg data2_r;

//-------------data1_r <= data1--------------

always @ (posedge clk, negedge rst_n)

if(!rst_n) data1_r <= 1'b0;

else

data1_r <= data1;

//-------------data2_r <= data2--------------

always @ (posedge clk, negedge rst_n)

if(!rst_n) data2_r <= 1'b0;

else

data2_r <= data2;

//----------------and------------------------

wire data_1and2;

assign data_1and2 = (data1_r + data2_r) ? 1'b1 : 1'b0;

//----------------data_out-------------------

reg data_out_r;

always @ (posedge clk, negedge rst_n)

if(!rst_n) data_out_r <= 1'b0;

else

data_out_r <= data_1and2;

assign data_out = data_out_r;

endmodule

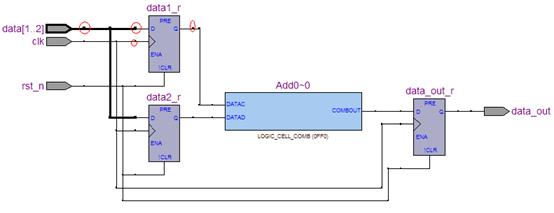

综合后,RTL视图如图3所示:

图 3 RTL视图

Technology Map viewer中的视图如图4所示

图 4 Technology Map viewer生成的视图

图中的黑块(用红圈标出)一般是各个pin的末端或走线折弯的地方。

/5

/5

文章评论(0条评论)

登录后参与讨论