Quartus II handbook 9.0 Volume 3

Clock Specification

Page 7-30

Derive PLL Clocks(生成PLL时钟)

1. 我们需要先设置一个时钟作为基准时钟,作为PLL的输入时钟。

2. 对于PLL的输出时钟,你可以使用creat_generated_clock命令手动创建或者使用derive_pll_clocks自动搜索时域网络并创建PLL的输出时钟。

3. derive_pll_clocks命令格式:

derive_pll_clocks

[-create_base_clocks]

[-use_tan_name]

|

选项 |

描述 |

|

-use_tan_name |

在默认情况下,时钟的名字为输出时钟的名字 |

derive_pll_clocks命令调用creat_generated_clock命令以在PLL的输出时钟上生成衍生时钟。creat_generated_clock的源是PLL的输入时钟引脚。在调用derive_pll_clocks命令之前或之后,我们必须手动的为PLL生成一个作为其输入时钟的基础时钟。如果我们未定义这个输入时钟,那么报告中就不会有PLL的输出时钟。取而代之的是分析仪会给出有类似Example 7-11的一个警告。

Example 7-11.Warning Message

Warning: The master clock for this clock assignment could no be derived.

Clock: <name of PLL output clock pin name> was not created.

你可以使用-create_base_clocks选项自动为PLL生成输入时钟。

你可以将derive_pll_clocks命令放在你的SDC文件中,以使得derive_pll_clocks命令能自动的检测PLL的任何变化。①由于SDC文件中包含derive_pll_clocks命令,当我们读该SDC文件时,相应的生成PLL输出引脚的creat_generated_clock命令将为产生;②如果你在使用derive_pll_clocks命令之后使用write_sdc-expand命令,那么新的SDC文件将为包含单独的PLL输出引脚的creat_generated_clock命令,并且不是derive_pll_clocks命令。任何修改PLL属性的行为将不会自动反应在SDC文件中。你必须手动写入可以反映PLL改变的derive_pll_clocks命令以更新creat_generated_clock命令。 【需做实验】

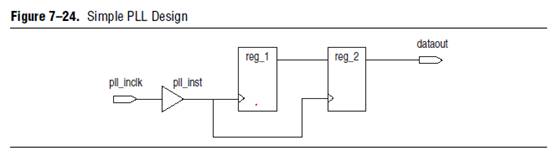

Figure 7-24 是关于PLL应用在Register to Register路径中的一个简单的例子。

|

当使用derive_pll_clocks命令,将自动对PLL进行约束时。

当这个Figure7-24使用这个命令时,Console栏将会产生如Example7-12的信息:

Example7-12. derive_pll_clocks Generated Message

Info: Deriving PLL Clocks:

Info: create_generated_clock –source

Pll_inst | altpll_component|pll|inclk[0] –divide_by 2 –name

Pll_inst | altpll_component|pll|clk[0]

Pll_inst | altpll_component|pll|clk[0]

Info:

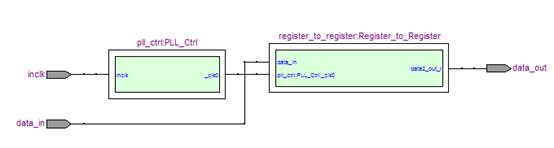

为了在Quartus II 9.0中实现Figure7-24的电路,我编写了一个简单的Verilog程序,通过编译得到如下图所示的Technology Map Viewer视图:

由于Quartus II TimeQuest Timing Analyzer自动调用了derive_pll_clocks命令,我们看到了如下信息:

Info: Deriving PLL Clocks

-----Info:create_generated_clock

-source {PLL_Ctrl|altpll_component|pll|inclk[0]}

-duty_cycle 50.00

-name {pll_ctrl:PLL_Ctrl|altpll:altpll_component|_clk0} {PLL_Ctrl|altpll_component|pll|clk[0]}

/5

/5

文章评论(0条评论)

登录后参与讨论