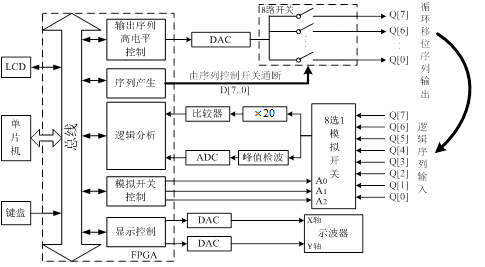

系统由数字信号发生器、逻辑分析仪和波形显示模块构成,如图1所示。为测试逻辑分析仪的门限电平分级功能,系统的信号源既可输出TTL电平序列,也可输出高电平**级可调的序列。由单片机控制DAC产生直流电平, FPGA产生的序列控制八路直流电路的通断,从而产生高电平可调的序列。信源输出通过8选1模拟开关,进入峰值检波电路,根据ADC采样得到的峰值在FPGA内部判断是否高于门限电平。若信号峰值高于门限,则根据过零比较器采集序列的逻辑状态。模拟开关地址选通频率应为序列时钟频率的8倍。在显示模块中,向示波器X轴送入锯齿波,向Y轴送入相应的波形数据,在示波器上稳定地显示出波形。

图1 系统框图

一、 理论分析、计算

1,  触发实现理论分析

触发实现理论分析

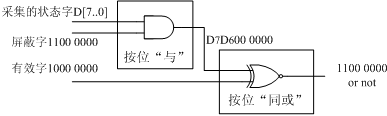

图2 触发判决示意图

当用户设置为单级触发时,系统直接将采集到的八路信号与]

触发字按位“同或”,若输出为“11111111”,则判断为满

足触发条件。

当用户设置为n级触发时,系统将采集到的八路信号的当前状态依次逆向循环移位1次、2次,···,n-1次,分别得到n级逻辑状态字。多级触发时,触发字的位数可能小于8位,此时需要将采集到的状态字的有效位与触发字的有效位相比较。假设触发字高两位有效,为“10”,判定一个状态字是否满足触发条件的具体示意如图2所示。首先用按位相“与”的方式屏蔽与触发无关的位,得到D7D600 0000;并生成一个有效字,该字与触发字有效位对应的位相同,其余位置“0”,为1000 0000。将D7D600 0000与1000 0000按位“同或”,若输出为“1100 0000”,则表示满足触发条件,否则,则判定为不满足条件。

/5

/5

用户427295 2012-10-4 10:21