作为电磁兼容性(EMC)的国际标准,主要适用IEC标准、CISPR标准和ISO标准。

IEC是指国际电工委员会(IEC:International Electrotechnical Commission),上述的“1Ω/150Ω直接耦合法”也被称为“VDE法”。

该方法是通过在半导体集成电路的接地端口连接相当于1Ω电阻的网络,在电源端口及信号端口等端口连接相当于150Ω电阻的网络,并且测量其频谱。但是,请注意,在电源电流较大的半导体集成电路(LSI)中,接地引脚处的1Ω电阻两端产生的电压会变大,如果影响到基本运行,则不适合这种方法。有电磁干扰(发射)相关的限值,如果不在相应值范围内,就不符合标准。本来IEC等标准中就规定了相应的测试方法,因此作为参考示例提供了限值。但是在一般的运用中,限值会被视为标准值。

现在让我们继续EMC计算方法和EMC仿真的话题。如前所述,IEC 61967-4标准中规定了从电磁兼容性(EMC)角度是对于半导体集成电路(LSI)的电源电流和信号电流进行测量的简单方法,计算步骤如下:

经过这种程度的计算处理后,我认为就可以将其创建为可在电路分析工具中使用的脚本或宏,并完成自动计算了。

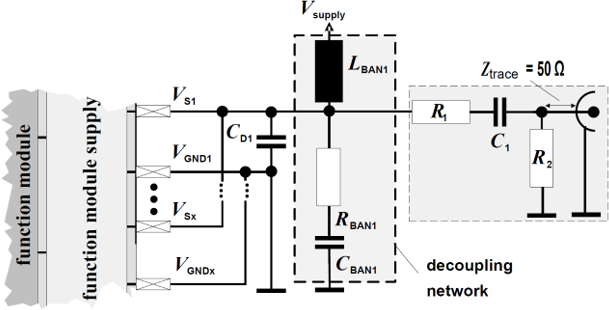

另外,在进行测试时,由于会连接频谱分析仪,因此需要再连接其输入阻抗50Ω后进行计算(请注意,这里容易出错!)。

如果符合标准,就“可喜可贺”,但如果不符合标准,就需要采取一些措施了,比如:改善①、即选择运行模式或重新设计硅片,更改②中取决于产品的去耦电容(CD)的种类或更改相关的值。

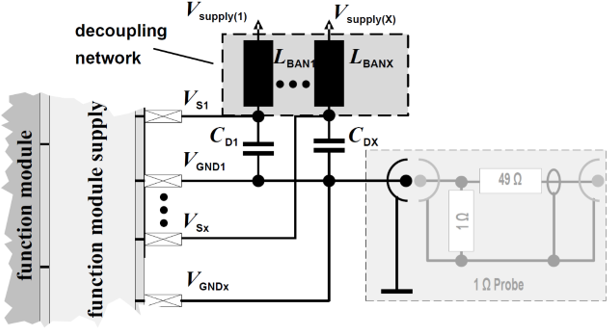

这次介绍的计算方法是可以通过电路分析工具尝试的方法,不需要实测值,使用简单的宏或脚本即可自动执行计算,符合IEC 62433标准,未使用数据同化,未使用降噪技术。下图是测试和计算用的参考图。

IEC 61967-4标准1Ω直接耦合法的测试电路/计算电路示例

(LBAN1=5uH,CD1:取决于产品)

(出处:Generic_IC_EMC_Test_Specification_2.1_180713_ZVEI.pdf)

IEC 61967-4标准150Ω直接耦合法的测试电路/计算电路示例

(R1=120Ω, C1=6.8nF, R2=51Ω, LBAN1=5uH, CD1:取决于产品, RBAN1:open, CBAN1:open)

(出处:Generic_IC_EMC_Test_Specification_2.1_180713_ZVEI.pdf)

感谢您阅读本文。

<书籍参考页码>

《LSI的EMC设计》,科学信息出版株式会社,2018年2月第一版,ISBN978-4-904774-68-7。

/4

/4

文章评论(0条评论)

登录后参与讨论