尽管看似简单,但PCB和高级封装中的功率传输仍然是设计人员面临的最大挑战之一,尤其是在数据中心、边缘计算、移动设备和电信/网络等环境中。在这些环境中,大量数据通过极高的数据速率通道传输,尽管我们非常关注信号完整性,但如果没有稳定的电源,这些系统都无法工作。

电源完整性发生在元件级和PCB级,正如其他人在本博客中提到的那样,电源完整性问题会造成信号完整性问题(抖动、电源/接地反弹、EMI)。虽然大多数更简单的电源完整性指南往往只关注PCB级别,但PCB和封装必须协同工作才能为互连提供稳定的电源。

本指南将尝试为PCB设计人员提供电源完整性的综合概念视图。虽然设计人员通常无法控制其封装,但他们可以采取措施确保其PCB和元件封装协同工作以提供稳定的电源。我将概述一些确保这些领域的电源完整性的主要方法,涵盖从叠层设计到最佳电容器选择的各个方面。

什么决定了PCB中的电源完整性?

电源完整性在交流和直流中都是一个概念;在直流情况下,我们关心铜线的尺寸是否合适以确保低直流压降。如果设计PCB时未考虑电源完整性,在电源轨上观察到的电压可能如下图所示。在I/O切换的阶段,从PCB的供电网络(PDN)拉出的电流脉冲会激发电源总线上的瞬变。逻辑电路重复切换示例如下所示。

发生这种情况的最常见实例是开关速度非常快的高速元件;同时切换更多的I/O会导致更大的功率需求,因此电源轨上可能会有更多噪声。放大瞬态响应时,瞬态会随着多个时间常数衰减,其中最主要的是一个长的低频时间常数,它在电源轨上产生的噪声最多。

通常,当给定PDN结构的信号上升时间更快时,生成的纹波可能具有更大的过冲,或者与更高频率的欠阻尼振荡相关的多个时间常数。这些振荡不可取,原因有两个:

出于这两个原因,设计人员必须采取一些措施来确保稳压器的直流电压输出尽可能稳定。

PDN阻抗、电感和电容

PCB中PDN的阻抗将是电源完整性的主要决定因素。稳压器也通过其反馈回路发挥作用(参见下文),但设计PDN阻抗是PCB设计人员的工作范围。目标是尽可能降低PDN阻抗,通常低于100 mOhm水平。

PDN阻抗由多个元素的存在决定,如下表所示。

元素 | 对电源完整性的影响 |

电源和接地层对 |

|

离散电容器 |

|

电容器封装和过孔电感 |

|

嵌入式电容 |

|

封装寄生效应 |

|

PDN拓扑

所有为高级处理器供电的PDN都是多端口网络。它们需要多重稳定电压,从高值到低逻辑电平。在高引脚数处理器上,电压从较高逻辑电平(5V0或3V3)下降到低至0V8是很常见的。

定义高级处理器PDN的电源树如下所示。该示例旨在说明如何构建不同的电源轨,这些轨道来自为整个系统供电的主电源或稳压器。

上方示例并非旨在推广到所有数字元件,但它应该说明许多元件将具备多个电源轨。由上述电源拓扑供电的数字处理器可以是任何类型的元件,例如大型FPGA、网络处理器、MPU、大型MCU、GPU或其他专用处理器。处理器上的I/O从电源轨获取电源,因此这些电源轨可能会在PDN中经历显着的瞬态噪声。

上方拓扑应该说明了两个设计要求的必要性:轨道之间的隔离,特别是同一稳压器提供的两个不同的轨道,这样就不会在彼此之间传递噪声。每条轨道还需要具备自己的低阻抗值,以确保任何噪声激发都很低。

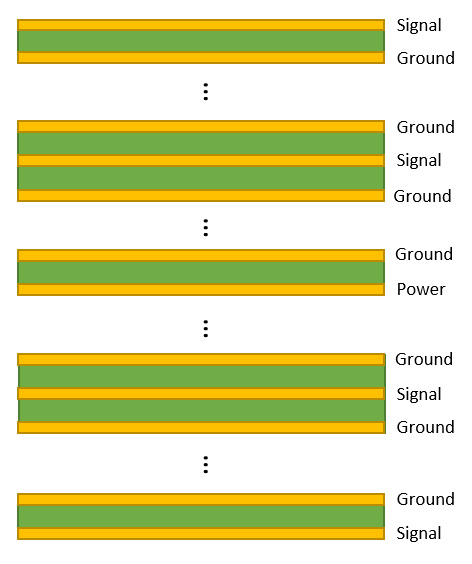

印刷电路板叠层和材料

在电源完整性方面,PCB叠层中的材料选择在提供确保稳定供电所需的电容方面起着重要作用。此外,层布置应提供电源轨,以将其放置在薄层上与接地层相邻的位置。这将有助于确保叠层为信号带宽高达约1 GHz的信号提供足够的电容。

当平面层中的可用电容不足,并且离散电容器受到寄生效应的限制时,可以通过[url=]嵌入式电容材料(ECM)[/url]提供所需的电容。这些材料是非常薄的薄膜(有些厚度低于1 mil),具有高达30的高Dk值。这些材料还可能具有非常高的损耗,会吸收在PCB基板中传播的EMI,从而减少从电路板边缘辐射的EMI。

就PDN阻抗而言,这些材料的影响分为四个部分:

这些材料的效果如下图所示。随着电介质厚度的减小,我们可以看到PDN中的谐振峰值会衰减并移至较低频率。如果我们增加材料中的介电损耗,也可以看到类似的结果。

封装寄生效应

元件封装具备与封装结构相关的自身寄生效应,并且元件封装具备自身的PDN阻抗。封装阻抗与PCB阻抗相结合,它们共同决定了半导体芯片上逻辑电路中电源输入端的噪声量。现代处理器包括封装内电容器,以帮助抑制瞬态激发,并将有用的信号带宽扩展到GHz范围。

不止于PCB和封装

我们涵盖了PCB和封装的所有内容,包括高级封装中一些最复杂的设计特性和模型。PCB设计人员可以控制电路板布局、叠层和布置/布线,并且还可以控制封装。在功率调节策略方面,我们尚未涉及两个重要主题:

VRM模块

PDN的结构以及许多高级元件需要多个电源轨的事实需要多个稳压器模块,它们相互为并联分支。固定电源稳压器的作用是补偿压降并通过反馈回路(大多数稳压器上的FB引脚)维持目标输出电压。反馈回路必须作出足够快的响应并调制输出,以试图稳定输出电压。

影响稳压器反馈环路响应的因素出现在布局级别和元件级别。

VRM的主题及其布局实践将在本网站的其他位置介绍。除了VRM设计和布局之外,设计人员还应专注于设计正确的叠层和电容器/材料选择,以确保在其工作带宽内具有足够低的PDN阻抗。正如我们上面所讨论的,布局和放置也会通过产生寄生效应,从而影响电源完整性。

仿真

仿真可以在交流或直流中进行,也可以在原理图或已完成的PCB布局中进行。对于以高达GHz的信号带宽运行的高速PCB,交流电源完整性仿真最为重要,因为它们可以揭示I/O开始切换时的电源总线纹波。

原理图中的交流仿真是基于SPICE的仿真,可以检查用于去耦/旁路的电容器网络的稳定性。这些模型允许估算电源总线响应,以及评估PDN中包含的电容是否足够。还需要评估由同一稳压器/VRM供电的不同电源轨之间的隔离性,这可以通过评估传输阻抗来确定。

交流仿真也可以在PCB布局中执行,但这需要电磁场求解器在给定PCB中PDN结构的情况下预测信号在空间和时间上的行为。这些模拟要求密集的计算,需要专门的软件。

尽管交流模拟在先进产品中很重要,但直流模拟在高速PCB中仍占有一席之地。在这些PCB的主处理器中切换的大量I/O会产生数安培的电流需求。当您使用一块为多个外围设备提供服务的超大型高速电路板(如底板)时,您必须在整个系统中支持大约100

A的电流,包括在快速处理器上为I/O供电的电源轨。因此,识别并消除电源轨中的极端电流非常重要。

/5

/5

文章评论(0条评论)

登录后参与讨论