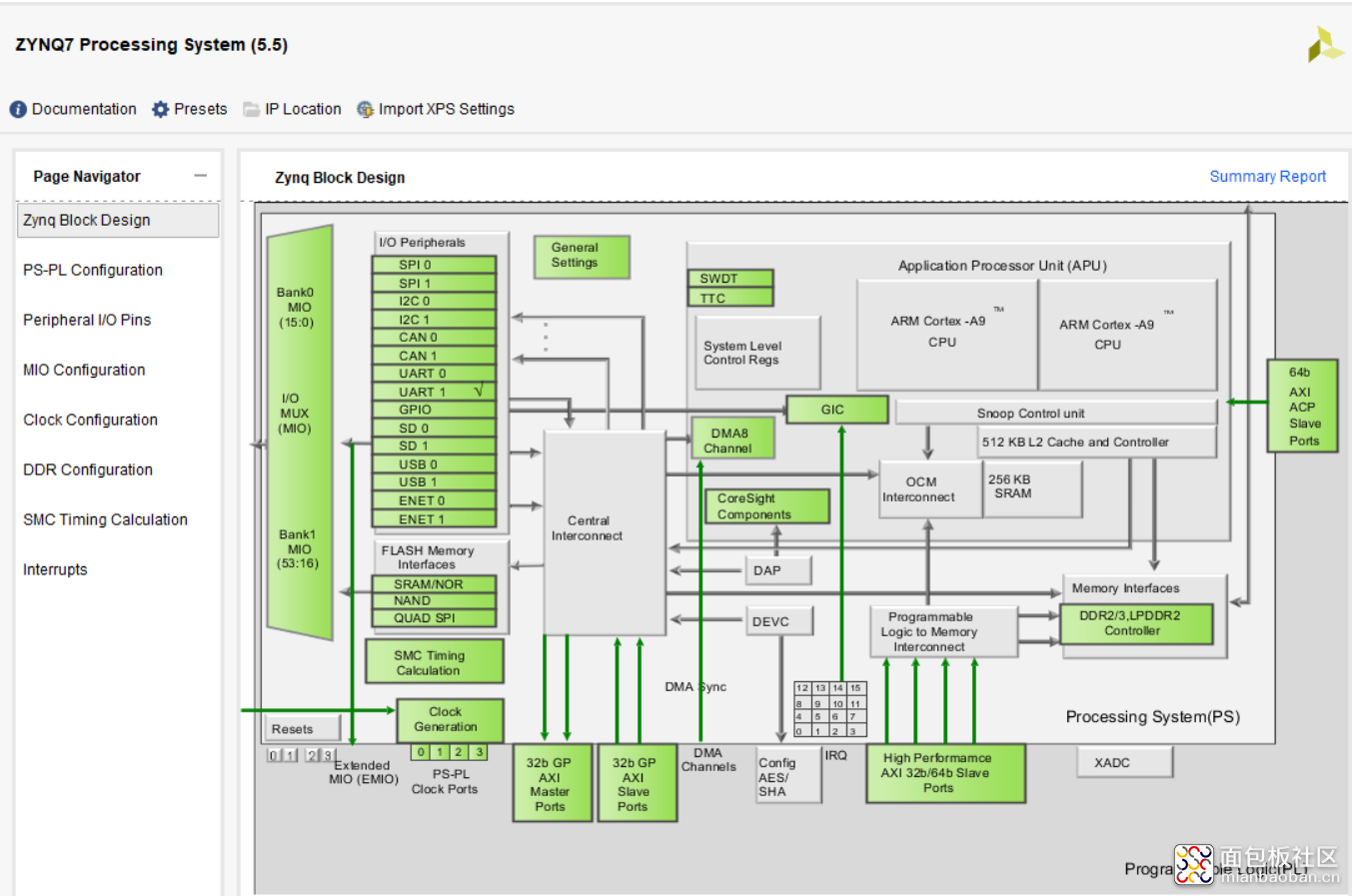

完成UART的配置,选择板子对应的MIO口,并配置电压。完成DDR的配置,选择正确的对应的DDR材料类型。时钟则输入33.33M,CPU比例选择6:2:1。

打开中断选型,勾选PL到PS的中断名IRQ_F2P[15:0]。

3,回到Block Design界面,添加axi-gpio模块,双击设置位宽,是否使能等。axi-gpio就是实现PS到PL的IO信号传输及使用。

4,完成后手动连线并再点击自动布线,Block Design基本创建完成。可以自己修改GPIO端口名称,方便记忆

5,然后点击 Sources 选顷卡,右键选择 sysetm, 在弹出框中选择 Generate Output Products,生成了Block Design的HDL文件。

讲白了就是把IP核设计编程HDL代码,即例化IP核的代码。

6, 右键选择sysetm, 在弹出框中选择Create HDL Wrapper,创建顶层HDL文件。

7,加入约束。这里用到了PL端的IO口,所以需要对IO约束,添加XDC约束文件。

8,综合、实现、编译生成bit流文件 。

9,硬件导入到SDK中,选择菜单 File->Export->Export Hardware,弹出的框中勾选上 Include bitstream。

10,Launch SDK。

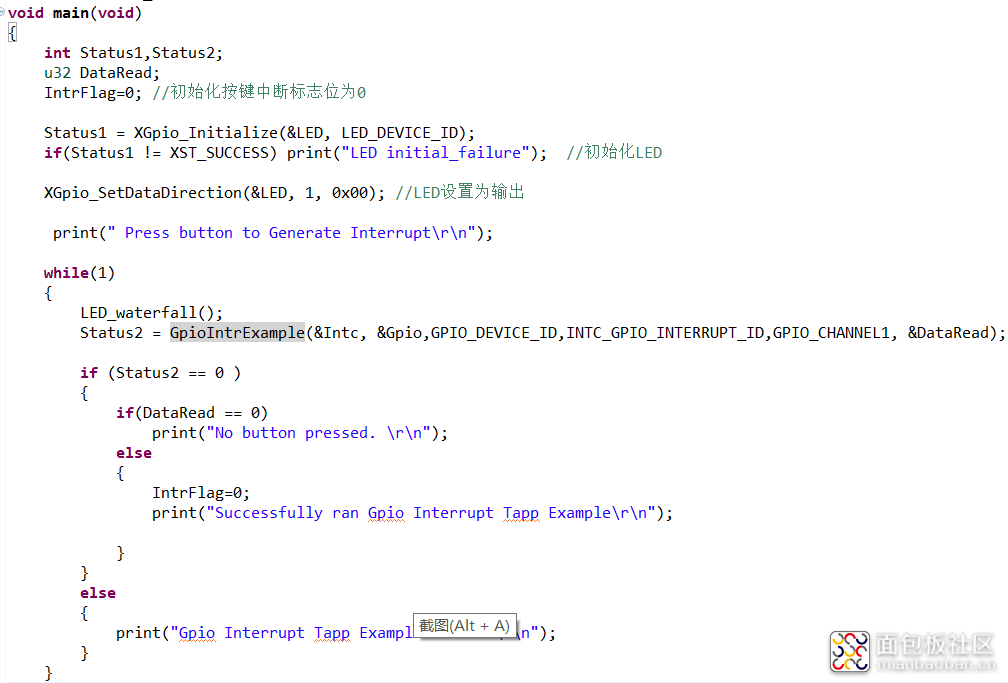

11,SDK 软件编程,会有模板参考。

主程序,需要用到的axi-gpio,timer,uart等在其他子程序中。

12 ,编译无错后,先在SDK菜单栏点击Program FPGA,再编译SDK 工程,右键工程名,选择Run As,选择Launch on Hardware,完成下载。

作者: 狂野的牛哥, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3867932.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

py二 2019-6-21 10:57