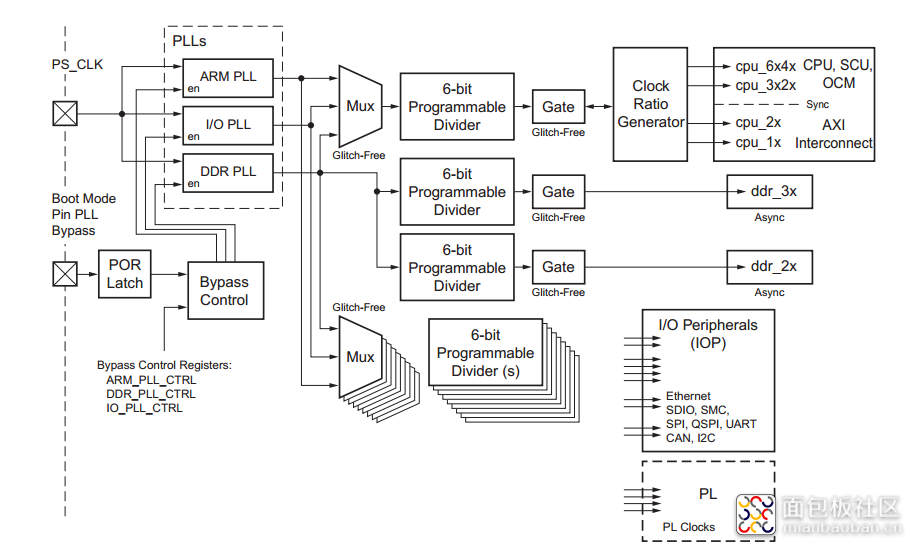

通常模式下,锁相环PLL是启动的,PS-CLK提供时钟信号,经过三路PLL,分别是:ARM PLL,产生时钟用于CPU和互联;IO PLL,产生时钟用于IO外围设备;DDR PLL,产生时钟用于DDR DRAM 控制器和AXI-HP接口。

旁路模式下,PS-CLK直接为各种时钟生成器产生时钟,此时不通过PLL。当POR复位信号上电复位时,对PLL旁路模式引脚采样,然后在PLL旁路模式和使能模式间进行选择。PLL旁路模式,运行系统较慢,但功耗低。

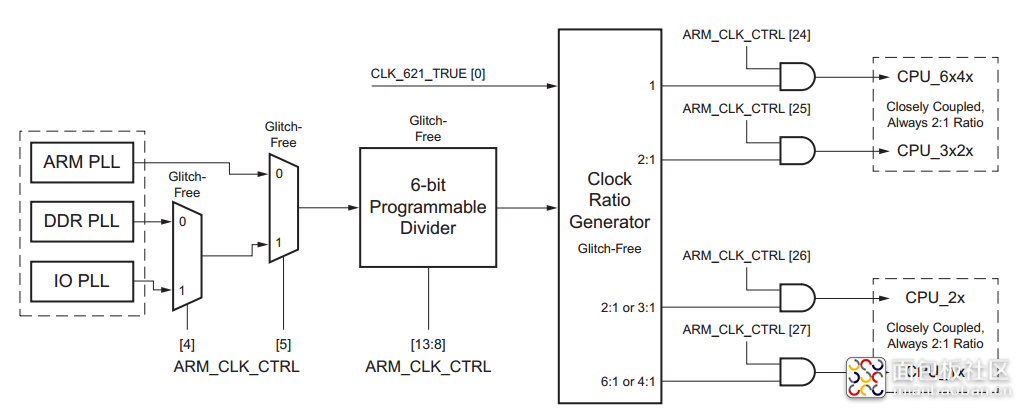

一,CPU 时钟域

时钟经过选择器和6位可编程分频器后,进入时钟比值生成器,最后产生4个独立的时钟信号:CPU_6x4x,CPU_3x2x,CPU_2x,CPU_1x。

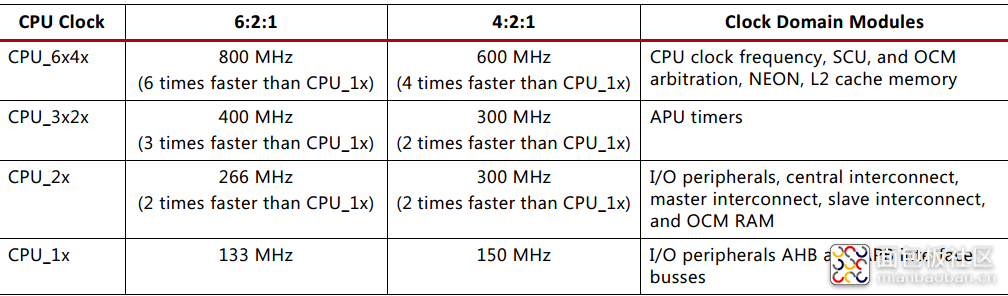

上图是关于四个时钟信号的范例,可以看到它们之间的倍数关系及应用场合。倍数关系是6:3:2:1或者4:2:2:1。

注:所有的CPU时钟互相同步,DDR时钟互相独立并且独立于CPU时钟,而IO的各个外设时钟完全异步。

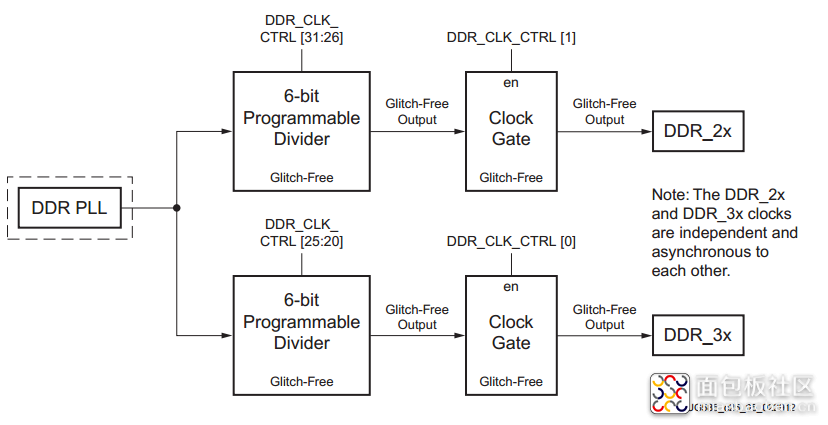

二,DDR时钟域

两个DDR时钟:DDR_2x和DDR_3x。前者驱动AXI_HP端口、由AXI_HP到DDR互联模块的AXI_HP互联路径;后者驱动DDR存储器端口、控制器和DRAM接口。

DDR_2x和DDR_3x互相独立,异步。

三 IO时钟域

IO上不同的外设时钟域都是独立的,完全异步,有的来自于系统内部,有的来自于外部引脚供给,种类繁多

四,时钟编程实例

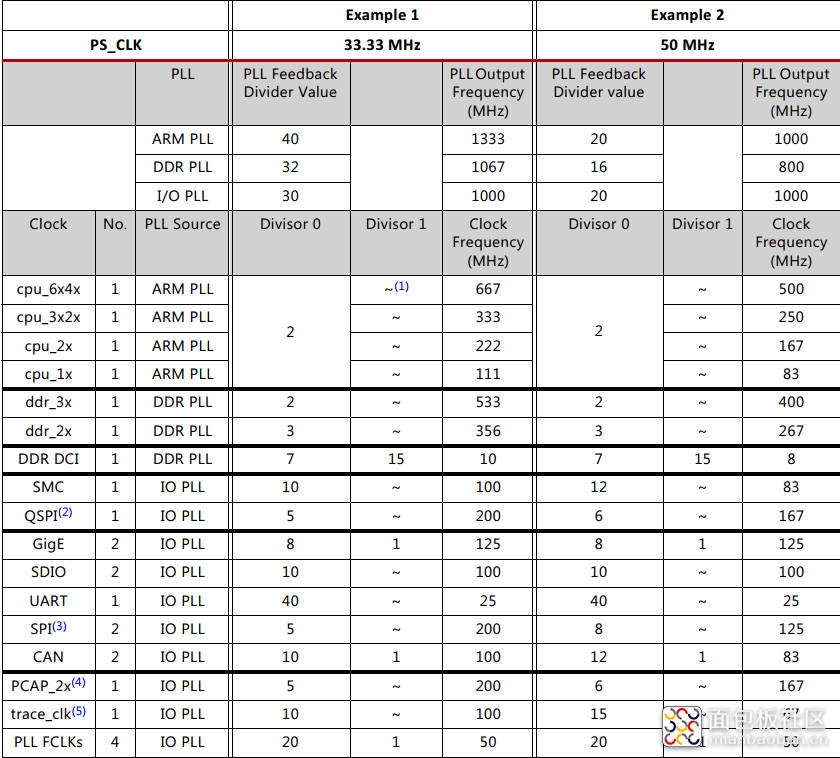

实例1,PS-CLK的输入时钟为33.33M,实例2是50Mhz。

就实例1而言,PLL的输出频率=PS-CLK频率×PLL反馈分频器值(M值),所以实例1种的三种PLL的输出频率就可以计算出来了。再具体到各个时钟,还要经过一或两次分频,即分频因子0和1,每个时钟基于的PLL除以分频因子,即可得到该时钟频率。

作者: 狂野的牛哥, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3867932.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

ihb_sina 2019-6-21 17:41