建立时间:数据至少需要提前于clk跳变沿多长时间到来,数据的采集才不会出错。

保持时间:数据在clk跳变沿之后,要维持多长时间不变才可以保证数据有效传输。

输出响应时间(输出延迟时间):从clk跳变沿到来之后,到输出端数据发生改变并稳定下来需要的时间

以上都由器件本身决定,之所以存在这些要求,也是由器件内部电路决定的。比如建立时间,通常是因为触发器内部电路要求数据必须在跳变沿到达前已经送到输入端的某一级电路,才可以继续往下传输。

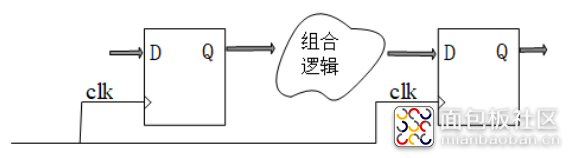

一个时序逻辑电路,如下图所示:

触发器D1的数据从Q端输出后,经过组合逻辑,传送到下一级触发器D2。

设:建立时间Tset,保持时间Th,输出延迟Tcq,经过组合逻辑时间为Tlogic。

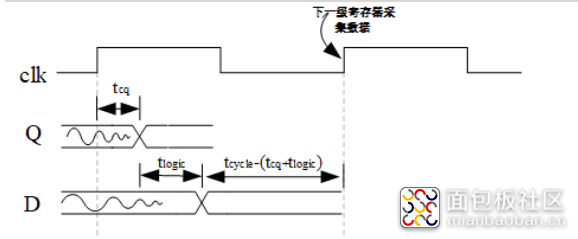

对于D1,时钟跳变沿来之后,数据经过时间Tcq才从Q端输出,再经过组合逻辑。

如上图,数据出组合逻辑以后,到下一个时钟跳变沿到来之前,这段时间长度为:Tcycle-Tcq-

Tlogic。这段时间必须要>=Tset,这样D2才可以正常工作。则:Tcycle-Tcq-Tlogic-Tset>=0

称Tcycle-Tcq-Tlogic-Tset为建立时间裕量(建立时间容限),这个值必须不能小于0.

如果再考虑时钟延迟,比如时钟正延迟,即clk到达D2的时间比到D1的时间延迟,延迟量设为:Tdelay

则建立时间裕量可以再加上Tdelay,这对D2的建立时间是有好处的。反之,若时钟反向延迟,即延迟方向与数据方向相反,则对D2建立时间有害,会缩短建立时间裕量。

再看保持时间裕量

D1的输出经过Tcq+Tlogic后就会到达D2的输入D端,也就说时钟跳变沿到达以后,D2维持数据的时间是Tcq+Tlogic,过了这个时间,新的数据就又出现在输入D端,那D端的数据就无法保持不变了,如果这个时候上一个数据的保持时间还没结束,那这个数据可能就无法正常传输了。

Tcq+Tlogic-Th为保持时间裕量(容限),显然这个值也是需要>=0的。

若时钟延迟,正向延迟,则D1的跳变沿先到,那数据就会提前到达D2的输入端,保持时间裕量变成Tcq+Tlogic-Th-Tdelay,显然这对D2的保持时间是不利的。

反之,若反向延迟,则对D2的保持时间有利。

综上,会发现同样的时钟延迟下,建立时间裕量和保持时间裕量是矛盾的,所以在实际中,要平衡考虑二者,让二者都符合时序约束。

用户3893407 2019-7-1 15:12

用户1013590 2019-6-22 18:09

curton 2019-5-31 23:22

curton 2019-5-30 18:27

quw431979_163.com 2019-5-28 08:57