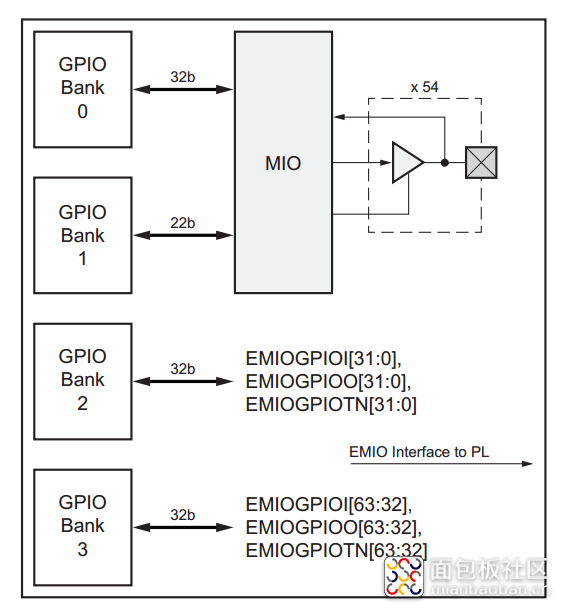

ZYNQ的GPIO模块分为四个BANK,从Bank0-Bank3,其中Bank0和1是MIO(多用途IO),Bank1和2是EMIO(扩展MIO)。

MIO共有54个引脚,每个引脚都可以复用连接PS的不同外设,如UART0的RXD和TXD既可以连接在MIO10和11上,也可连在14,15上,18和19,22和23等等都可以。所以MIO就是一端直接连接在PS上的线,这个线具体连接PS内部的哪一个外设,有多种选择。另一端可以直接外连,进行输入输出信号。

54个MIO分为两个电压组,MIO0-15是一个,MIO16-53是第二个。每组同时共有一个电压,所以分配MIO多种挂外设时候,应该考虑电压是否匹配。

EMIO,一端连接在PL上,另一端仍是连接在PS上。如输入的信号,从PL的引脚上走,经过EMIO,还是进到了PS中。

通过EMIO接口,在PS和PL之间提供了192个GPIO信号。其中64个输入信号,128个输出信号。128输出信号中,64个输出是真正的输出,另外64个是使能输出。

注意:Bank1只有22位,这和其他几个Bank都是32位是不一样的。

可以对每个GPIO或者每一组进行编程操作。

每个GPIO都提供了可编程的中断。

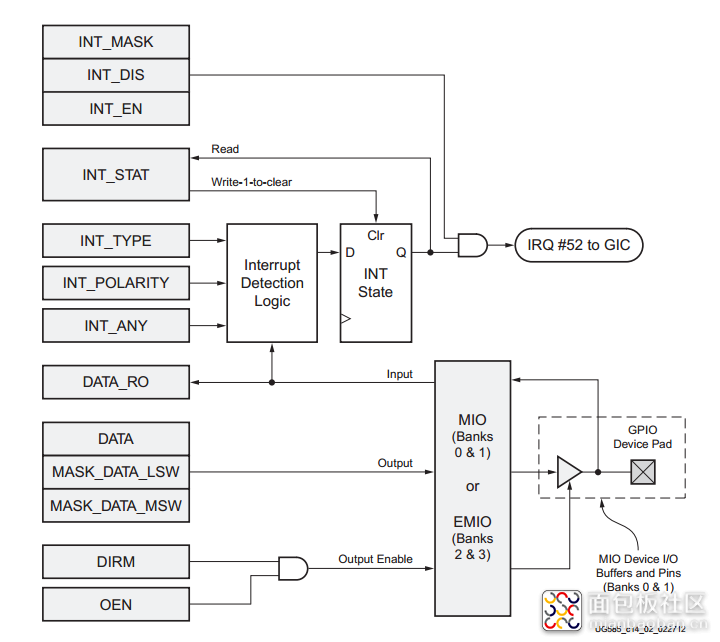

Bank0和Bank1的功能结构如下图所示:

具体每个寄存器的意义及说明查看数据手册,列出几个。

DATA_RO:总是读取GPIO引脚状态,不管GPIO是输入还是输出。注:若没有将MIO配置为GPIO,则DATA_R0的内容不可知。因为不能通过GPIO寄存器去读取非GPIO的值。

DATA:GPIO配置为输出时,该寄存器给输出的值。如果读该寄存器,返回上次写入的DATA值(或MASK_DATA值)

DIRM:方向模式。由于输入逻辑是一直使能的,所以这个寄存器是配置使能/禁止输出驱动的。为0,禁止输出驱动器。

OEN:输出使能。当GPIO配置为输出时,控制使能/禁止输出。为0,禁止输出驱动器。禁止输出时,引脚为三态。

注:如果MIO的TRI_ENABLE=1,则使能三态并禁止驱动器,直接忽略OEN。

用于EMIO的寄存器和MIO的相同,但是存在一些功能差异:

①输入时候,是来自于PL的布线连接,只要DIRM设置为0是输入模式,则直接读取DATA_R0的值,和OEN以及输出值都无关。

②输出时没三态使能,OEN对其无影响。此时DIRM设为1,表示为输出。

注意:①Bank0的【8:7】引脚用于在复位时候控制IO缓冲区的电压模式,故必须根据正确的电压模式由外部系统来驱动。为了防止被逻辑驱动,不作为通用输入。当系统启动完成后,可用作通用输出。

②所有的GPIO共享一个中断,IRQ ID是52,所以必须通过INT_MASK和INT_STAT寄存器来确定引起中断的GPIO源。

GPIO的编程流程:

如:

MIO引脚10作为输出

引脚配置:

①将0x0000_0400写到gpio.DIRM_0 寄存器,把方向设置为输出。就是第10位(从0开始数)置1,一共32位,控制Bank0的32位。

②将0x0000_0400写到gpio.OEN_0 寄存器,输出使能。

写数据:可以直接写gpio.DATA_0,也可以通过MASK_DATA来写。

MIO引脚10作为输入

将0x0写到gpio.DIRM_0 寄存器,也就是保证第10位是0即可,其他位是1无所谓。

读数据:读取gpio.DATA_RO_0寄存器,也就是读取所有Bank0输入引脚的值,或者在输入引脚上使用中断逻辑。

对GPIO的读写操作,既可以使用读写寄存器的底层函数来操作,也可以直接使用API函数进行GPIO的配置,SDK都提供了。

作者: 狂野的牛哥, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3867932.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

用户1013590 2019-6-22 18:15

curton 2019-5-22 08:13

curton 2019-5-15 21:25

curton 2019-5-14 15:29

curton 2019-5-13 16:21