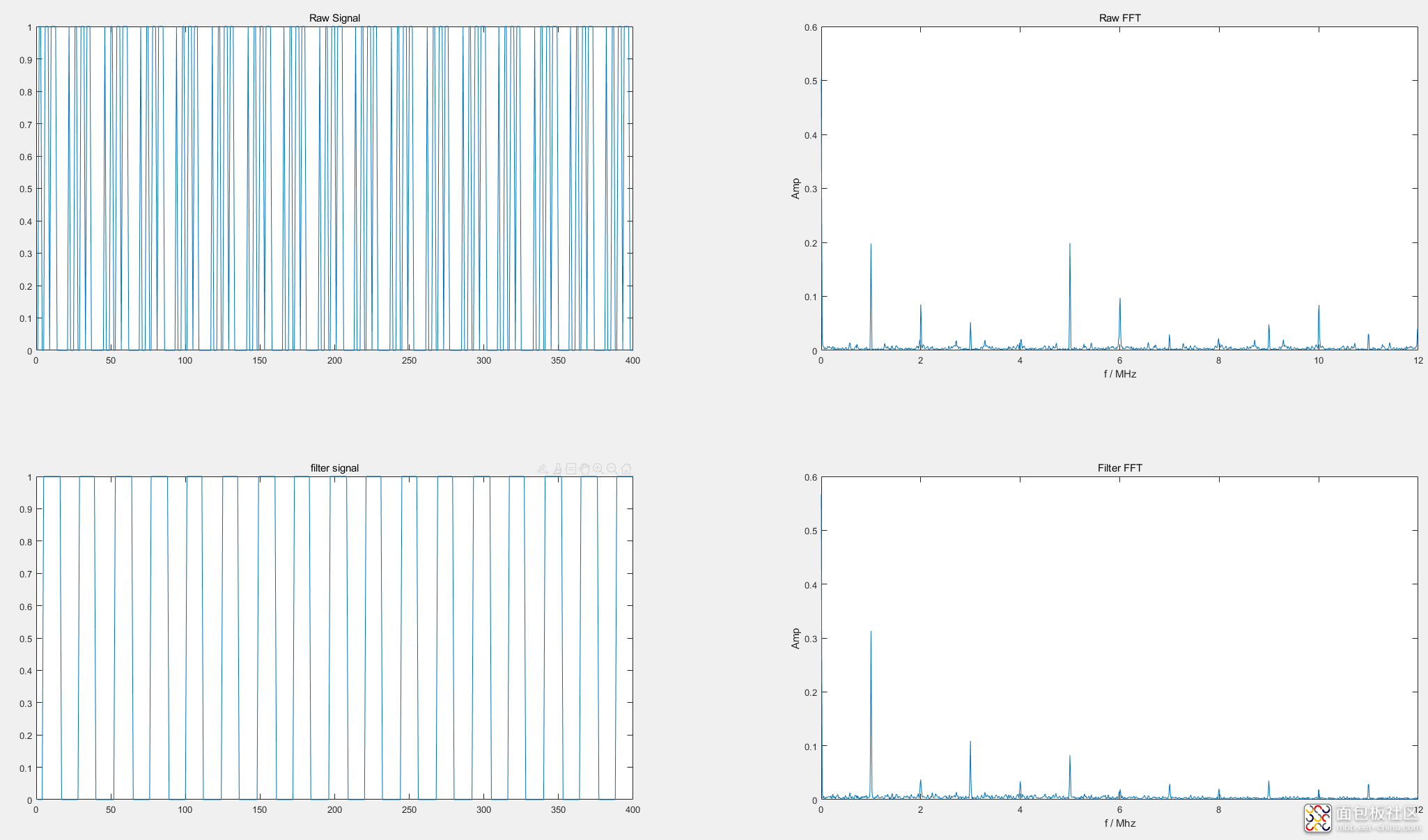

1M + 5M + 6M

Numerator = [14 108 296 404 296 108 14];

幅频响应

原始信号1~40

ans =

列 1 至 33

0 1 1 0 0 1 1 1 0 1 1 1 1 0 0 0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0

列 34 至 40

1 1 1 0 0 0 0

输出数据

列 1 至 16

0 14 122 404 700 714 526 540 822 1010 930 836 944 1118 1104 822

列 17 至 32

418 122 14 0 0 14 108 296 404 310 230 418 700 714 526 540

列 33 至 40

822 1010 930 836 930 1010 808 418

方波化数据

列 1 至 33

0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1

列 34 至 40

1 1 1 1 1 1 0

作者: illyasviel, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3882207.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论