原创

Imec 发布叉片器件仿真结果,将是 2nm 技术节点的终极方案?

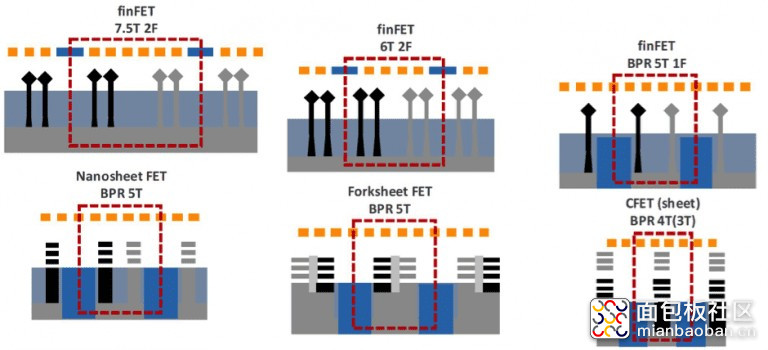

在2019年IEEE国际电子器件会议上,比利时微电子研究机构 imec 展示了叉片(forksheet)器件的首个标准单元仿真结果,专为3nm以下逻辑技术节点而设计。与纳米片器件相比,缩减n到p间距可将性能提高10%。当与缩放助推器结合使用时,新的器件架构将使逻辑标准单元的高度降低至4.3轨,再加上单元模板优化可将面积减少20%以上。结果表明,叉片架构作为一种潜在的解决方案,可以将纳米片结构的可扩展性扩展到3nm技术节点以上。

imec最近提出,叉片器件是垂直堆叠的横向全栅纳米片器件的自然扩展。与全栅式纳米片器件相反,在叉片中,纳米片现在由三栅极叉形结构控制,这种结构是通过在栅极构图之前在P和NMOS器件之间引入介电壁来实现的。该壁将p栅沟槽与n栅沟槽物理隔离,从而实现了更紧密的n到p间距-这是FinFET或纳米片结构无法解决的挑战。由于减少了n到p的分隔,因此预期分叉片具有出色的面积和性能可伸缩性。

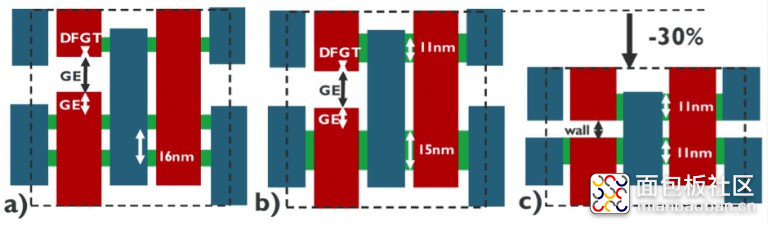

标准单元仿真首次确认了叉片设备架构具有出色的功率性能区域(PPA)潜力。所研究的器件针对imec的2nm技术节点,采用42nm的接触栅间距和金属间距为16nm的5T标准单元库。拟议的设计包括缩放助推器,例如埋藏的电源轨和环绕触点。与纳米片器件相比,报告了10%的速度增益(恒定功率)和24%的功率减小(恒定速度)。较小的栅漏重叠会导致米勒电容降低,从而可以部分解释性能的提升。最后,n至p间距的减小可用于将轨道高度从5T减小到4.3T。利用器件结构的进一步布局优化可将单元面积减少20%以上。当在SRAM设计中实现时,仿真显示出8nm pn间距的组合单元面积缩放和性能提高了30%。

imec的3D混合缩放计划总监Julien Ryckaert说:“随着行业从平面到FinFET,再到垂直堆叠纳米片的规模扩展,叉片的概念被认为是非破坏性的扩展。” 纳米片装置主要是为了改善静电控制和驱动强度而引入的。但是,FinFET和纳米片架构都具有较大的n-p器件分隔距离,从而阻碍了进一步的可扩展性。forksheet体系结构是解决这一难题的一种方法,可以视为2nm以上的最终逻辑“通用” CMOS器件。继续扩展到叉片器件之外,我们建议使用互补FET(或CFET)作为器件候选。”叉片的工艺流程类似于纳米片器件,只是有限的附加工艺步骤。

这项工作是imec逻辑INSITE R&D计划的一部分,该计划针对3nm以上技术节点的设计技术共同优化(DTCO)。结果将在12月11日(星期三)第36.5节(下午3:15)在IEDM2019上发布。此外,计划总监Julien Ryckaert将在周三11 日 上午10:20 举行的受邀演讲中,讨论imec走向2纳米以下技术节点的路线图,从垂直堆叠纳米片,叉片到最终的CFET,并结合缩放助推器使用。

图1 –从FinFET到纳米片(带有埋入式电源轨(BPR)),叉子片和CFET。

图2 – a)FinFET,b)全方位栅纳米片和c)叉片的SRAM半单元的布局。由于pn空间不受栅极扩展(GE),栅极切割(GE)或虚拟鳍状栅极褶皱(DFGT)的支配,因此分叉片可以提供高达30%的位单元高度缩放比例。

/5

/5

curton 2019-12-16 19:51