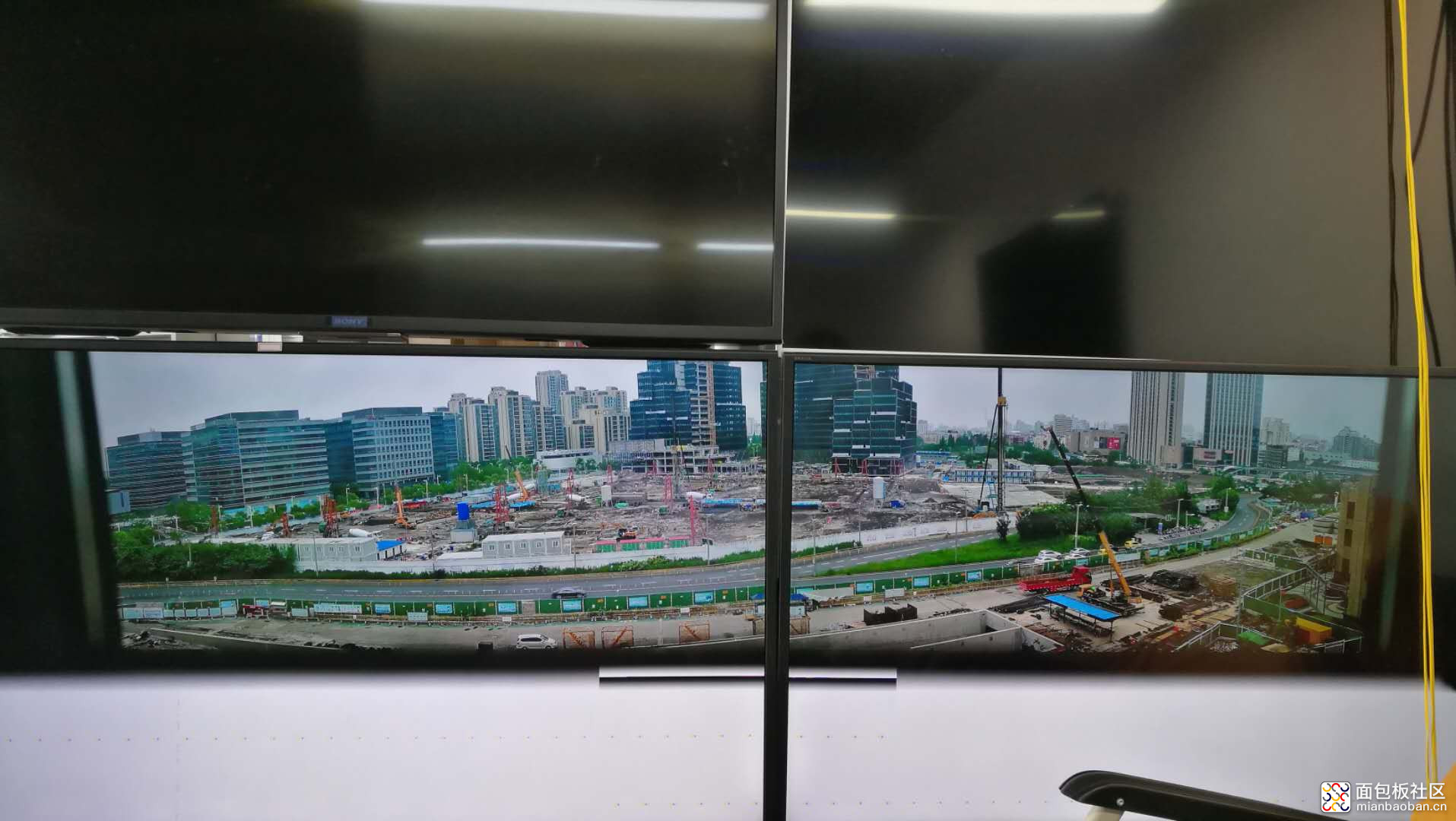

4路4K@30帧镜头1*4的排列方式,FPGA拼接融合后输出2路4K的效果显示如下:

不知道怎么传视频,所以各位也看不到动态效果了。只能以文字的方式简单的说明一下。首先输出是足帧(30)的,没有卡顿的现象;其次接缝不是很明显,要仔细找才能找到。有些地方甚至找不到。

注:知道了如何添加视频,现在补上。目前上传的是用win10自带的录屏工具录制vlc显示界面作成的,原始拼接后的视频大小是7680*2160的。(2020.10.16)

之前做过2*8(16个4k镜头)的拼接显示,用的是A算法(因为人在职场,为了避免泄密,所以尽量省略),接缝处呈现出比较明显的阴阳脸,看起来像旧年代的补丁裤,一块一块缝合而成。目前用的的B算法(算法原理也烂大街了,准确讲是烂网了,不过还要省略),效果就好多了。可以说给人的感觉是惊艳的。如果你人在现场相信肯定会说:恩,不错,小伙子做的还可以啊。恩,多么希望是个小伙子啊。刚开始做FPGA的时候,很期望看到程序运行后的效果,恩,很有成就感。现在呢,项目下来之后,想一想各个功能怎么实现,脑子里过一过,好,结束了,已经看到效果了。

昨天考虑了下后面2*8用B算法怎么实现,想想还是很有意思的,或者说有挑战性的。不过想到后面要用代码写出来,就用没激情了。好比运动员每天做同样的训练,枯燥无味。运动员,还有比赛,以至于有夺冠的那天,身披国旗,荣耀万分。问题是这里没有比赛啊,没有了动力自然有些懒散。如果有下来这种情况,估计会好些吧。

客户:这个产品不错啊

厂家:恩,我们的工程师打字很快的,去年还得了个冠军。

说到代码,不的不提硬件开发语言verilog,与汇编比的话,的确好多了。不过和c等高级语言相比。就好比一个是搬砖,一个是3D打印。恩,我先擦擦汗,太晒了。哎,说你呢,这里整的不平,时钟怎么顺利流过去,要自流平不是。

有人说有HLS了啊,可以用c、c++、以至于python等。之前用HLS做了一个人脸识别,也就是将算法HLS化,HLS再硬件化。恩,5帧左右吧,速度提不上去。HLS转成的verilog代码基本上不是给人看的,dataflow等基本命令也就是那么几个,怎么能造出跑车呢。造个卡车还是可以的,本来不用的资源都可以用上。总之速度与资源的处理都不理想,很难走进现实,不是么。以至于时不时想自己做个C转verilog的软件。这也算是个梦想吧。有人可能会说,FPGA厂商有实用案例啊。恩,定制化的项目,手把手指导过的(自己猜想,如有不实,请忽略),程序不知道改了多少遍吧,实用的局限性比较大吧。当然HLS也并不是一无是处,跑个简单的算法,比如加减乘除,sin、cos等,接口简单算法明确,还是很省时间的。

不过话说回来,将枯燥与乏味的事情做到极致,乃至推陈出新,何尝不是一种工匠精神,矛盾的共同体不是么。哎,你们都别动,这个砖是我的。

我是做FPGA逻辑设计的一个小学生,说了这么多,词不达意之处,还望各位海涵与指正。

作者: 大工小工, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3885609.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

洋仔 2020-5-13 10:45

qwqr3231 2020-5-12 14:46