:

FPGA与STM32等嵌入式开发最大的一个优点就是,可以在时序仿真阶段验证超过90%的功能,发现90%的问题。当所有的仿真没问题了,才能进行最后一步:板级调试。如果仿真都不对,那就没必要下载到芯片里了。

STM32等单片机,使用J-Link或ST-Link等调试器,可以进行在线调试,由于C代码是顺序执行的,我们可以插入断点,让程序停在我们需要的位置,或者是实时查看一些变量的数值,大大提高了我们Debug的速度,提高产品的开发效率。

对于FPGA来说,仿真毕竟是仿真,可以理解为理想条件,而最终我们的代码是需要运行在实际的FPGA芯片硬件上的。

所以也会遇到仿真正常,实际下载到板子里不正常的情况。

这种现象通常有两种原因:1.程序有BUG,2.硬件有问题。

比如实际程序中复位信号是低电平复位,而实际电路中设计的复位按键按下才是高电平,这样按键未按下就会导致程序一直处于复位状态。当然,这只是一种最简单的问题点,实际开发过程中,仿真与实际运行不匹配的情况还有很多。那么如何才能以最快的速度找到问题点呢?

早期的FPGA调试方法通常使用外部的逻辑分析仪硬件设备,连接到FPGA芯片的外部管脚上,如果想查看内部信号,还需要把这些信号定义成Output引出到外部管脚进行了测量,如果是多位数据,这样就会占用大量的管脚,但是此类工具有个优点就是支持多种协议解析,可以非常方便的查看协议的报文数据。

如果有一种工具能像单片机开发那样,通过调试器JTAG接口实时获取运行过程中寄存器的数值就好了。有需求就有市场,FPGA厂商也考虑到了开发者的这种需求,都在自家产品上加上了这个功能,那就是片上逻辑分析仪,就像在芯片内装了一个逻辑分析仪ELA(Embedded Logic Analyzer),可以实时监测数据的变化,还可以设置触发条件等!

FPGA领域几大厂家提供嵌入式逻辑分析仪:

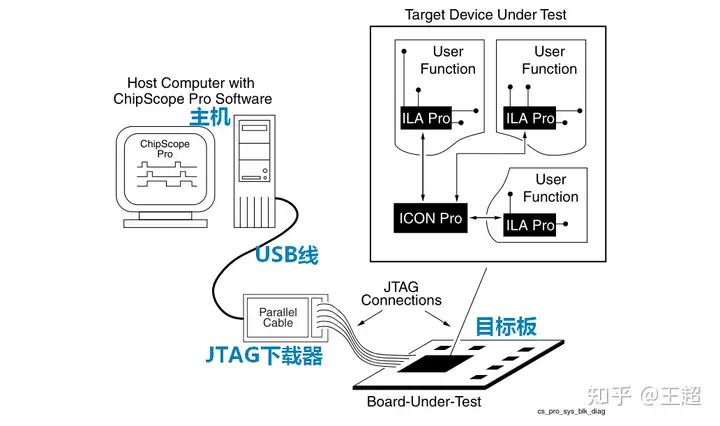

这些工具都是嵌入式逻辑分析仪,大大提高了Debug速度。这类工具的原理通常是以预先设定的时钟速率实时采样FPGA的内部信号,并暂存于FPGA的内部RAM中,当满足预设的触发条件后,通过JTAG将存储在片内RAM中的数据传输至PC上,PC接收到数据后,通过上位机把数据展现出来。

关于FPGA的逻辑分析仪介绍,可以查看之前写的笔记:

可以说,片上逻辑分析仪是FPGA的标配,这部分功能通常需要FPGA硬件和EDA工具软件两方面支持。

高云FPGA也集成了片上逻辑分析仪(Gowin Analyzer Oscilloscope,以下简称 GAO),GAO的原理是通过采样时钟,将用户设定的信号采样缓存到片内未使用的RAM空间中,当满足用户设定的触发条件时,将RAM中的数据通过JTAG发送到上位机中,并显示出来。

本文介绍,基于TangNano 4K开发板,即高云小蜜蜂GW1NSR-4C FPGA芯片,演示如何创建GAO配置文件,如何使用逻辑分析仪抓取信号并获取波形文件。

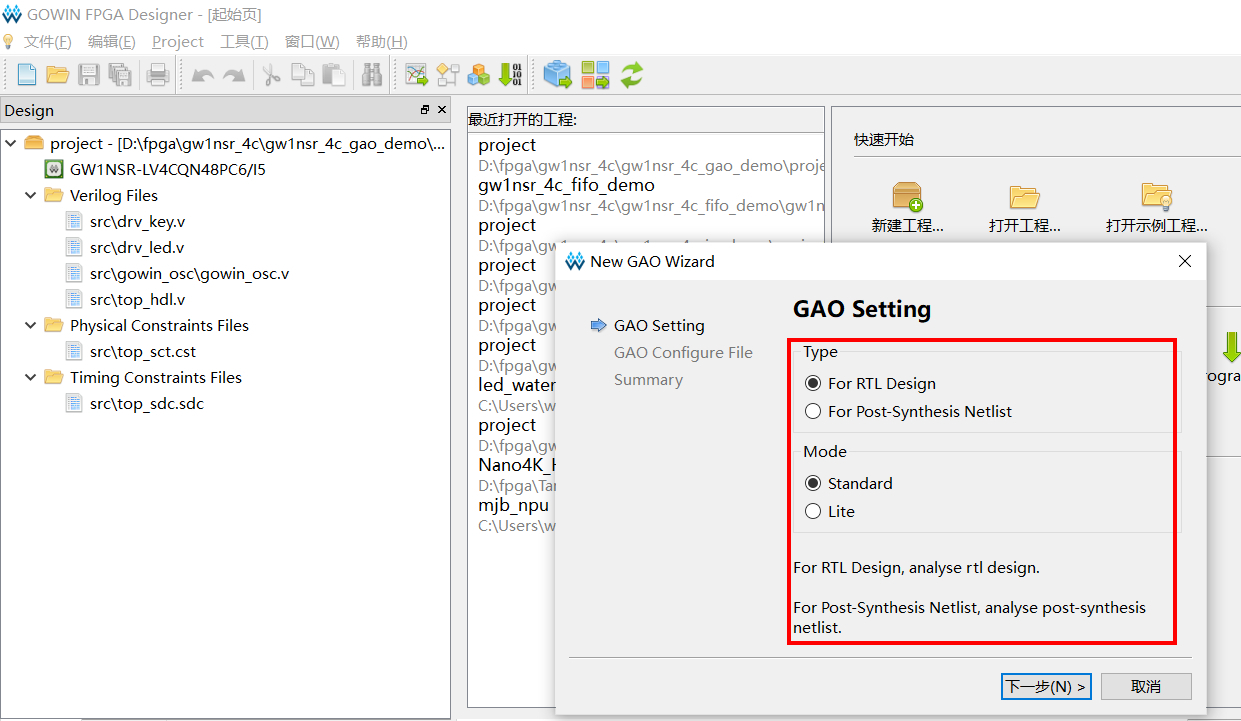

GAO支持RTL级信号捕获和综合后网表插入两种方式,并且提供Standard GAO 和 Lite GAO 两种版本。

GAO具有如下特性:

关于高云FPGA GAO逻辑分析仪的使用,可以参考官方文档,在云源软件的安装目录下:

D:\Program\Gowin\Gowin_V1.9.8.07_Education\IDE\doc\CN\SUG114-2.5_Gowin在线逻辑分析仪用户指南.pdf打开一个现有工程,顶层文件如下:

/***************************************************************模块功能为当按键有效按下时,控制LED状态翻转。

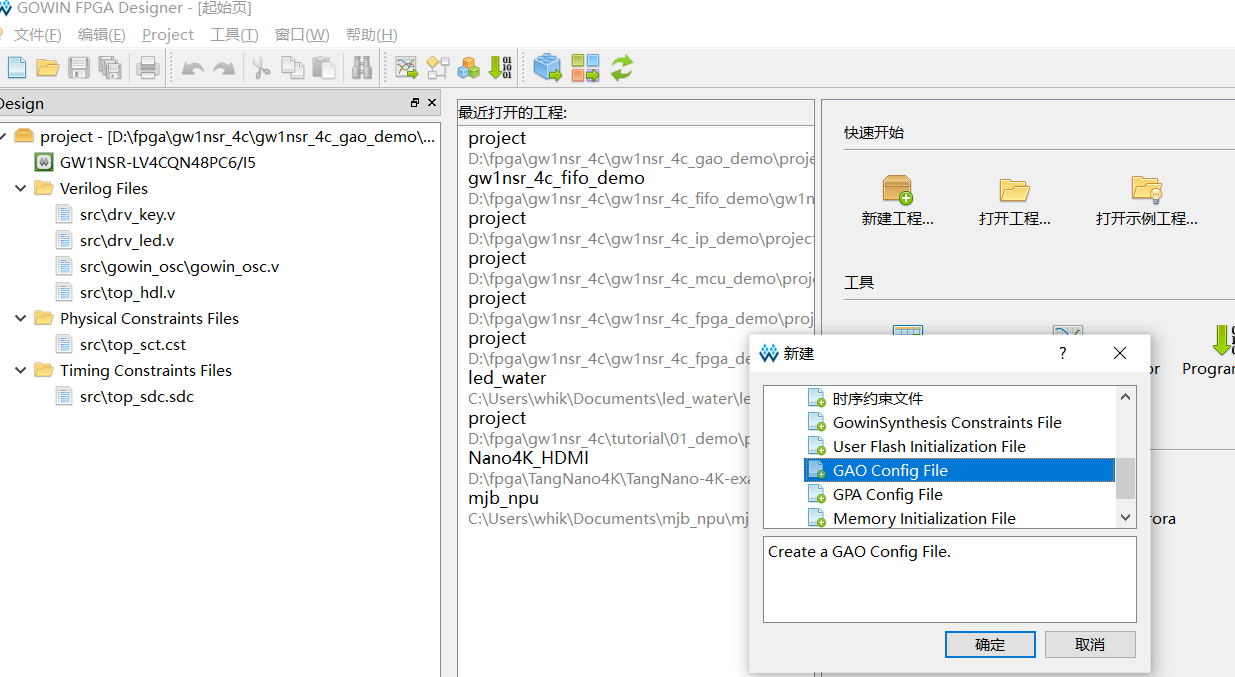

4. 新建GAO文件新建GAO Config文件,用于配置逻辑分析仪的参数。

选择默认配置

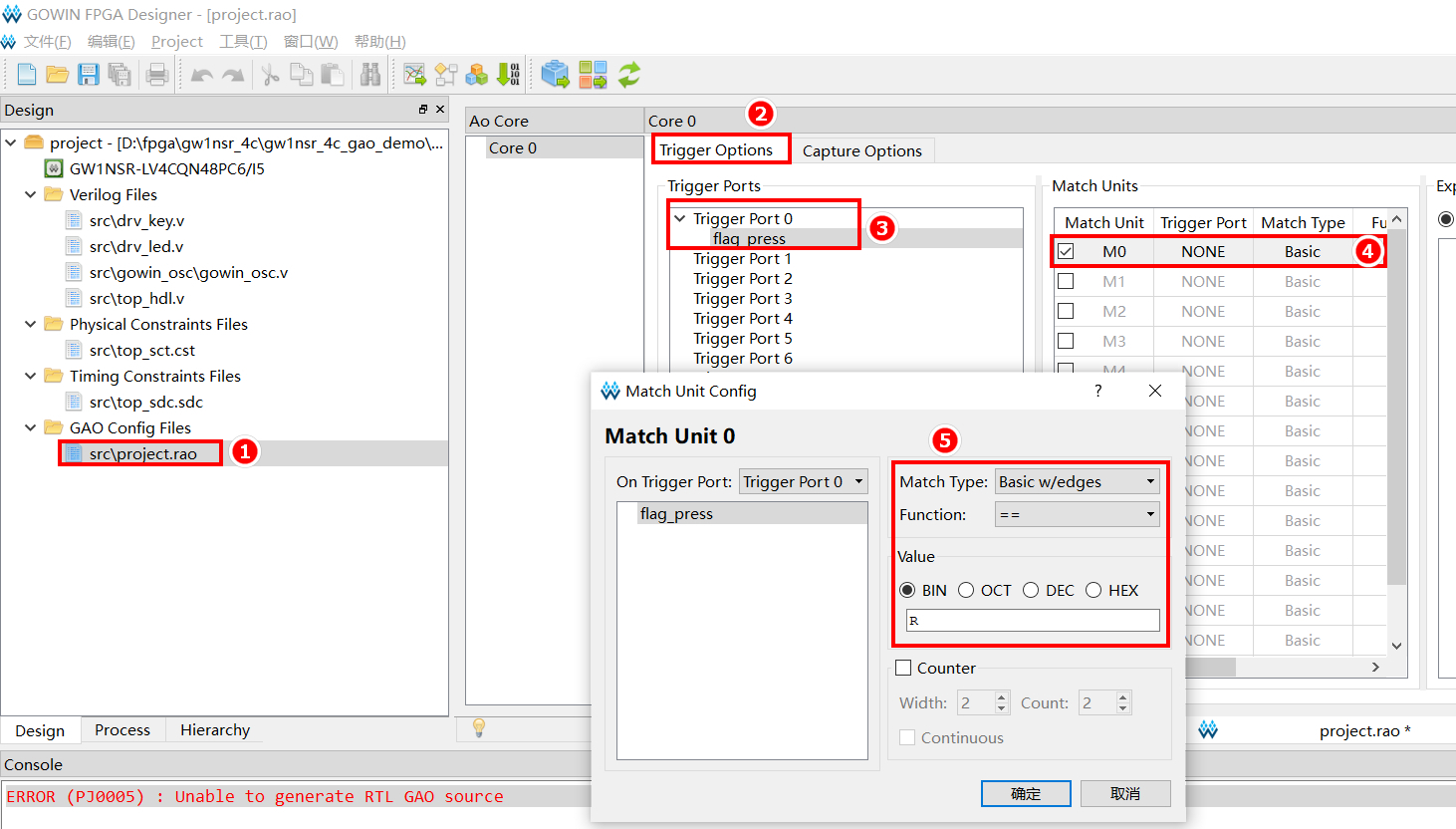

5. 添加触发信号

5. 添加触发信号

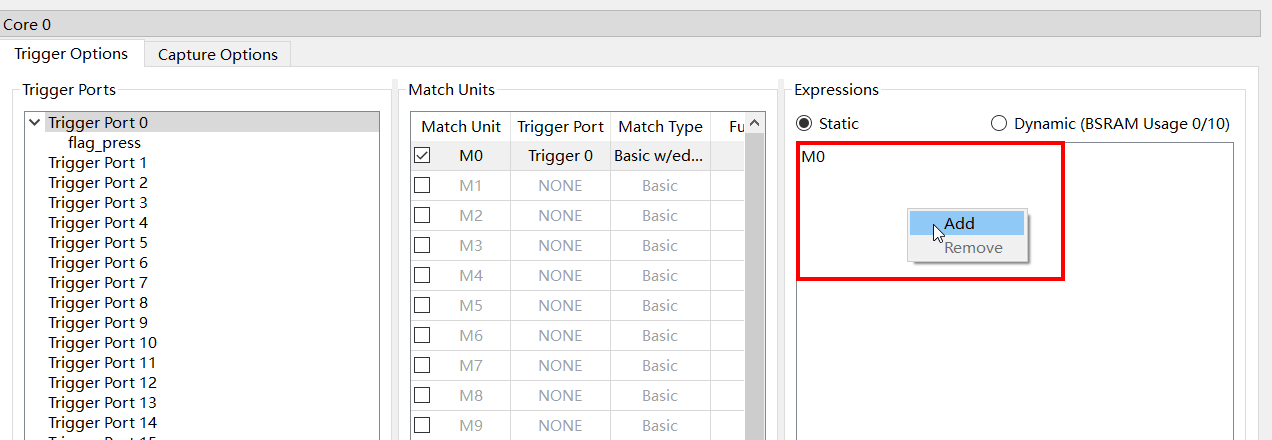

双击打开rao文件,在Trigger Options中选择触发信号,这里选择滤波后的按键按下信号,为1个时钟周期宽的高脉冲,触发方式设置为上升沿触发。

6. 设置采样参数

6. 设置采样参数

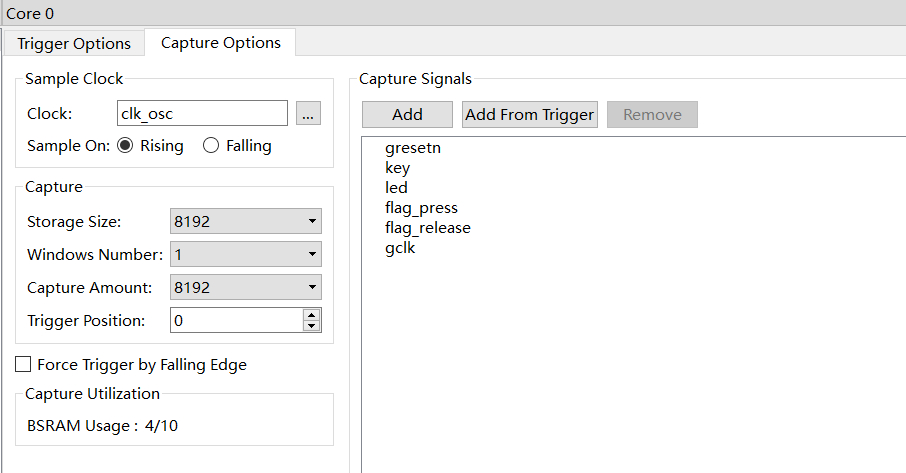

选择片上时钟250M二分频为125M,作为逻辑分析仪的采样时钟,再添加几个要观测的信号,并设置采样深度和触发位置。

返回Trigger Options,右键添加M0表达式,如果有多组,可以设置逻辑关系

保存gao文件,综合、布局布线。

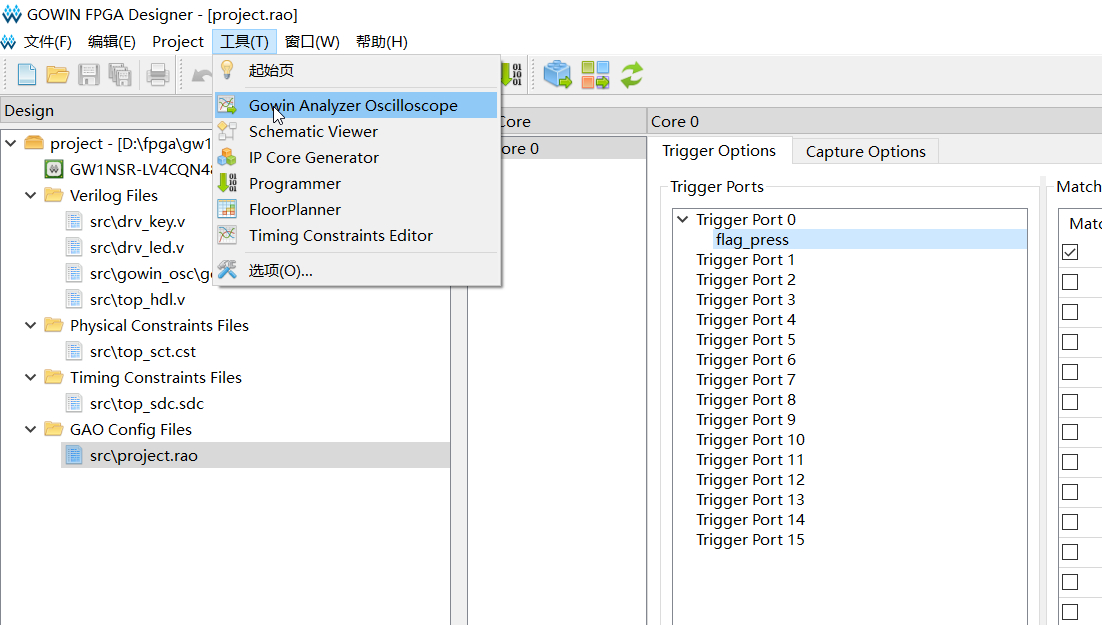

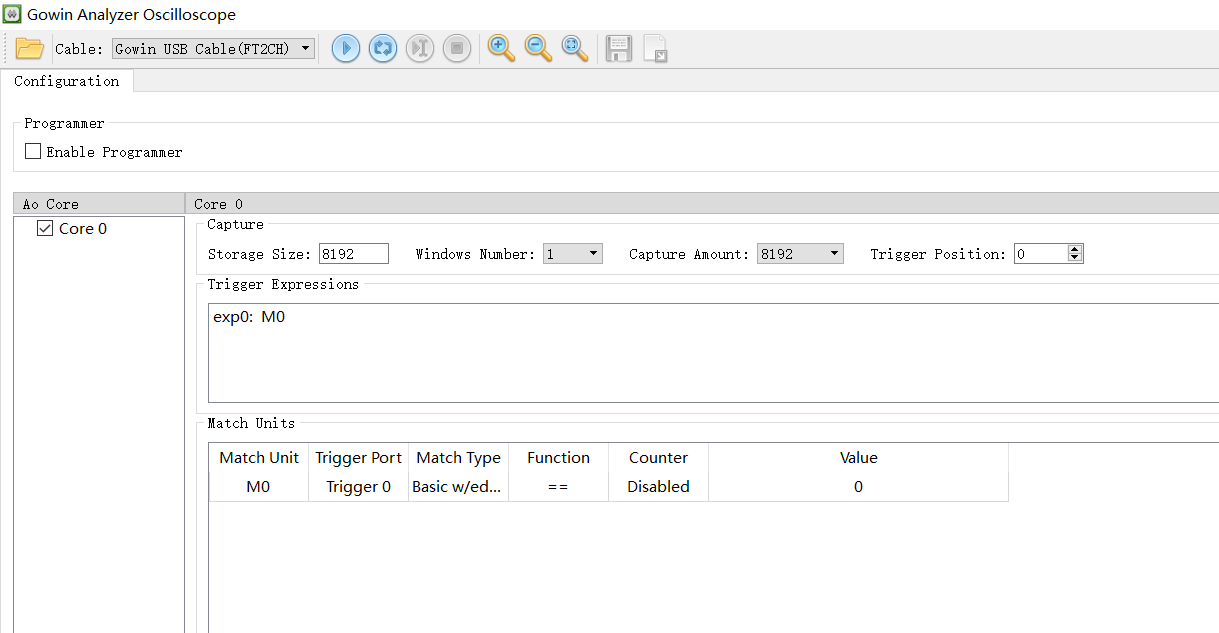

7. 打开GAO工具选择工具->GAO,打开逻辑分析仪上位机界面。

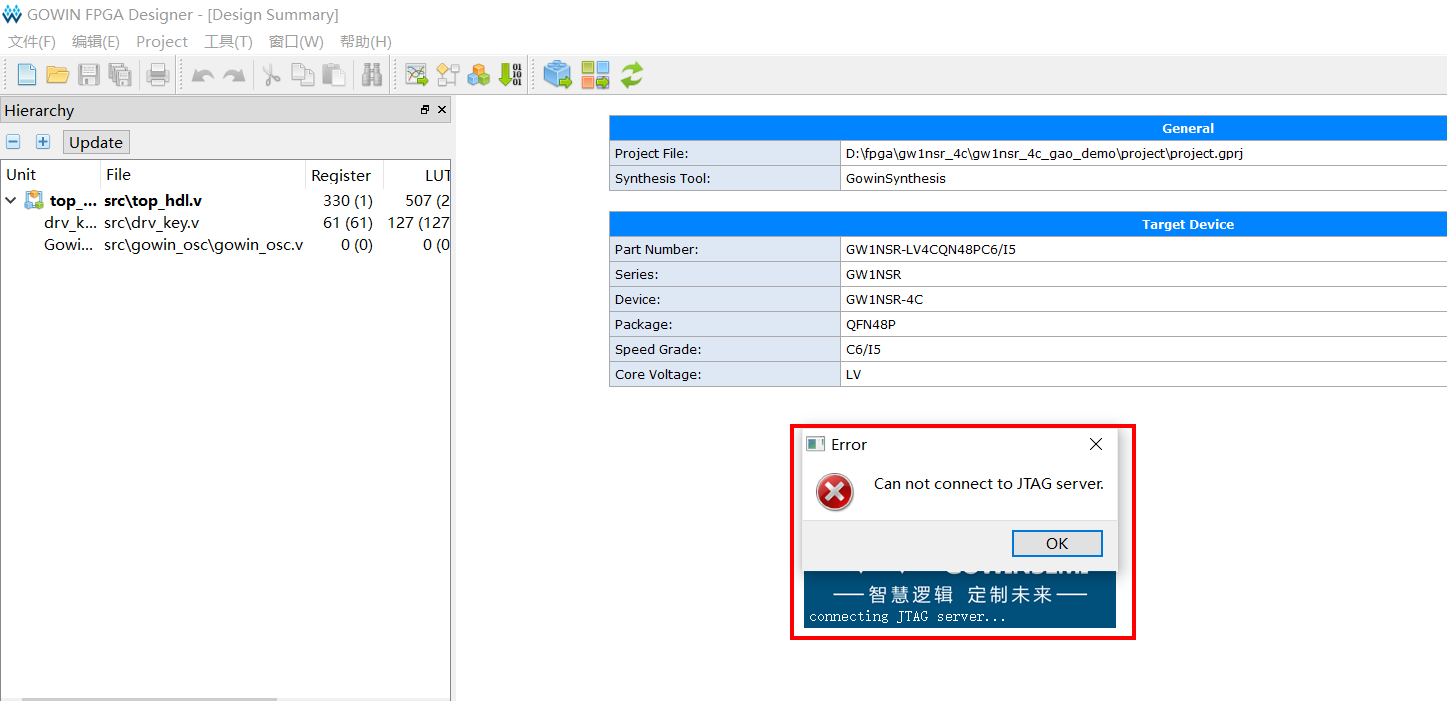

如果使用的是TangNano配套的Programmer工具,可以下载程序,但是打开GAO会提示Can not connect to JTAG server连接失败。

需要到高云官网下载独立的下载工具(EDU版本):

http://cdn.gowinsemi.com.cn/programmer1.9.8.07(build20620-1)_EDU.Win32.x86.zip下载完成后,替换原来的Programmer文件夹,再次打开就正常了。

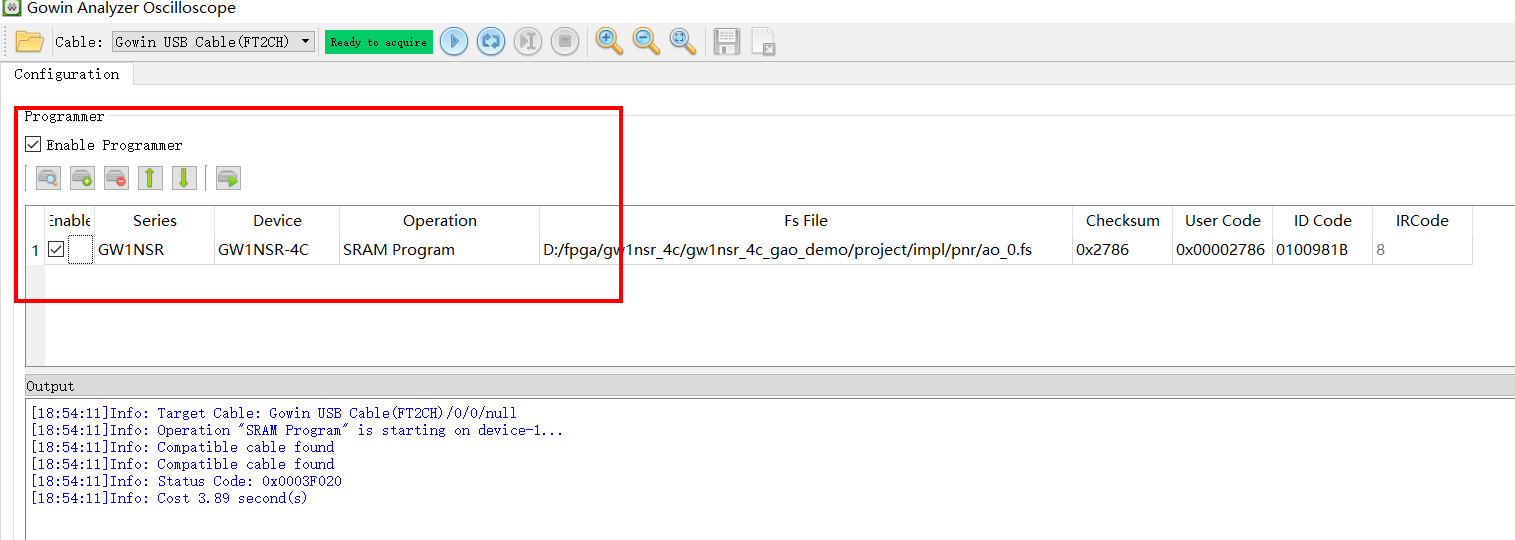

先下载fs程序文件。

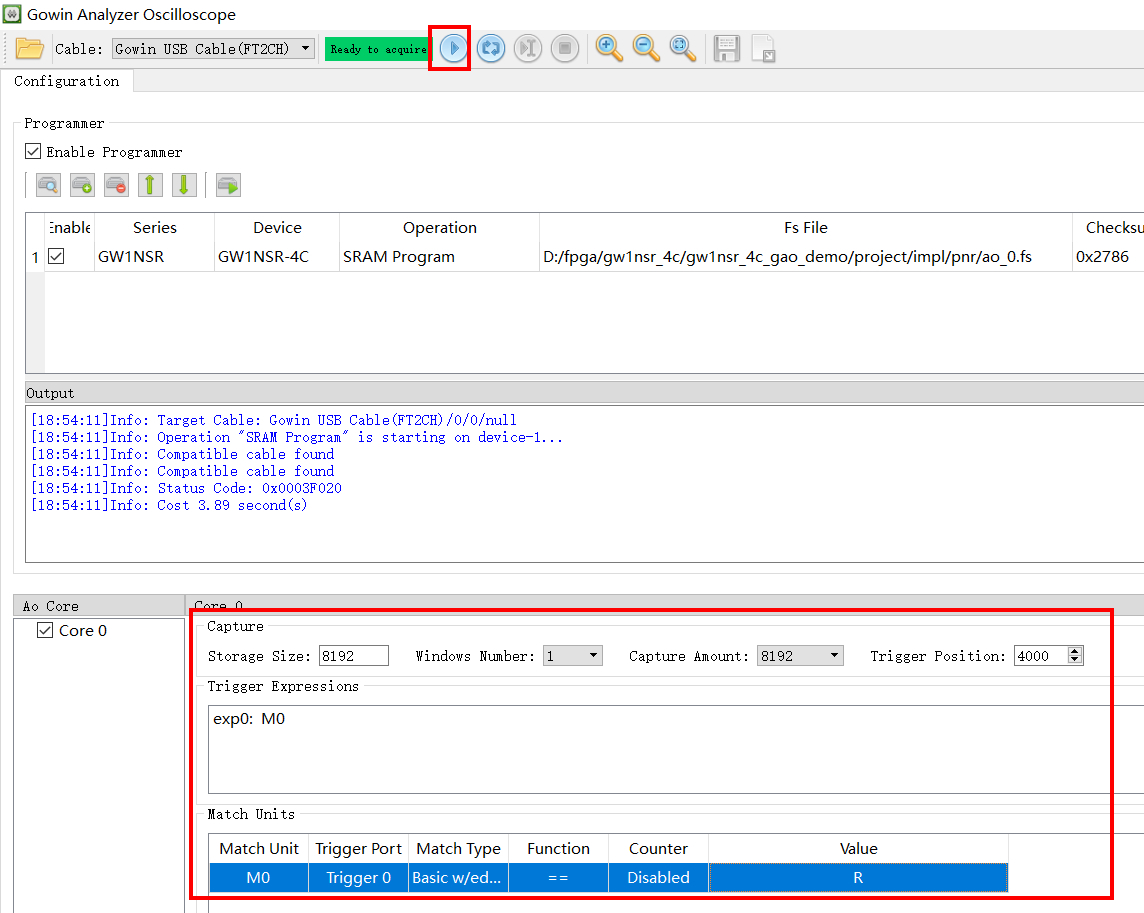

设置触发条件,并启动逻辑分析仪

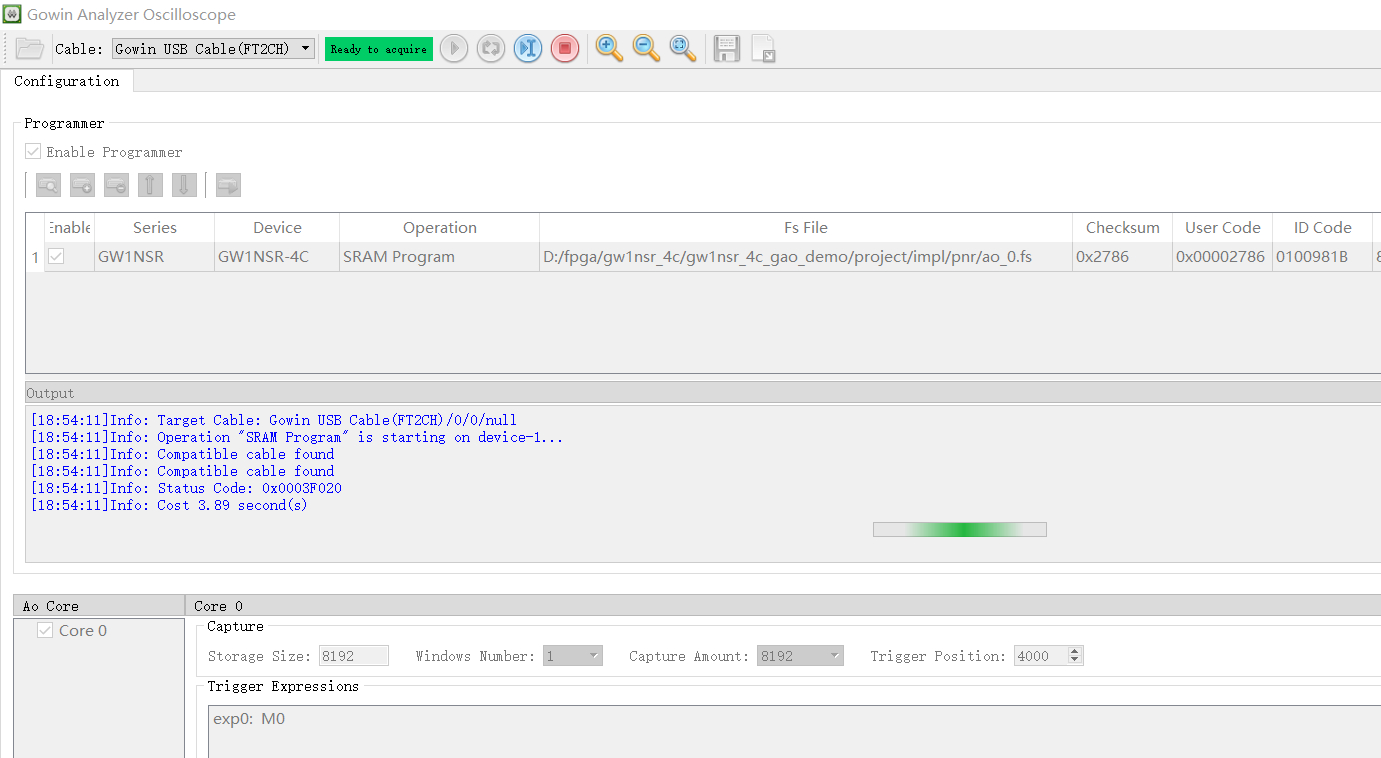

等待触发。

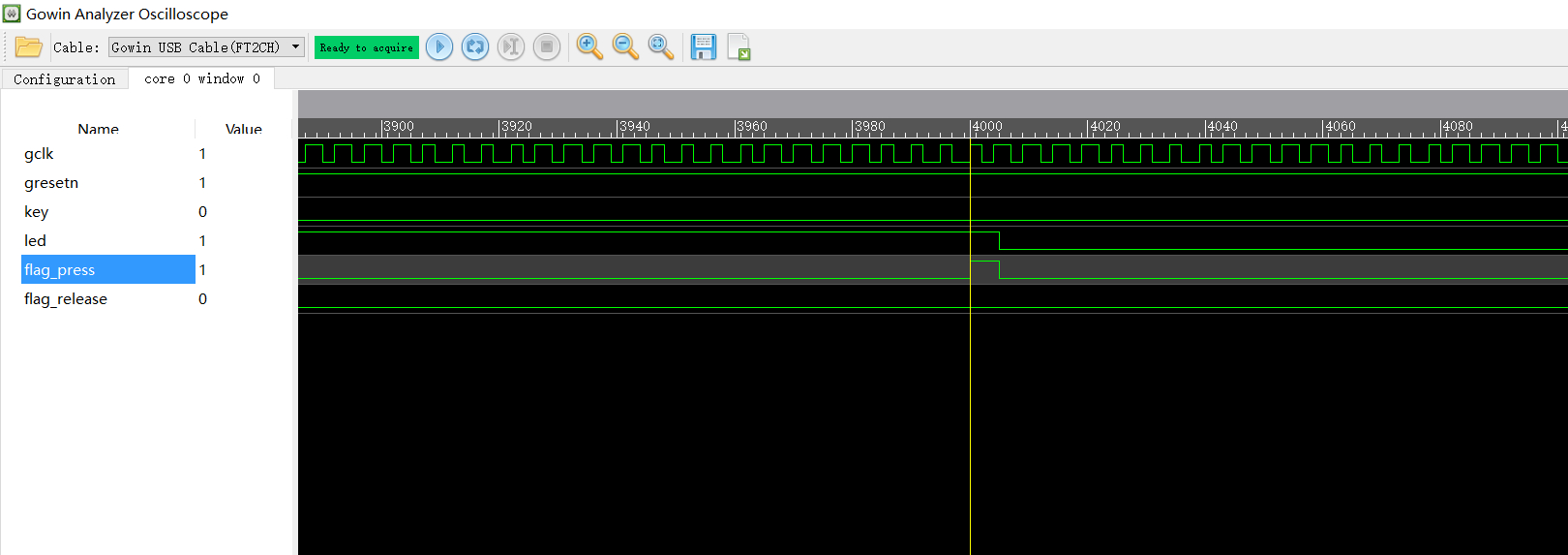

按下按键并松开,可以看到产生了按键按下的高脉冲信号,同时LED状态翻转。

8. 波形文件的导出

8. 波形文件的导出

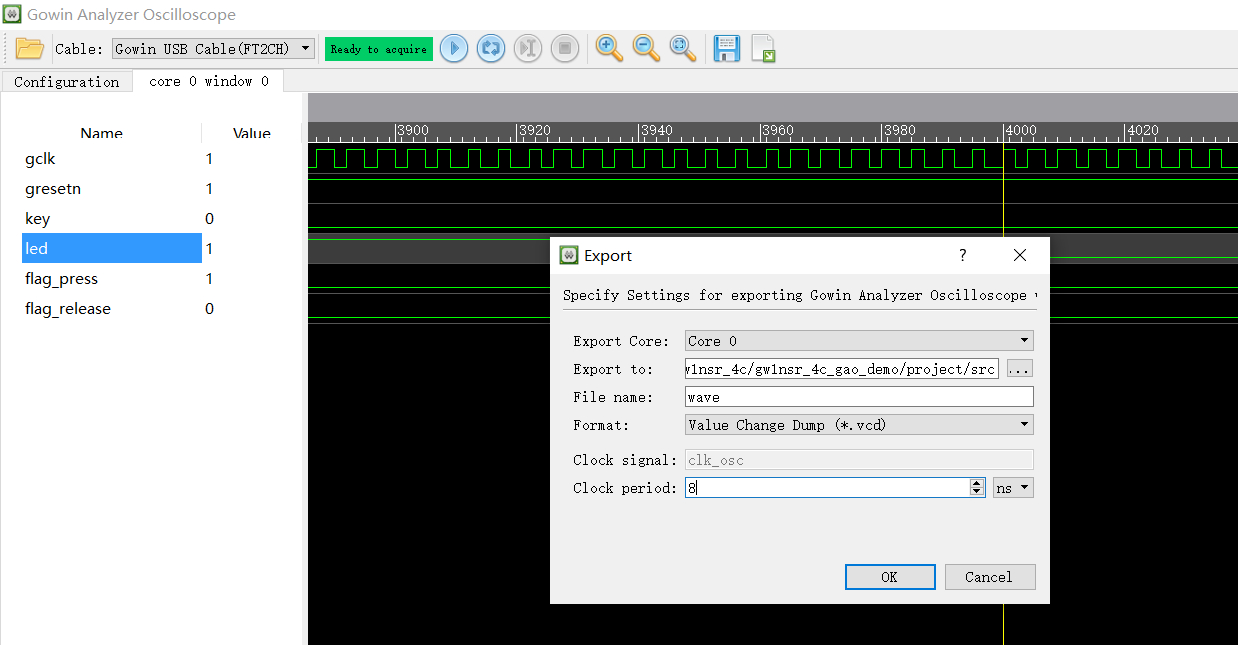

支持导出csv、prn和vcd格式的波形文件,前两种数据可以使用MATLAB进行分析,vcd格式可以使用gtkwave或modelsim来打开。

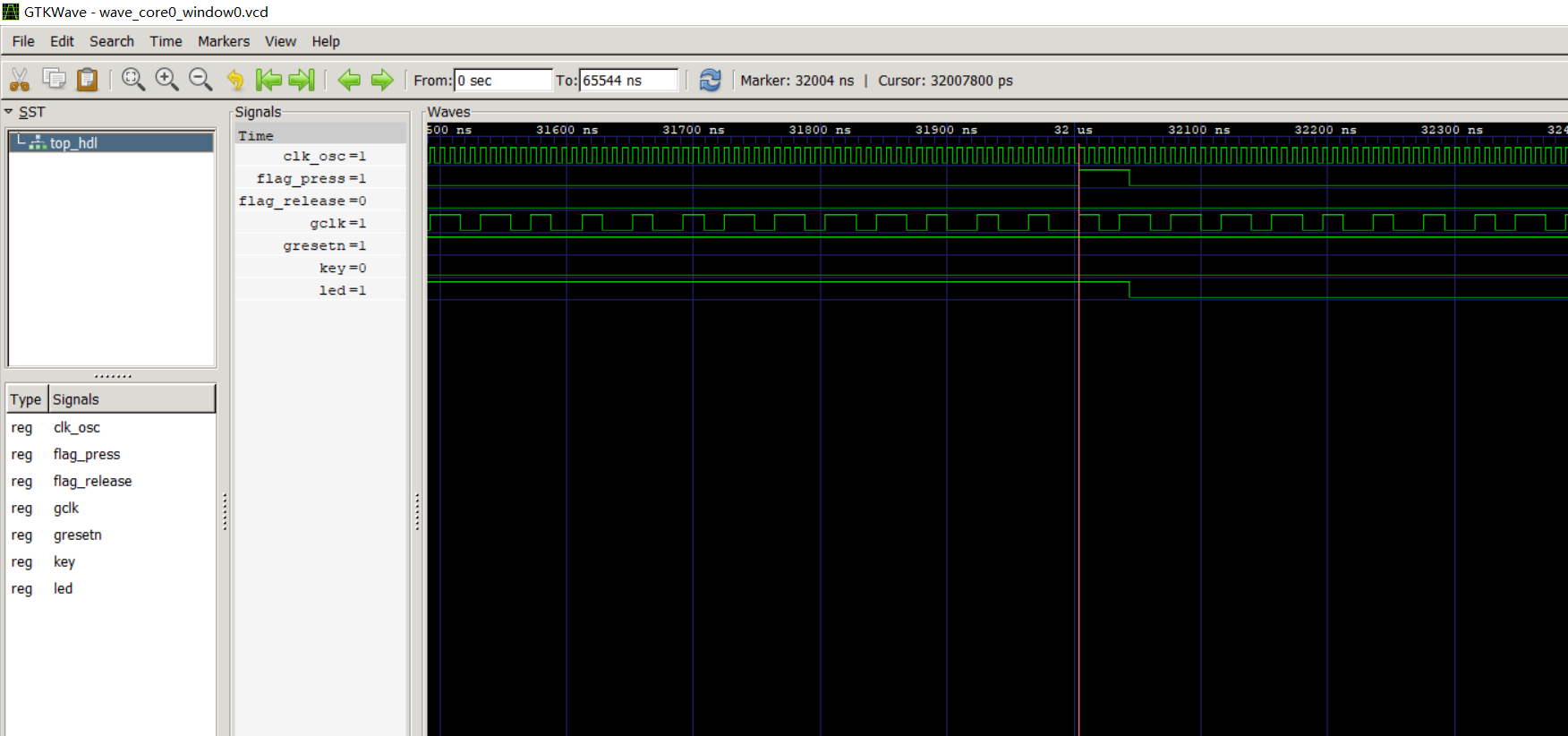

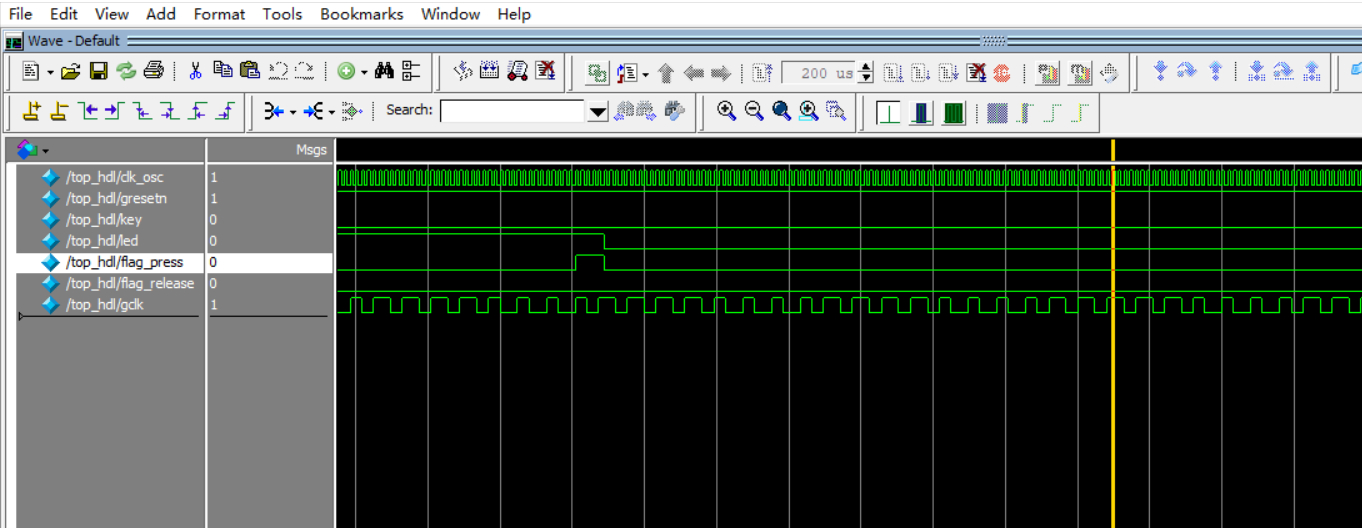

使用gtkwave直接打开文件波形

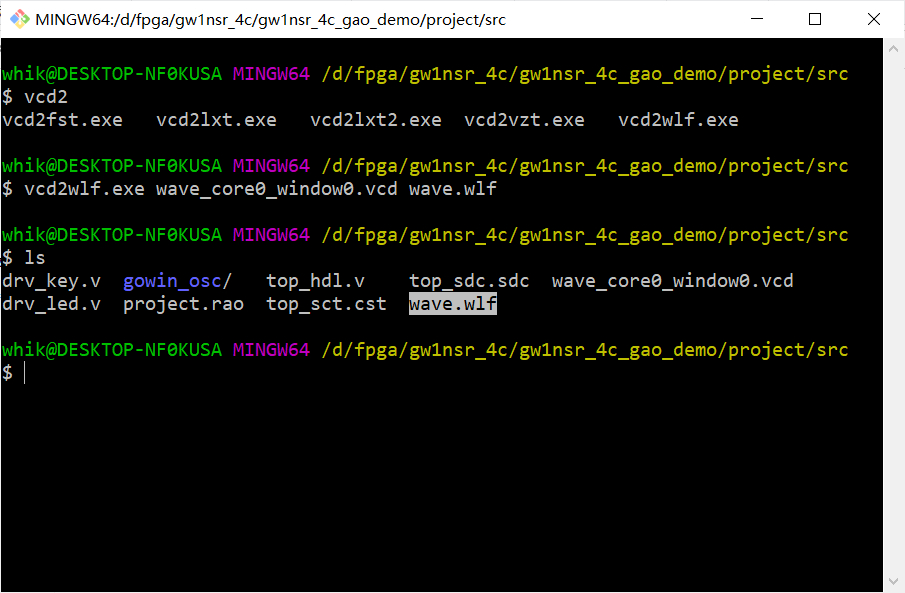

如果使用Modelsim打开,需要先将vcd转换为wlf格式,再使用Modelsim打开。

Modelsim打开wlf文件

9. 工程下载

9. 工程下载

作者: whik, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3887760.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

乖乖兔爸爸 2022-10-10 09:57

HUANGPING 2022-10-10 08:41

yzw92 2022-10-9 06:46