本文是高云FPGA学习笔记系列的第3篇文章,首发于面包板社区:

介绍完高云FPGA开发板,高云FPGA开发环境搭建之后,接下来才是真正的高云FPGA实战开发,如果你有国外FPGA芯片的使用经验,那么对于高云FPGA的使用,也可以很快的上手。

本文介绍基于高云FPGA开发环境——云源软件的使用,介绍如何创建FPGA点灯工程、管脚分配、时钟约束、综合、布局布线、比特流文件生成、下载和固化。

1. 工程目录创建

为了规范的进行开发,建议按照如下文件结构对FPGA工程进行管理,先创建一个文件夹:gw1nsr_4c_fpga_demo,在这个文件夹下再创建以下文件夹:

- rtl:用于存放Verilog设计文件

- tb:用于存放仿真文件

- modelsim:由于云源软件不支持仿真,需要借助第三方仿真工具进行仿真,此文件夹用于存放modelsim工程文件

- mcu:用于存放MCU工程

- sct:用于存放约束文件,如管脚约束,时钟约束等

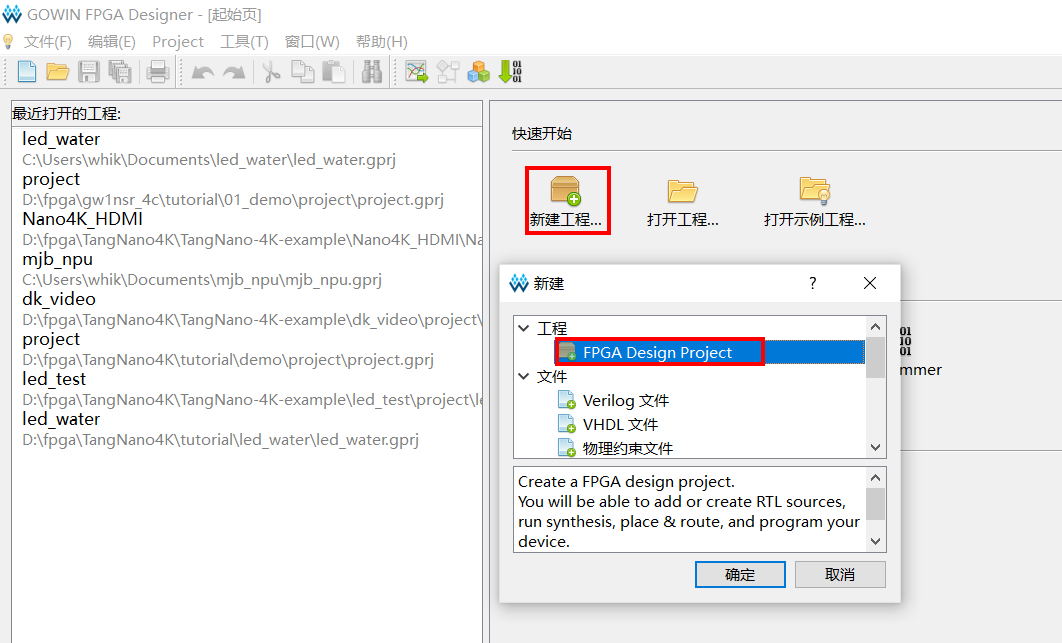

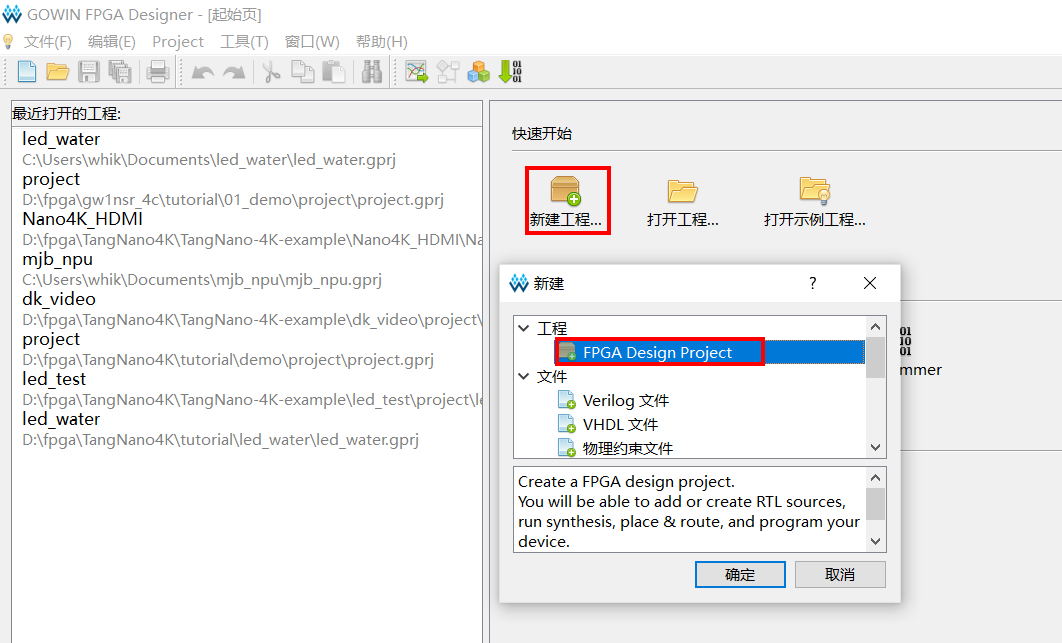

2. 新建工程

打开高云云源软件教育版,点击新建工程,或者直接按下Ctrl+N快捷键,打开工程创建向导。

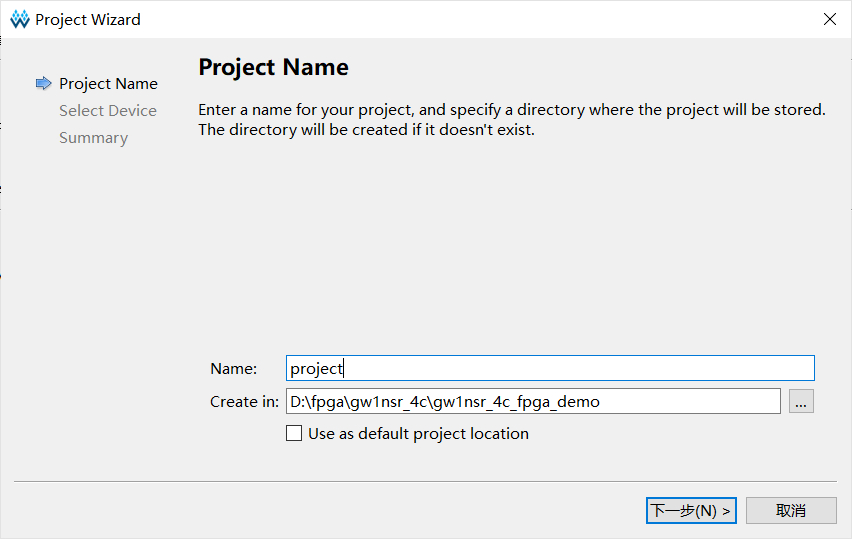

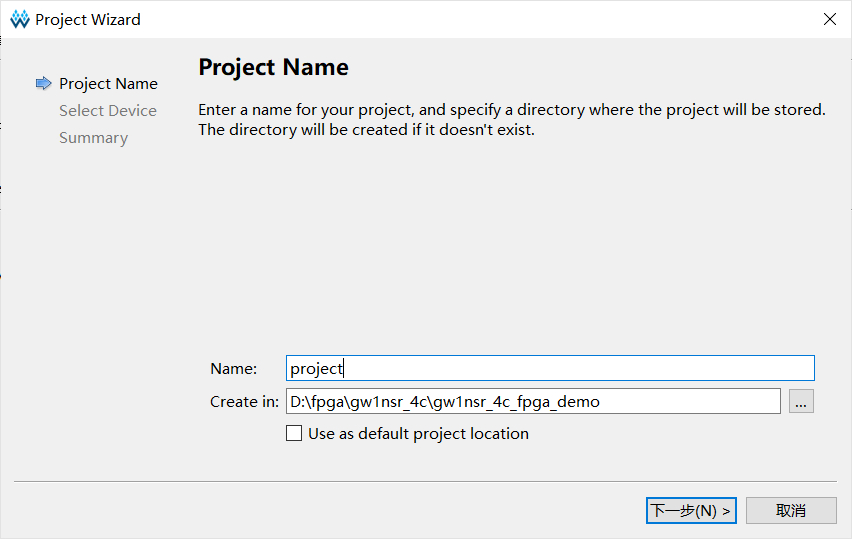

输入工程名称:project,保存路径选择之前创建的gw1nsr_4c_fpga_demo,创建工程的同时,会创建一个和工程名称相同的project文件夹。

以后就可以直接打开project目录下的gprj后缀的工程文件。

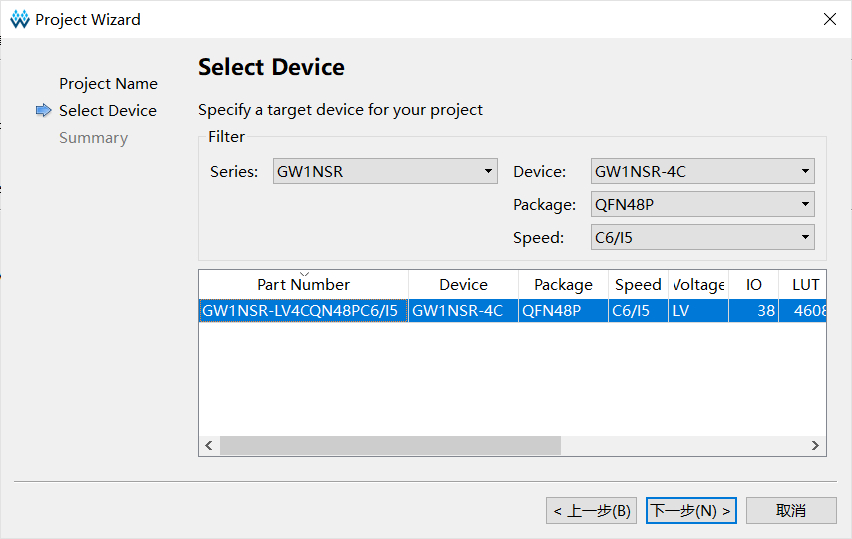

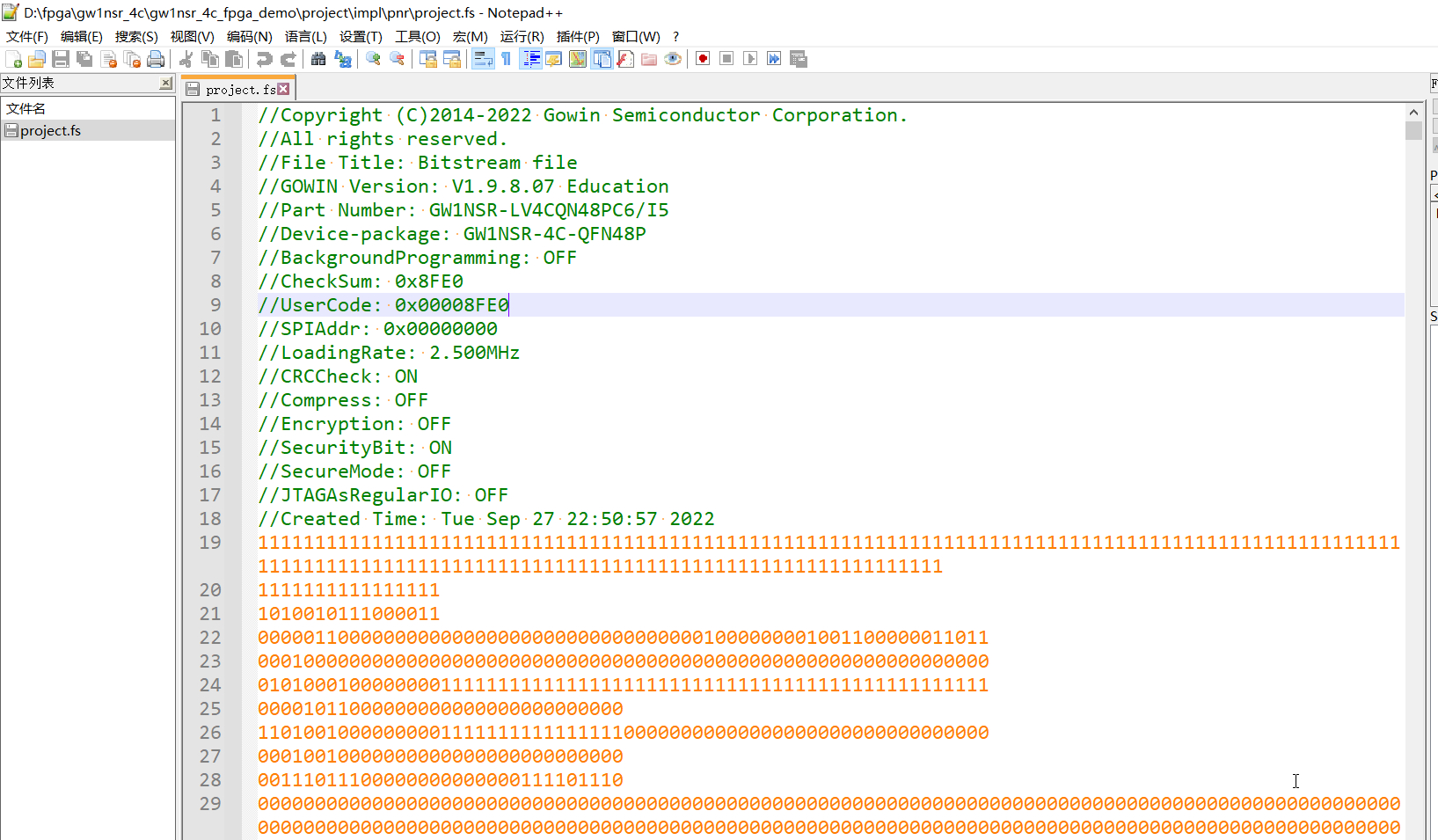

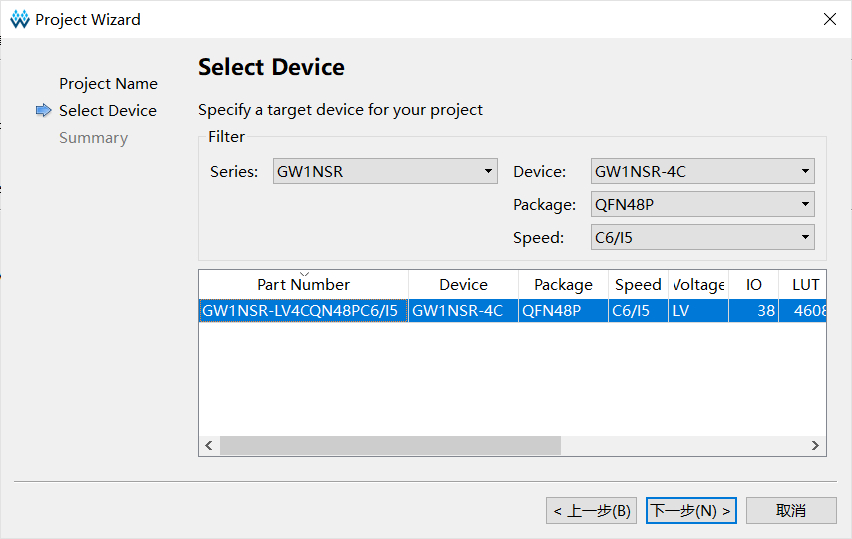

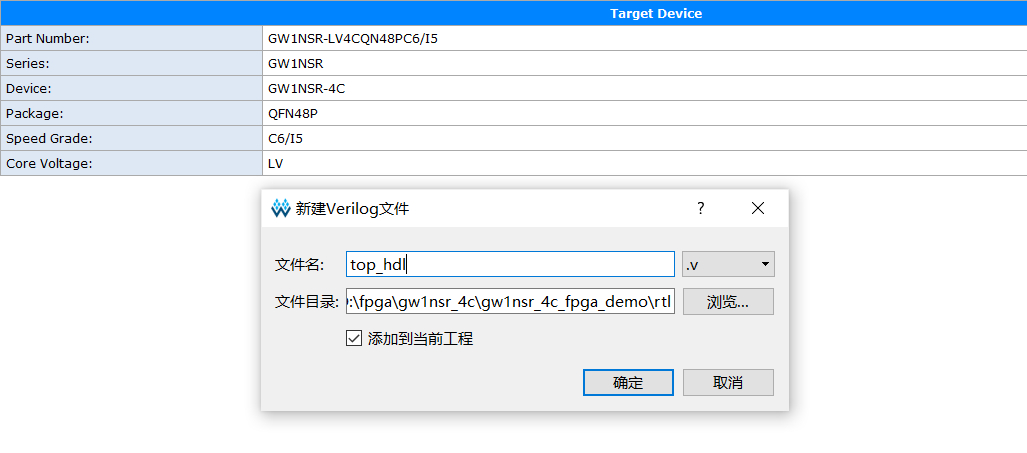

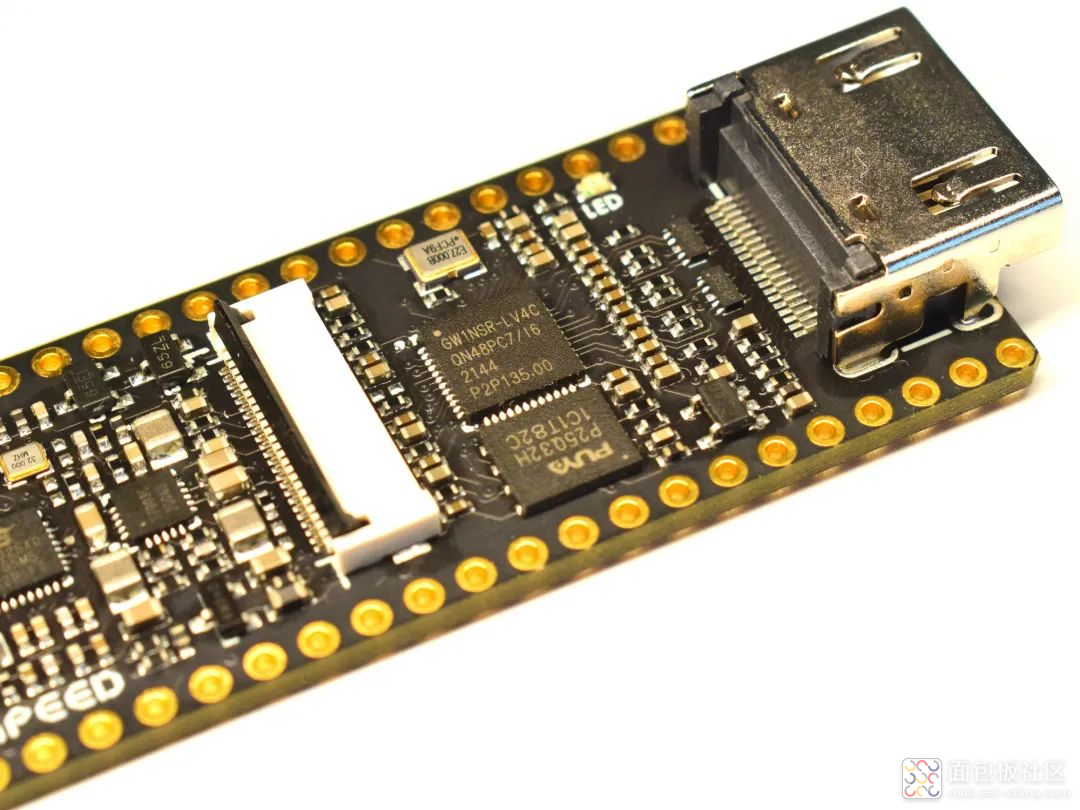

选择芯片型号:GW1NSR-4C

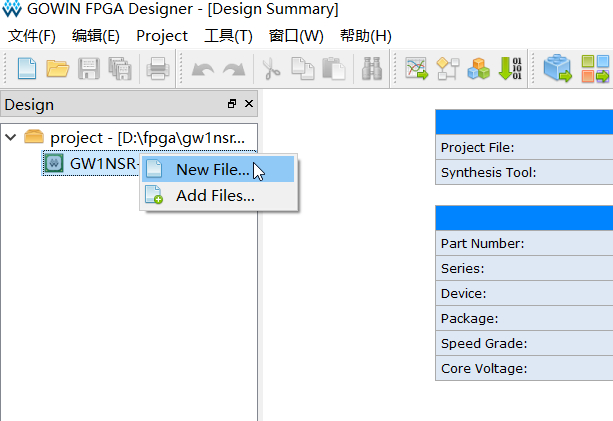

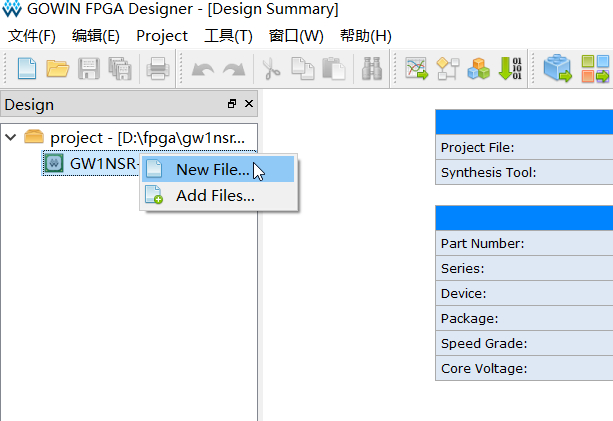

在工程上右键,选择New File,新建设计文件,在弹出的窗口,输入模块名top_hdl,文件类型根据需要选择,保存路径为之前创建的rtl文件夹。

勾选添加到当前工程

3. 设计输入

3. 设计输入

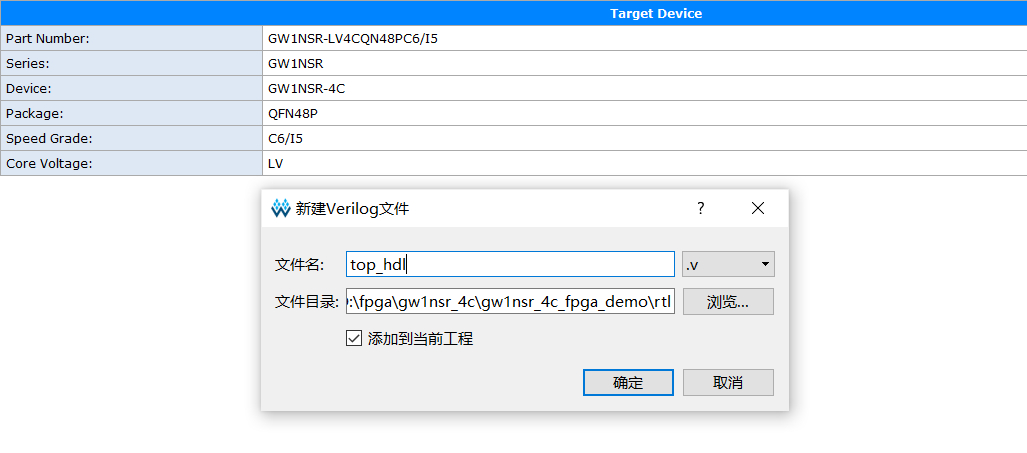

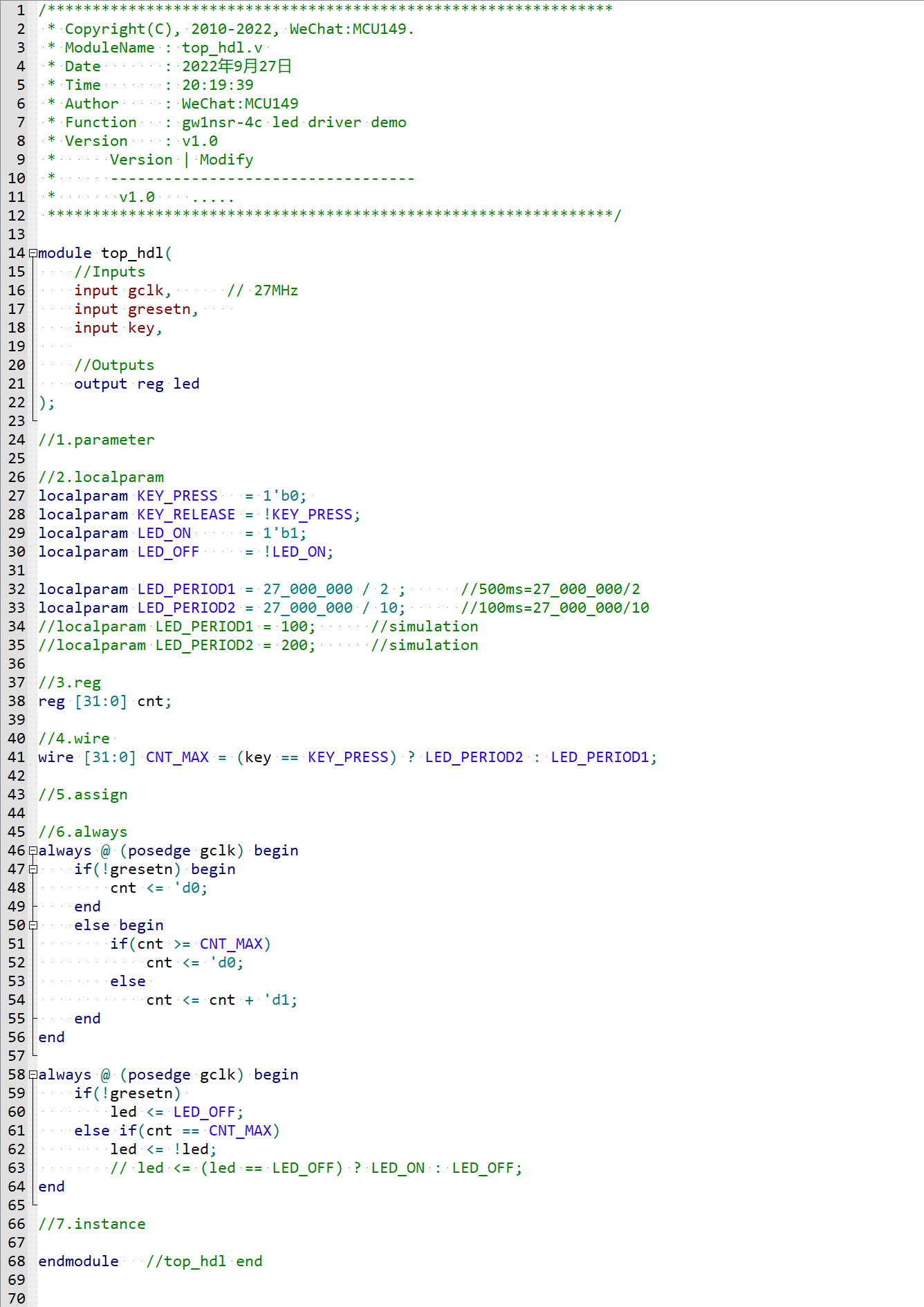

在云源软件编辑器中输入功能描述,本文以LED点灯为例,结合按键来控制闪烁频率。

实现的功能为:

- 对外部27MHz时钟信号进行计数,控制LED周期性闪烁。

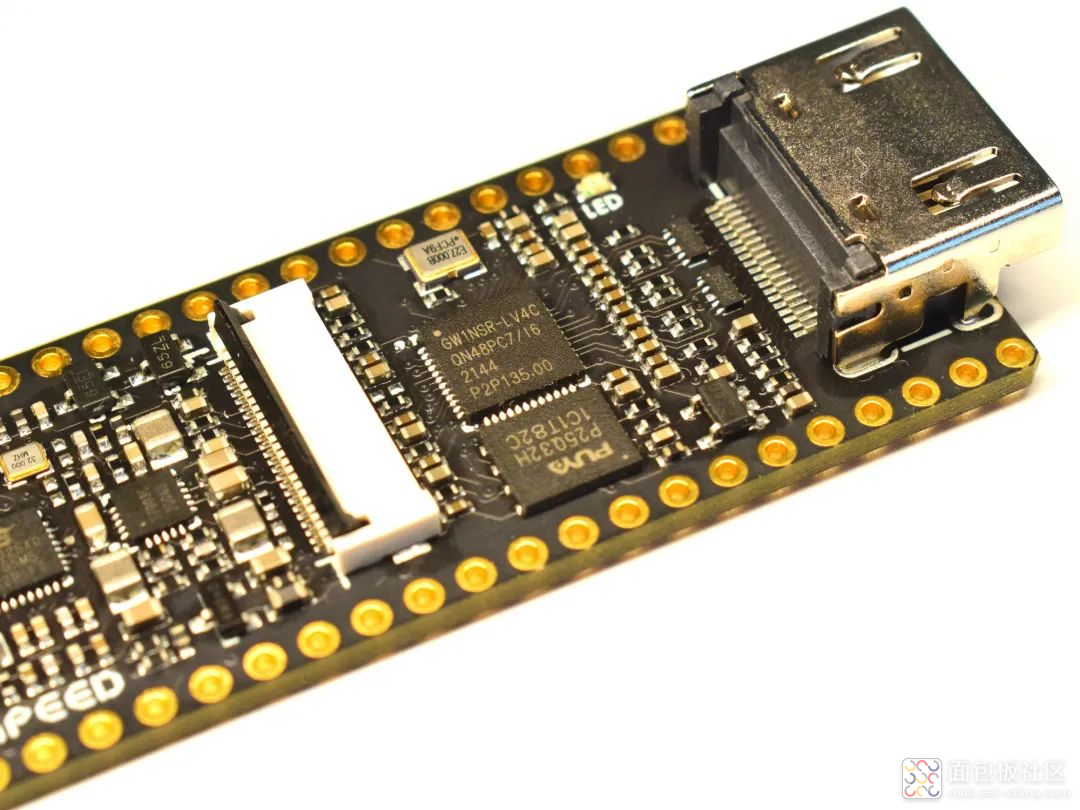

- TangNano 4K板载的两路按键,一路作为复位,一路作为用户按键。

- 用户按键未按下时,LED每500ms翻转一次状态。

- 用户按键被按下后,LED每100ms翻转一次状态。

Verilog源文件

/***************************************************************

* Copyright(C), 2010-2022, WeChat:MCU149

* ModuleName : top_hdl.v

* Date : 2022年9月27日

* Time : 20:19:39

* Author : WeChat:MCU149

* Function : gw1nsr-4c led driver demo

* Version : v1.0

* Version | Modify

* ----------------------------------

* v1.0 first version

***************************************************************/

module top_hdl(

//Inputs

input gclk, // 27MHz

input gresetn,

input key,

//Outputs

output reg led

);

//1.parameter

//2.localparam

localparam KEY_PRESS = 1'b0;

localparam KEY_RELEASE = !KEY_PRESS;

localparam LED_ON = 1'b1;

localparam LED_OFF = !LED_ON;

localparam LED_PERIOD1 = 27_000_000 / 2 ; //500ms=27_000_000/2

localparam LED_PERIOD2 = 27_000_000 / 10; //100ms=27_000_000/10

//localparam LED_PERIOD1 = 100; //simulation

//localparam LED_PERIOD2 = 200; //simulation

//3.reg

reg [31:0] cnt;

//4.wire

wire [31:0] CNT_MAX = (key == KEY_PRESS) ? LED_PERIOD2 : LED_PERIOD1;

//5.assign

//6.always

always @ (posedge gclk) begin

if(!gresetn) begin

cnt <= 'd0;

end

else begin

if(cnt >= CNT_MAX)

cnt <= 'd0;

else

cnt <= cnt + 'd1;

end

end

always @ (posedge gclk) begin

if(!gresetn)

led <= LED_OFF;

else if(cnt == CNT_MAX)

led <= !led;

// led <= (led == LED_OFF) ? LED_ON : LED_OFF;

end

//7.instance

endmodule //top_hdl end

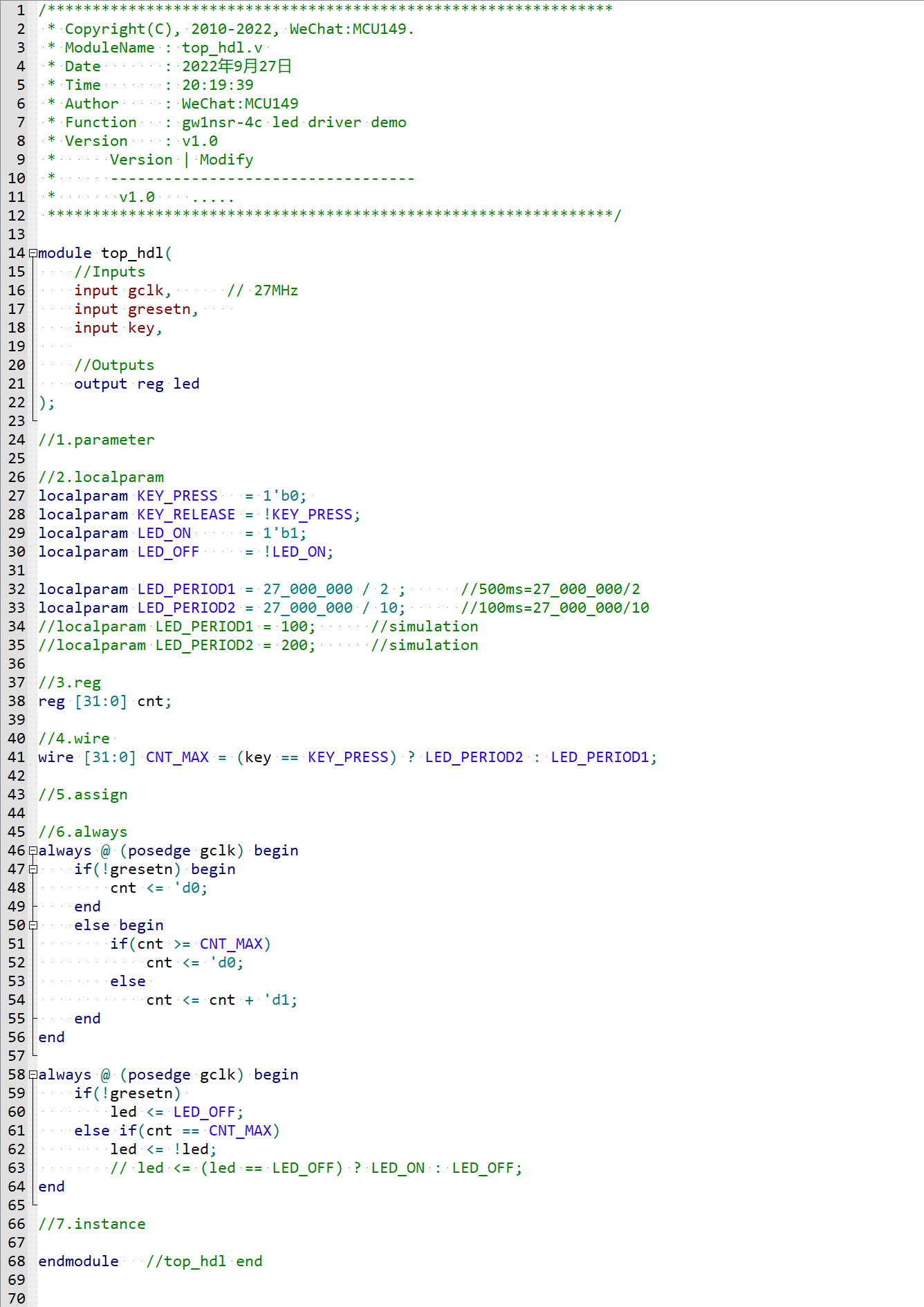

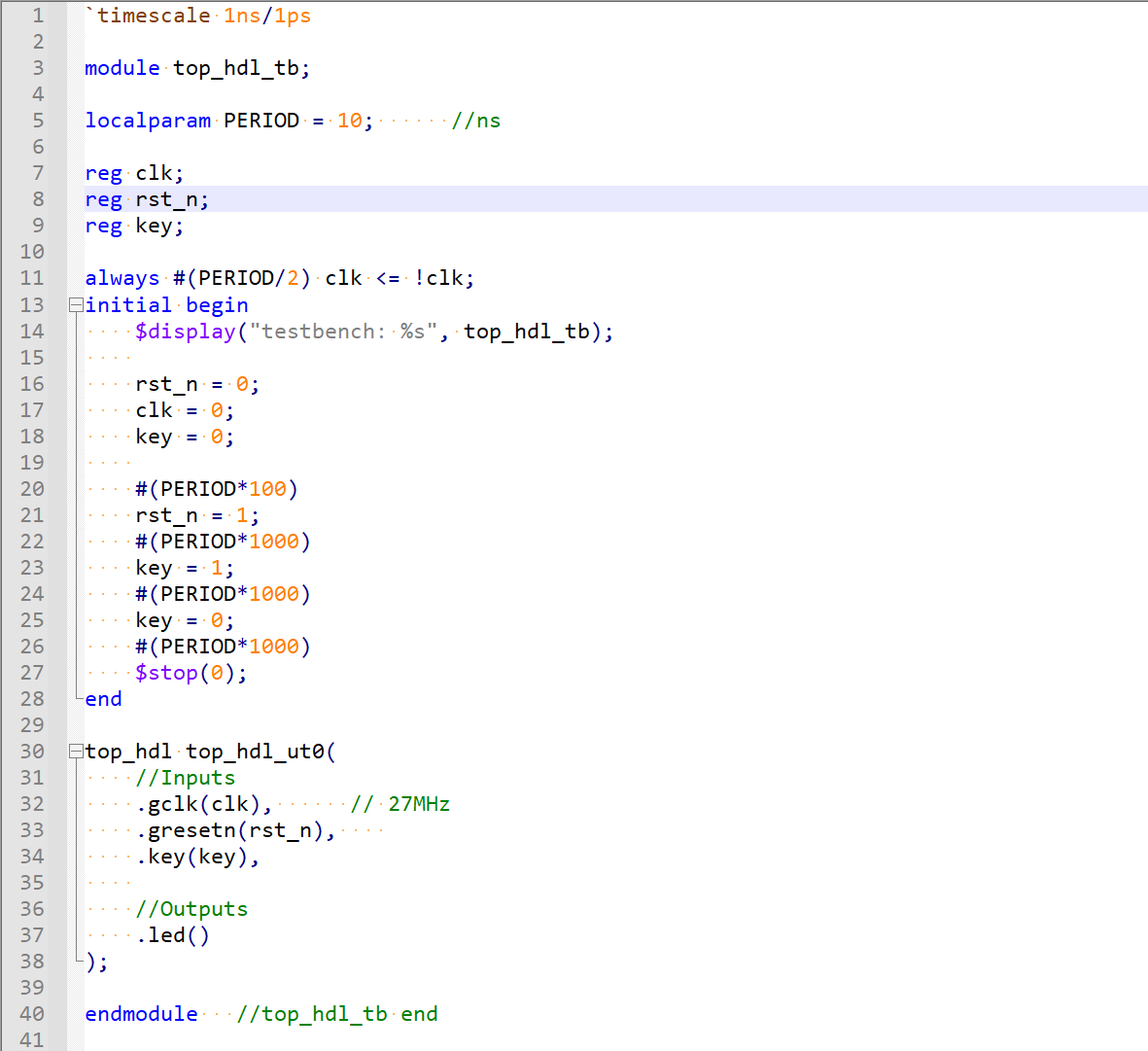

Testbench仿真文件:

`timescale 1ns/1ps

module top_hdl_tb;

localparam PERIOD = 10; //ns

reg clk;

reg rst_n;

reg key;

always #(PERIOD/2) clk <= !clk;

initial begin

$display("testbench: %s", top_hdl_tb);

rst_n = 0;

clk = 0;

key = 0;

#(PERIOD*100)

rst_n = 1;

#(PERIOD*1000)

key = 1;

#(PERIOD*1000)

key = 0;

#(PERIOD*1000)

$stop(0);

end

top_hdl top_hdl_ut0(

//Inputs

.gclk(clk), // 27MHz

.gresetn(rst_n),

.key(key),

//Outputs

.led()

);

endmodule //top_hdl_tb end

源文件截图:

激励文件截图:

4. 设计仿真

4. 设计仿真

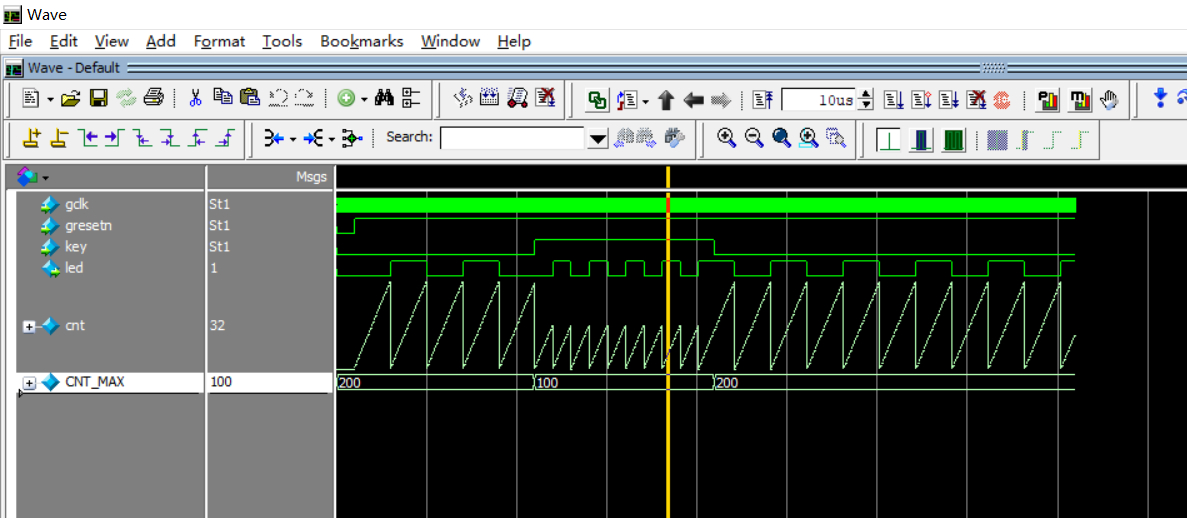

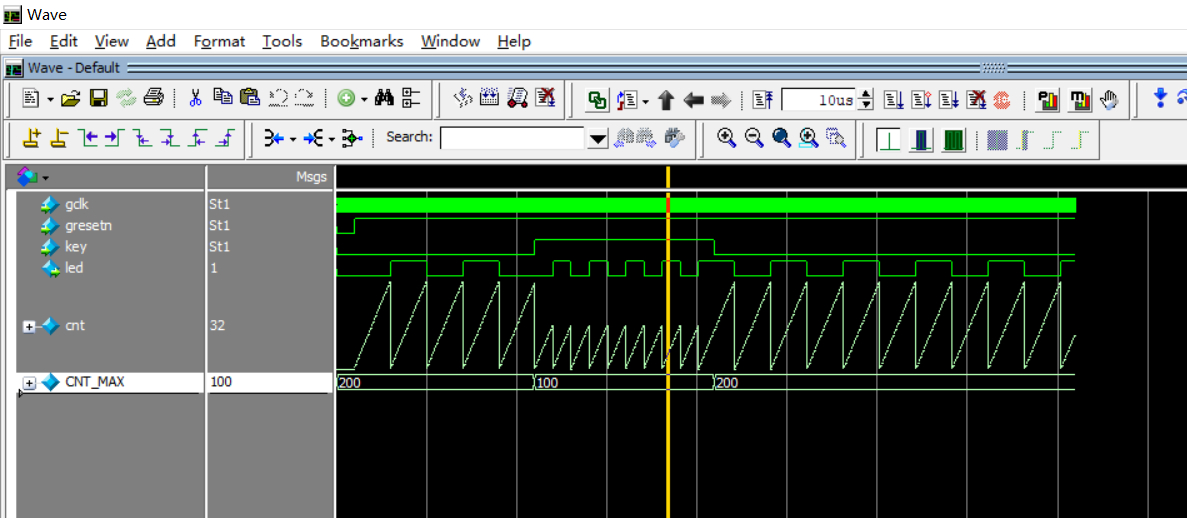

由于云源软件暂时不支持仿真功能,我们还需要借助第三方工具来完成功能仿真,这里我选择的是Modelsim,仿真的波形如下:

和我们的预期设计是一致的,为了缩短仿真时间,我把LED闪烁周期值减小了。

localparam LED_PERIOD1 = 27_000_000 / 2 ; //500ms=27_000_000/2

localparam LED_PERIOD2 = 27_000_000 / 10; //100ms=27_000_000/10

//localparam LED_PERIOD1 = 100; //simulation

//localparam LED_PERIOD2 = 200; //simulation

5. 综合

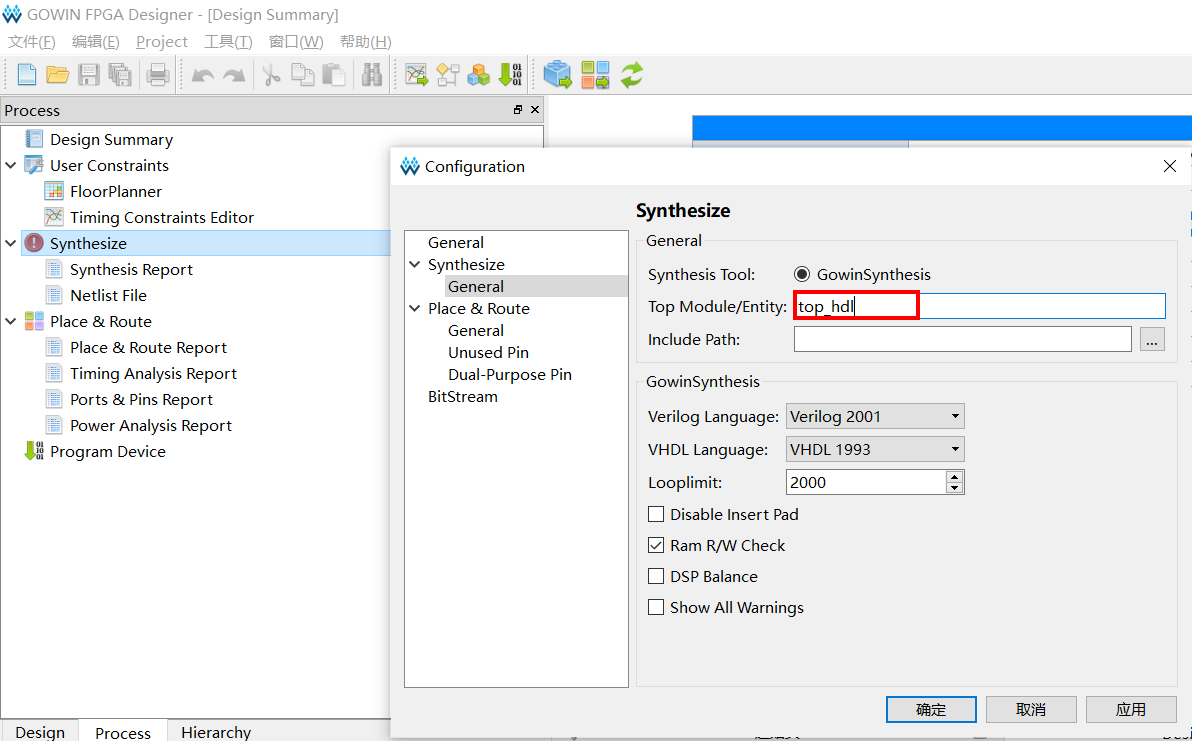

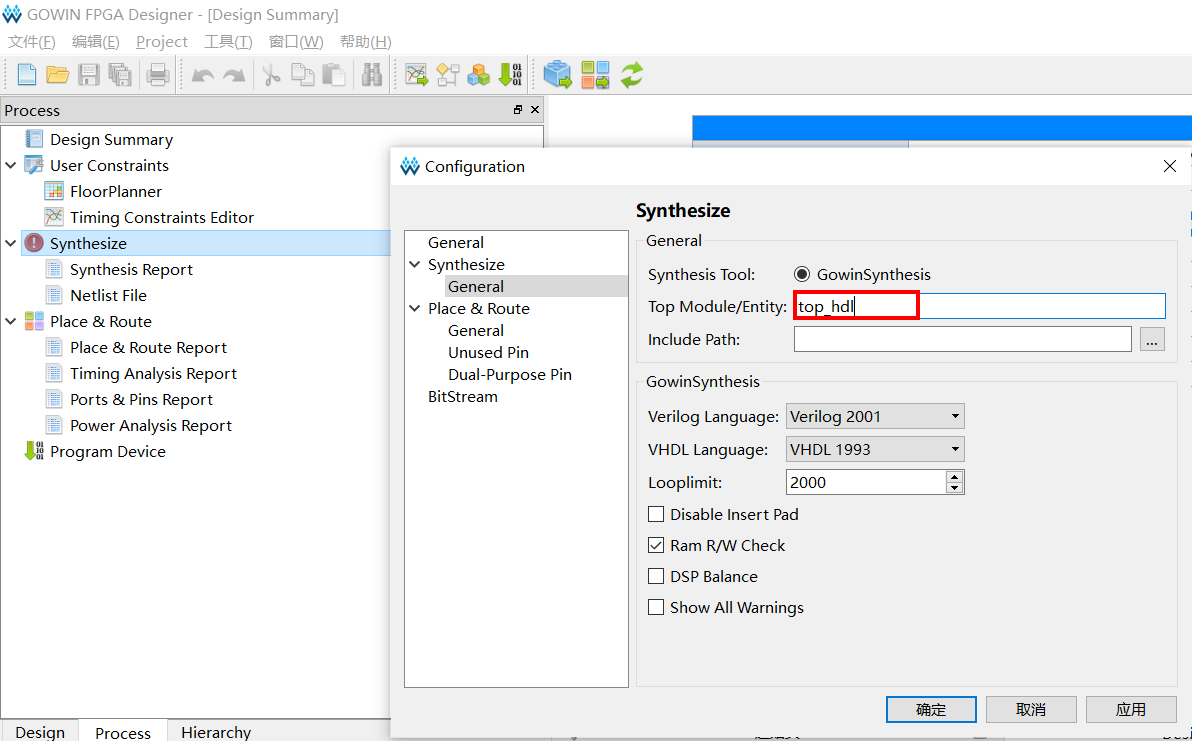

在进行管脚分配前,需要先进行综合,综合工具为高云自研GowinSynthesis工具,如果有多个设计文件,还需要指定顶层模块的名称,在综合选项右键点击Configuration

指定工程的顶层模块名称为:top_hdl

6. 管脚分配

6. 管脚分配

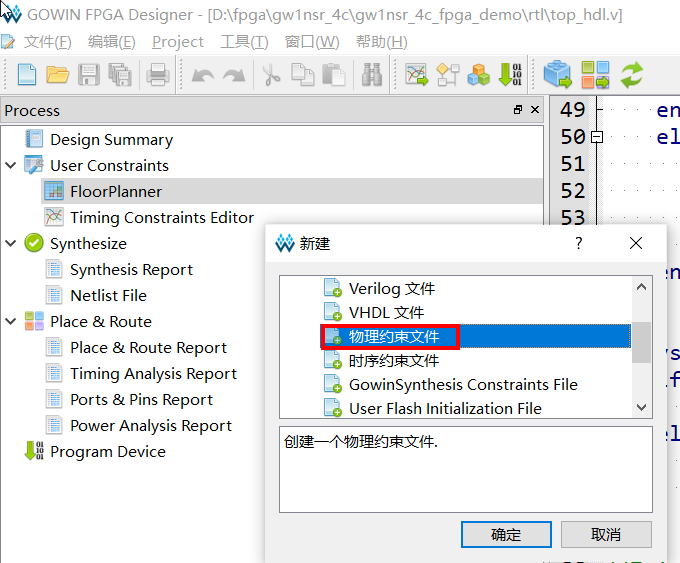

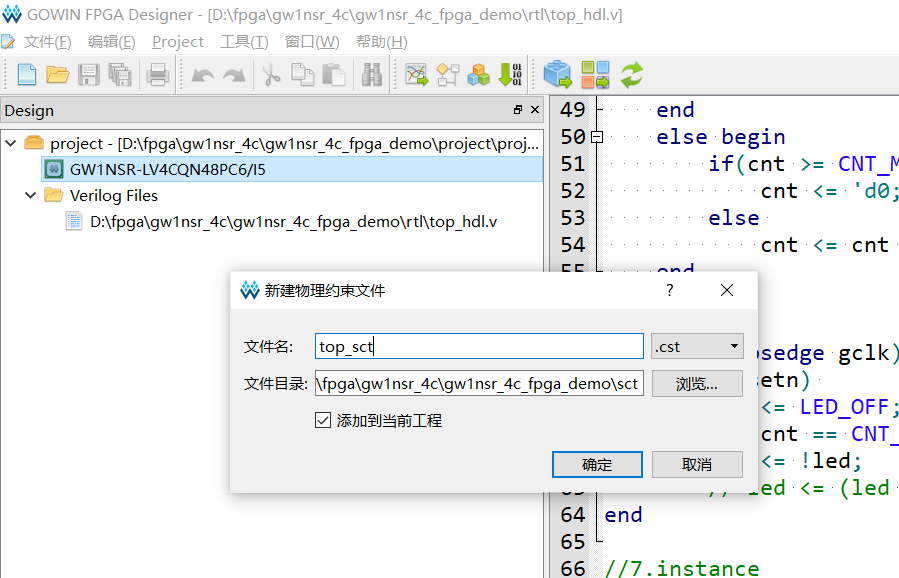

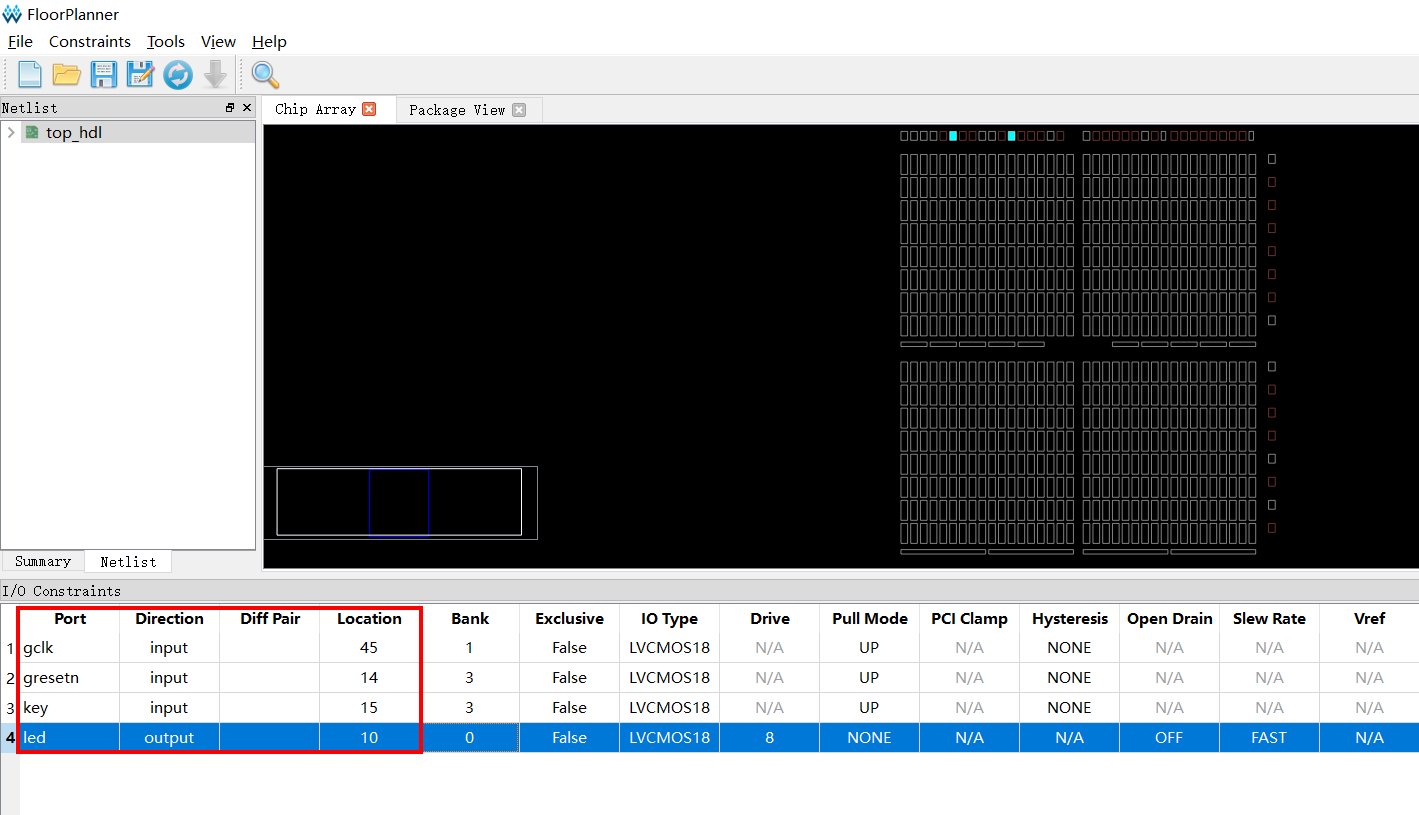

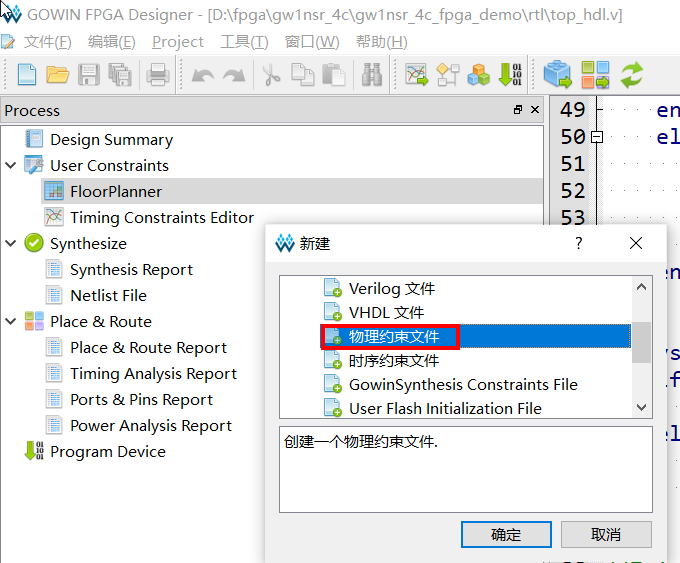

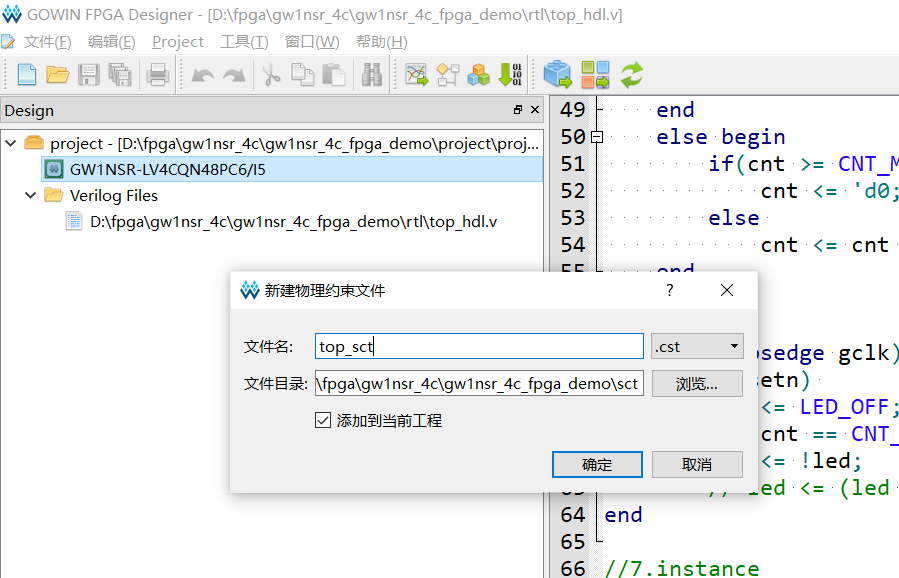

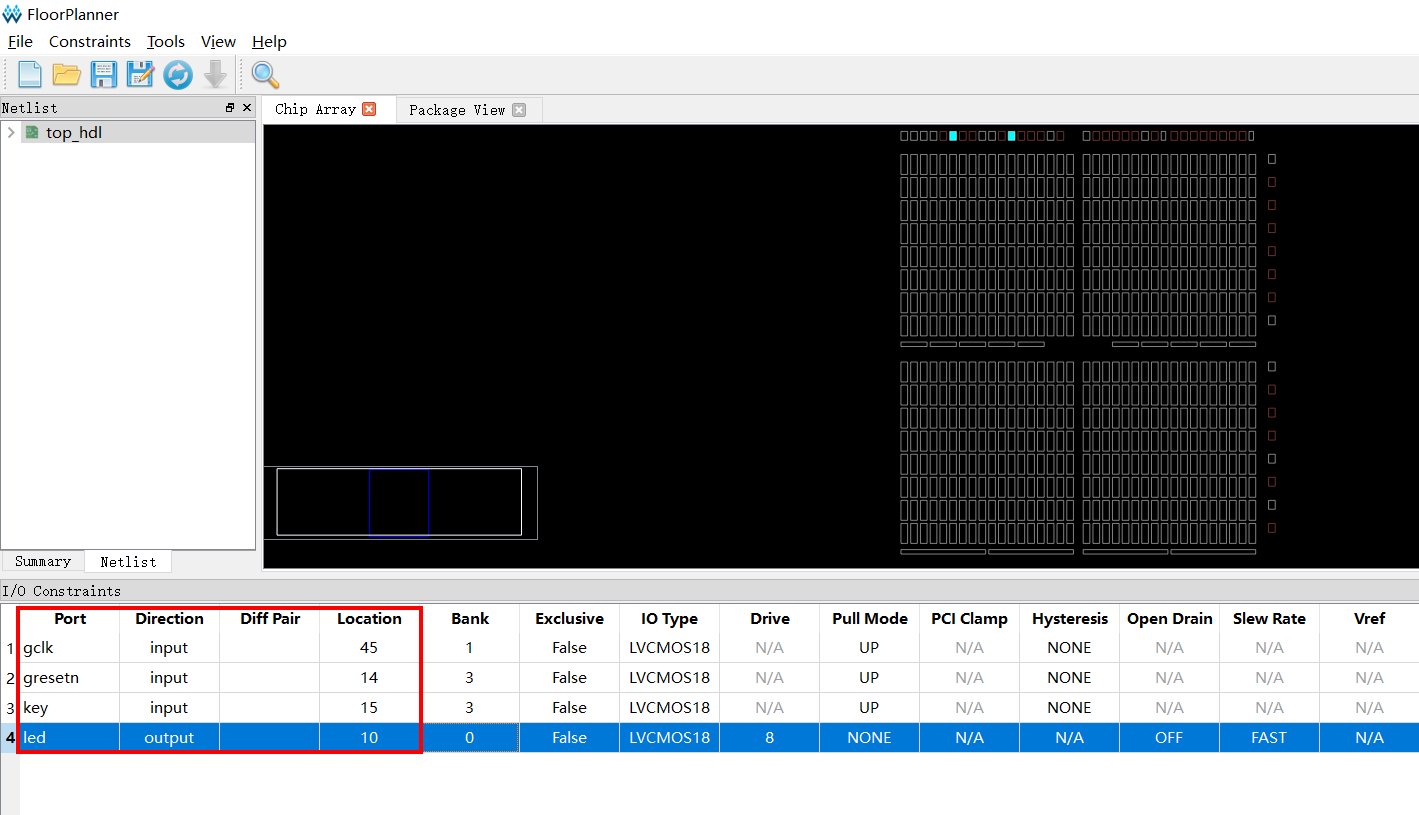

新建物理(管脚)约束文件,命名为top_sct,并保存到sct文件夹下。

输入管脚约束文件名。

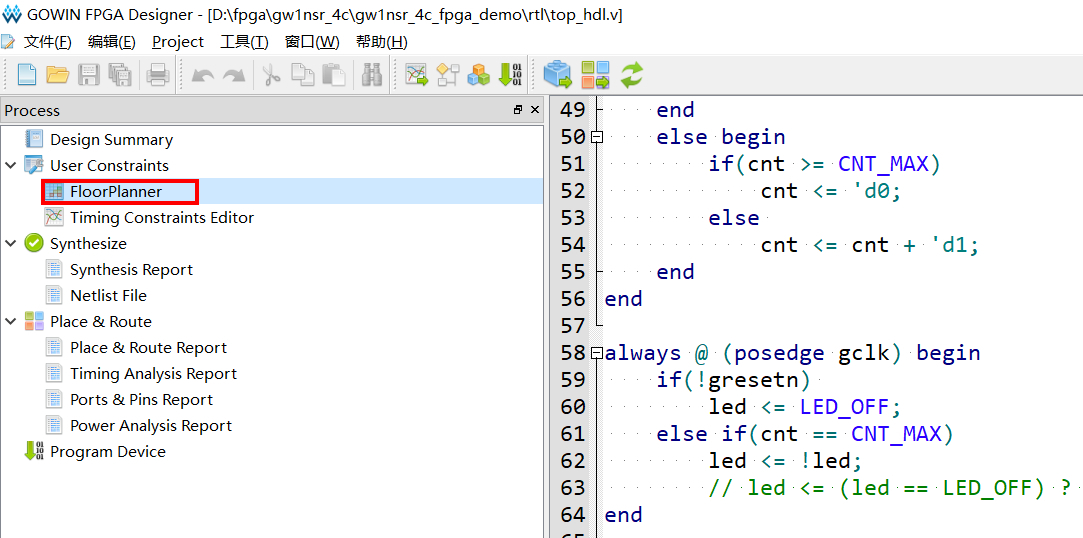

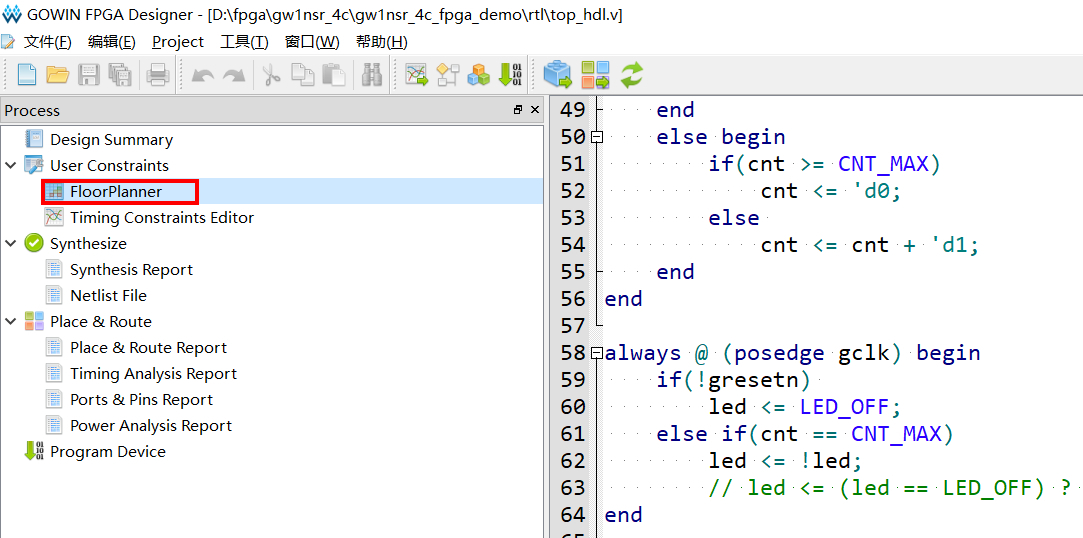

点击Floor Planner,打开图形化管脚分配工具。

分配管脚,和开发板上的管脚保持一致

或者直接输入约束语句:

IO_LOC

"led" 10;

IO_PORT

"led" PULL_MODE=NONE DRIVE=

8;

IO_LOC

"key" 15;

IO_PORT

"key" PULL_MODE=UP;

IO_LOC

"gresetn" 14;

IO_PORT

"gresetn" PULL_MODE=UP;

IO_LOC

"gclk" 45;

IO_PORT

"gclk" PULL_MODE=UP;

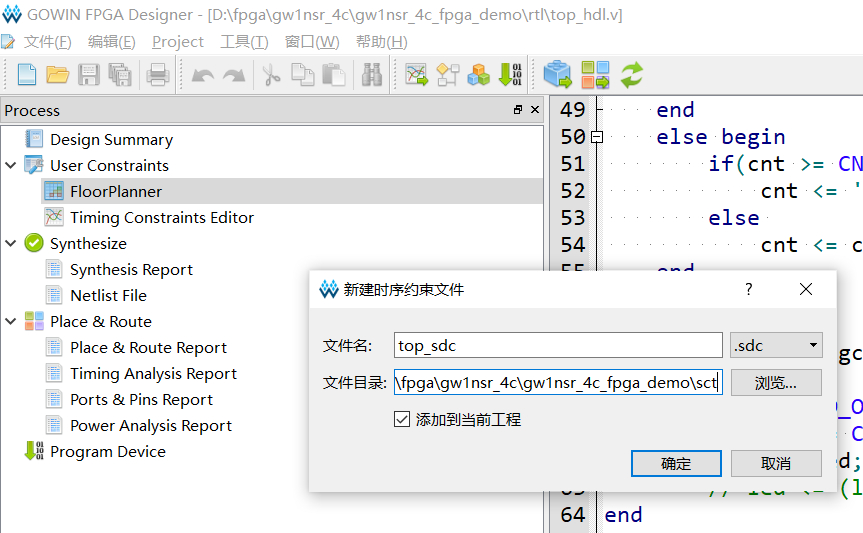

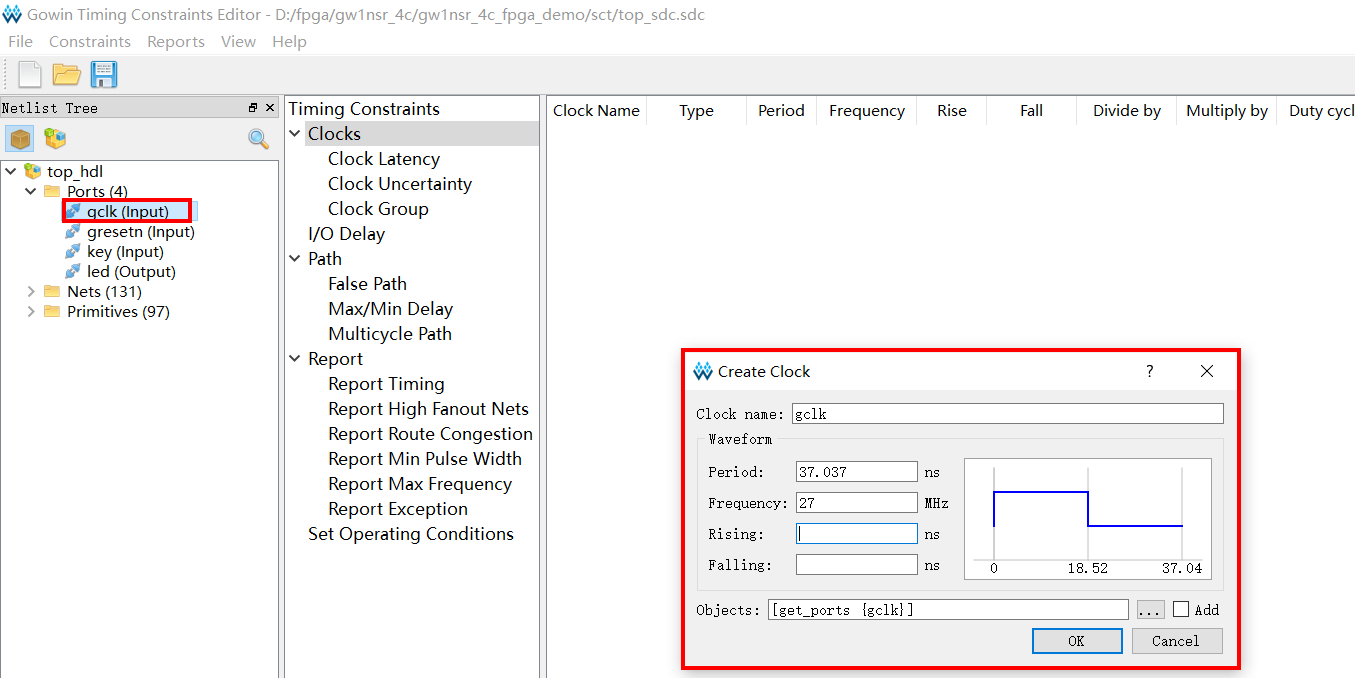

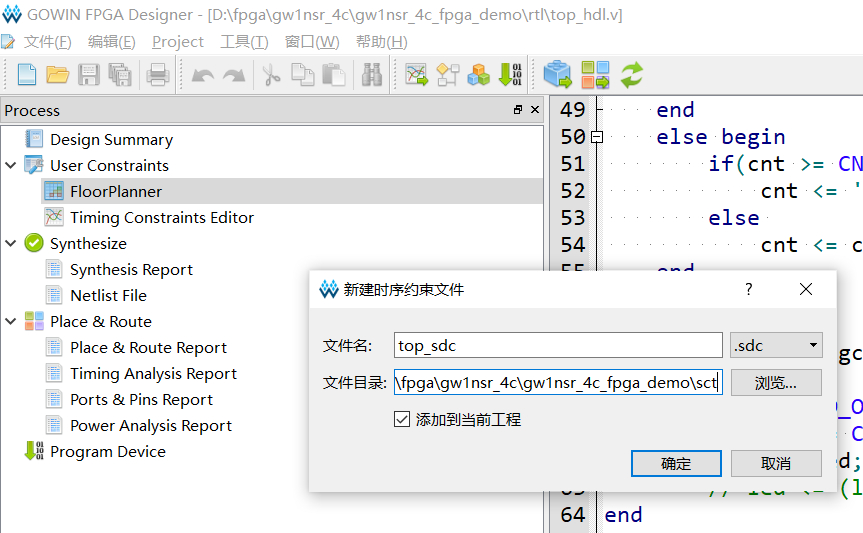

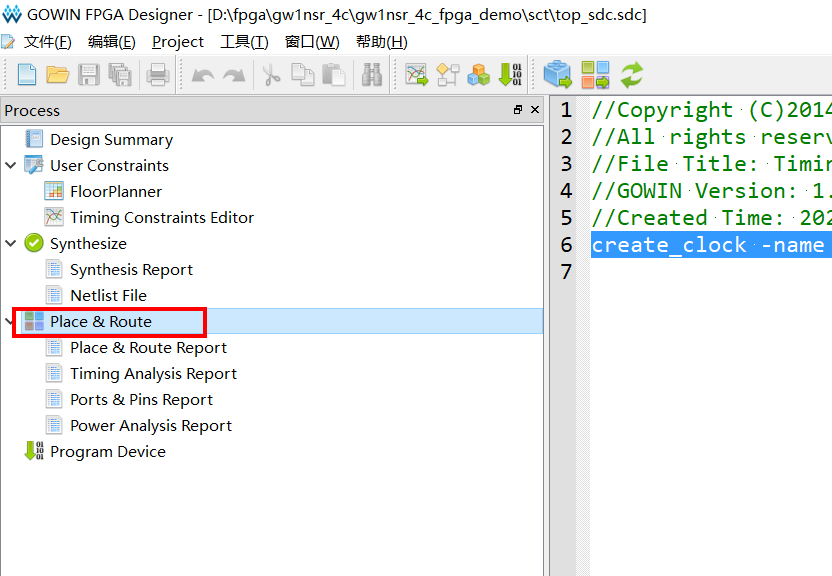

7. 时钟约束

时序约束不是必须要做,可以省略。

新建时序约束文件,命名为top_sdc,也保存到sct文件夹中。

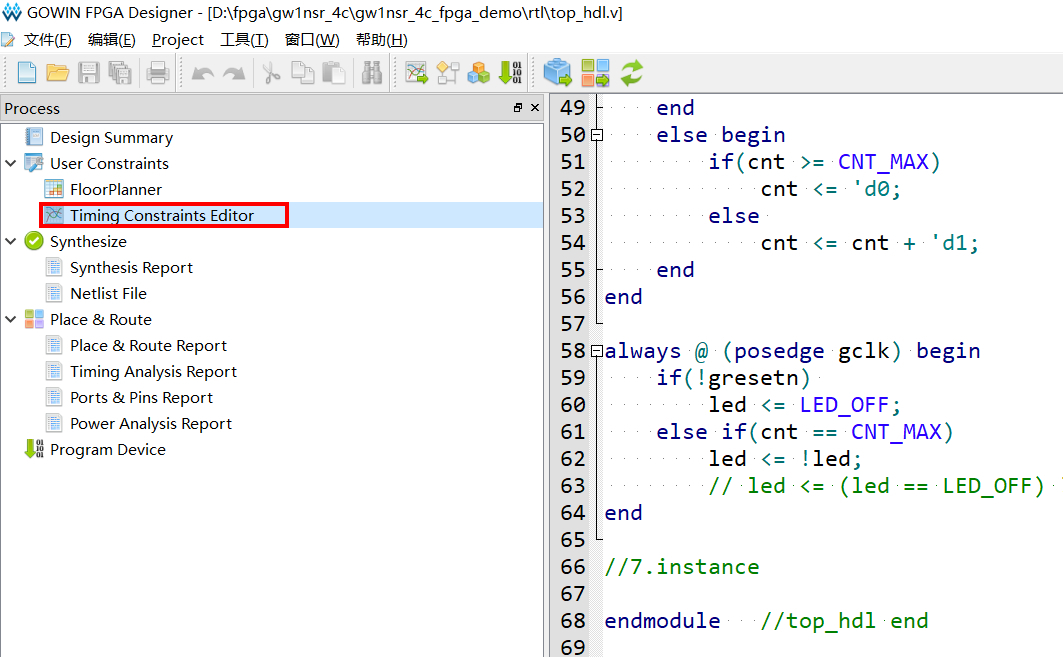

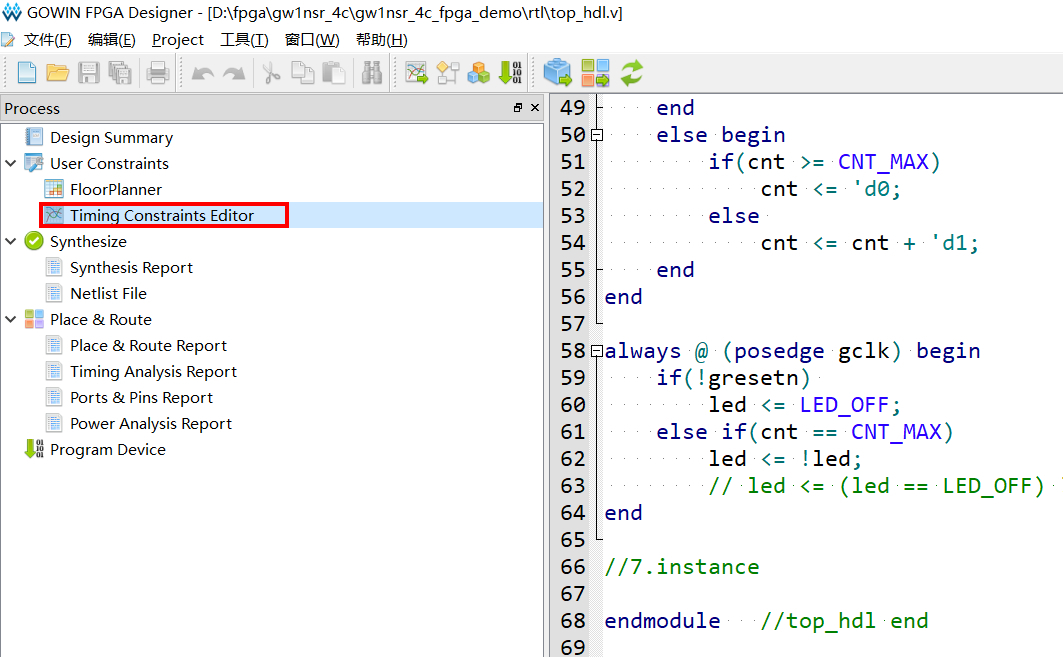

点击时序约束Timing Constraints Editor,打开时钟约束工具。

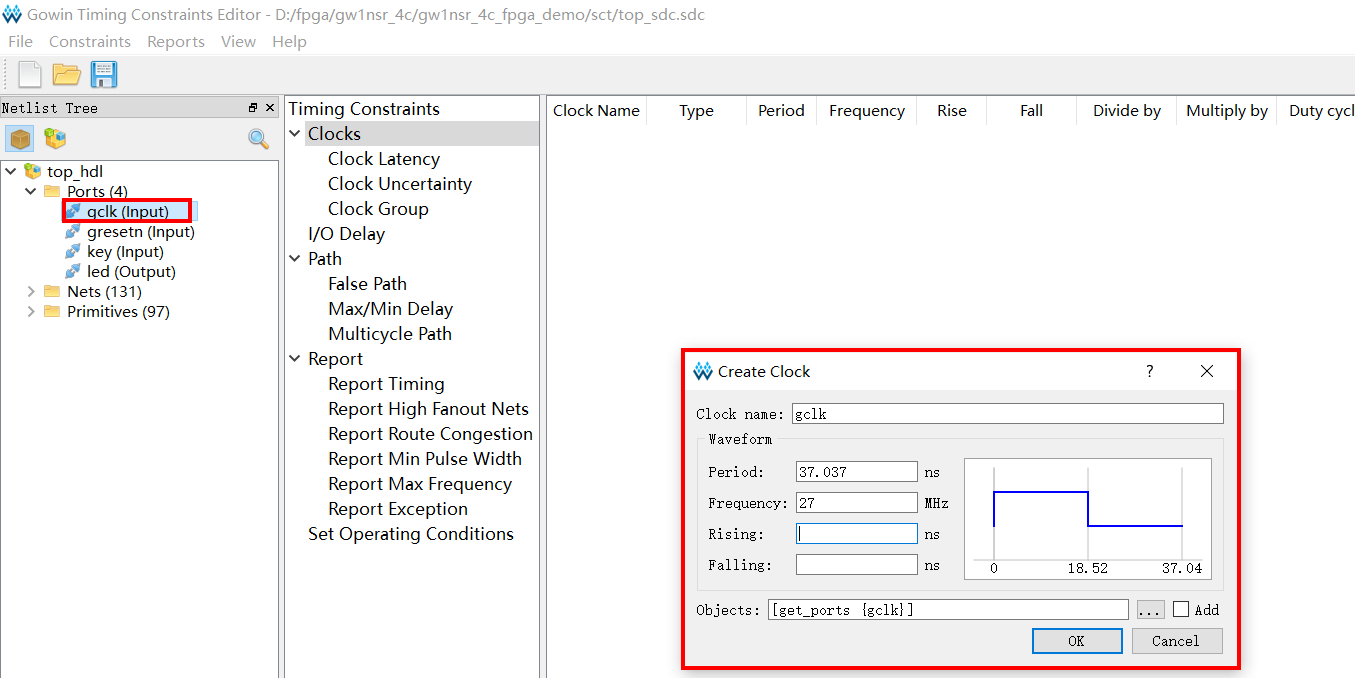

这里只对外部时钟进行约束,右键点击Ports->gclk,Add Clock,输入时钟频率为27MHz。

或者直接输入以下语句:

create_clock -name gclk -period

37.037 -waveform {

0 18.518} [get_ports {gclk}]

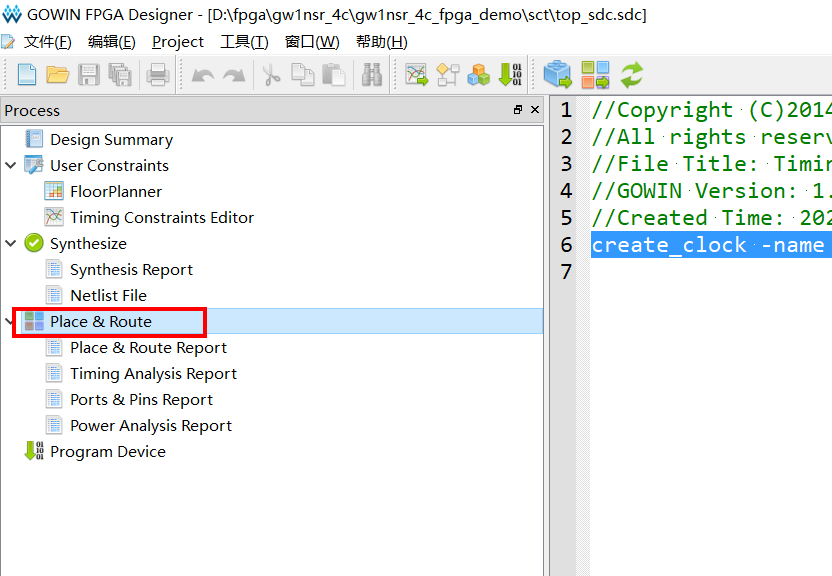

8. 比特流文件生成

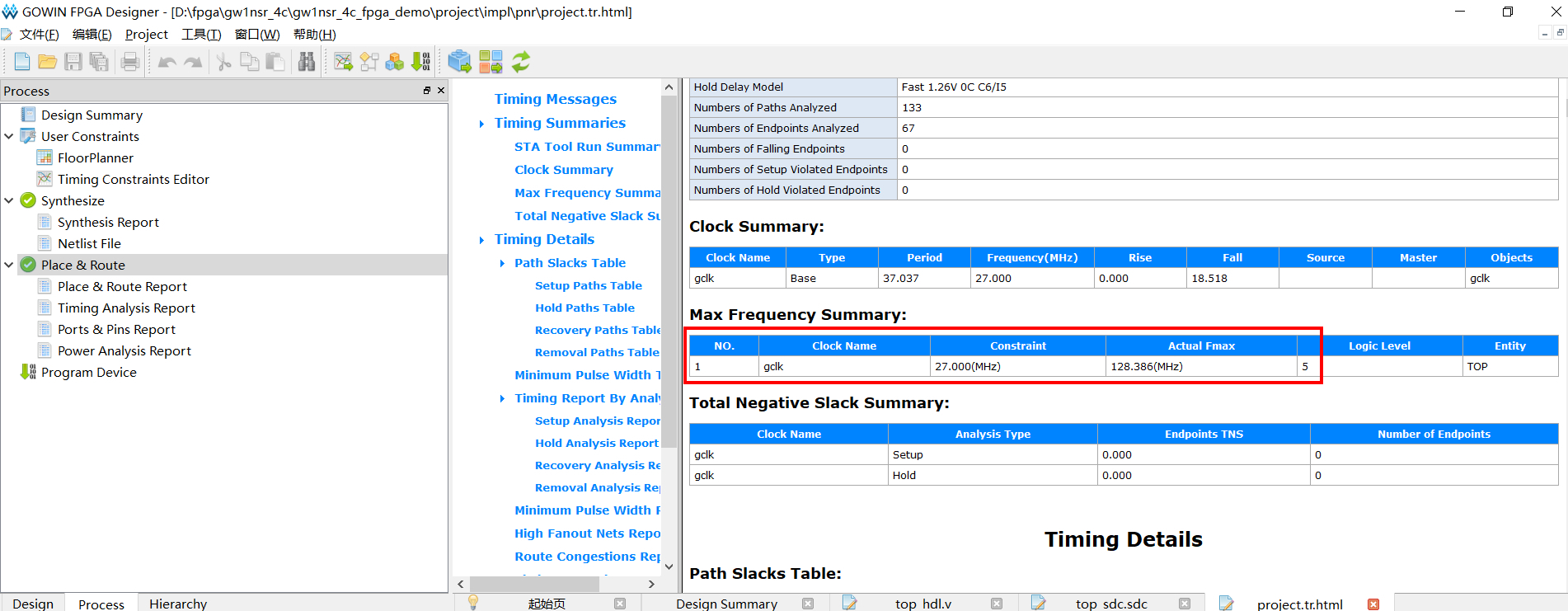

点击Place and Route,生成比特流文件,速度很快,几秒钟,比国外的EDA环境快很多!

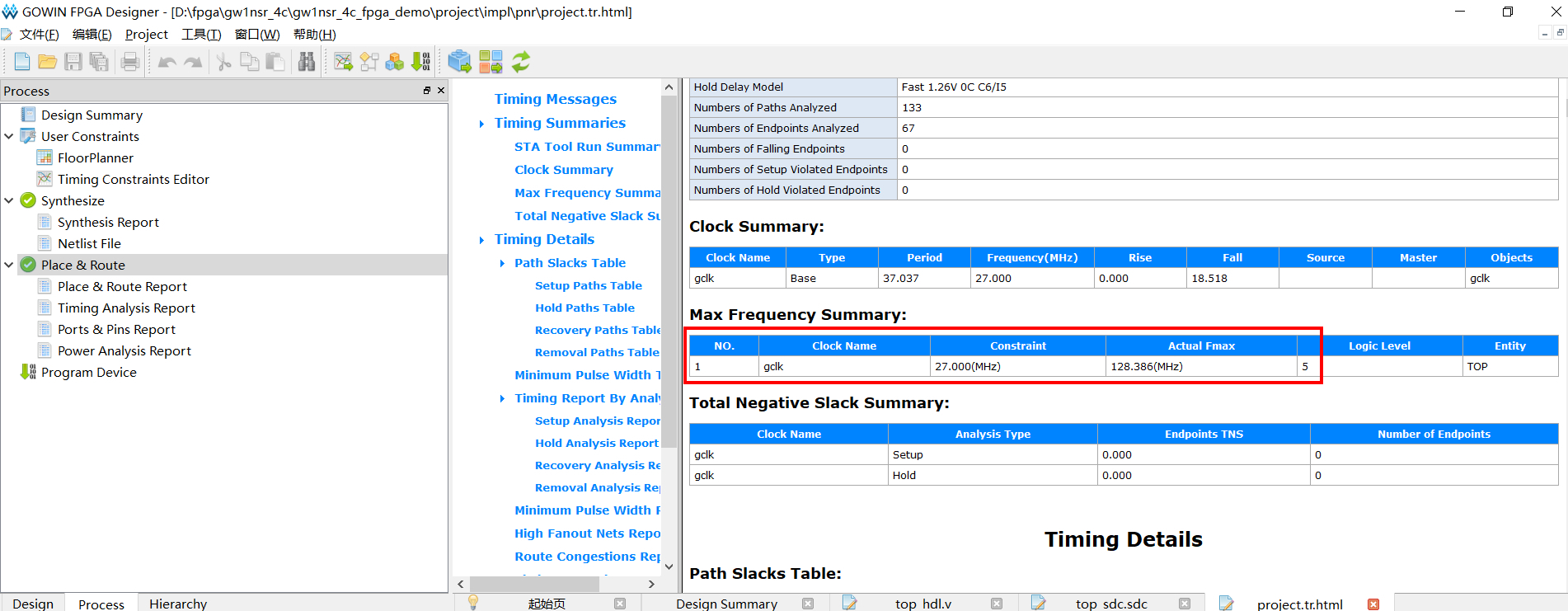

查看时序报告,可以看到满足设计要求,最大频率可以到128MHz。

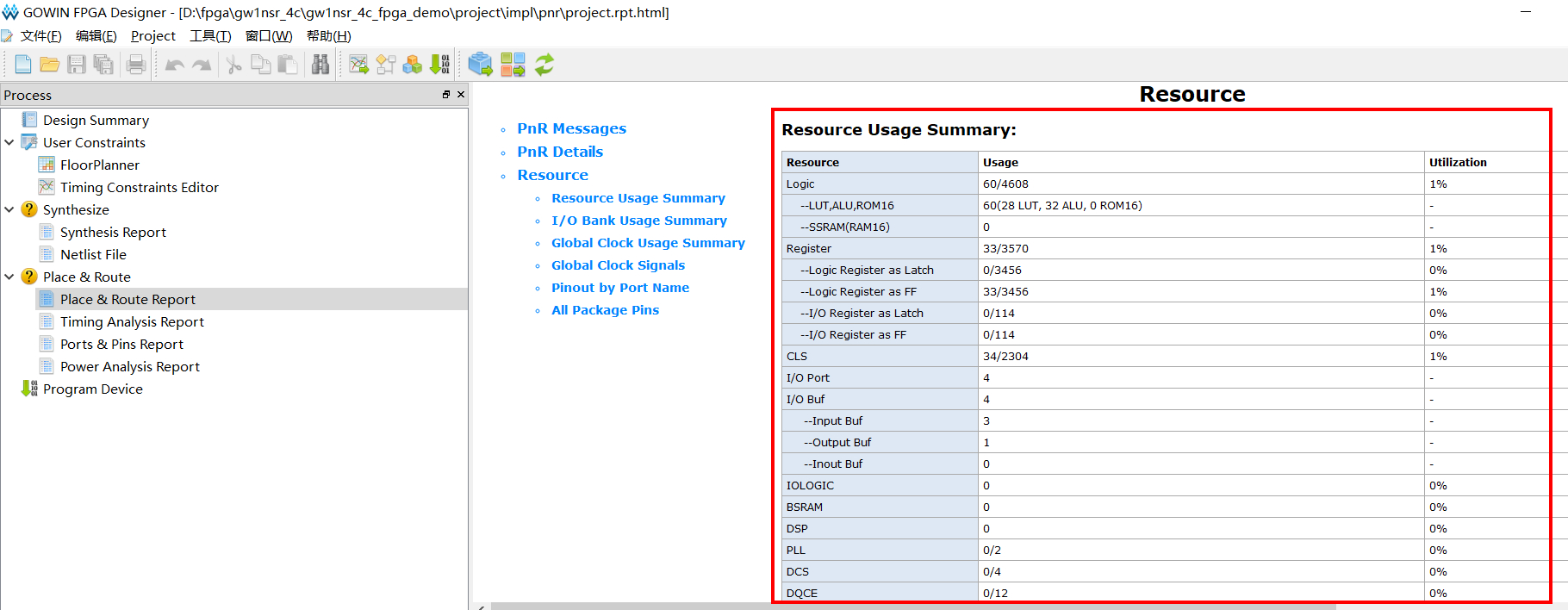

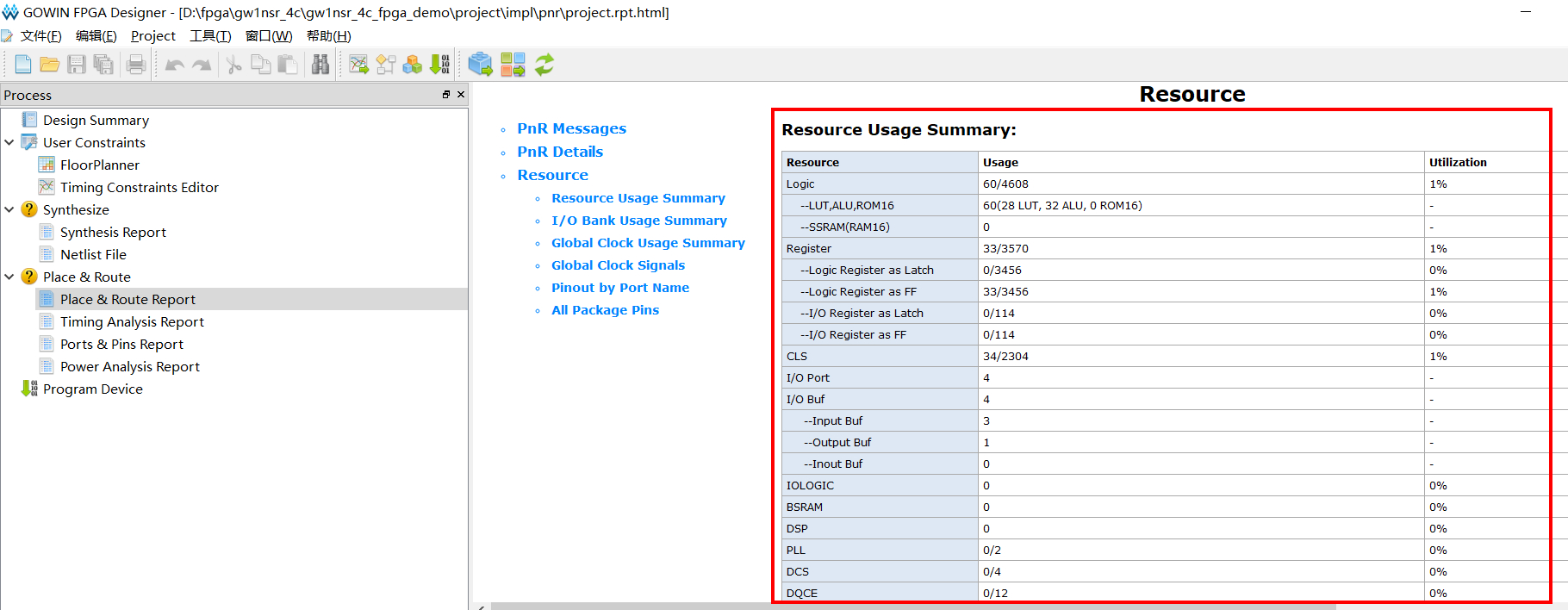

查看逻辑资源占用情况

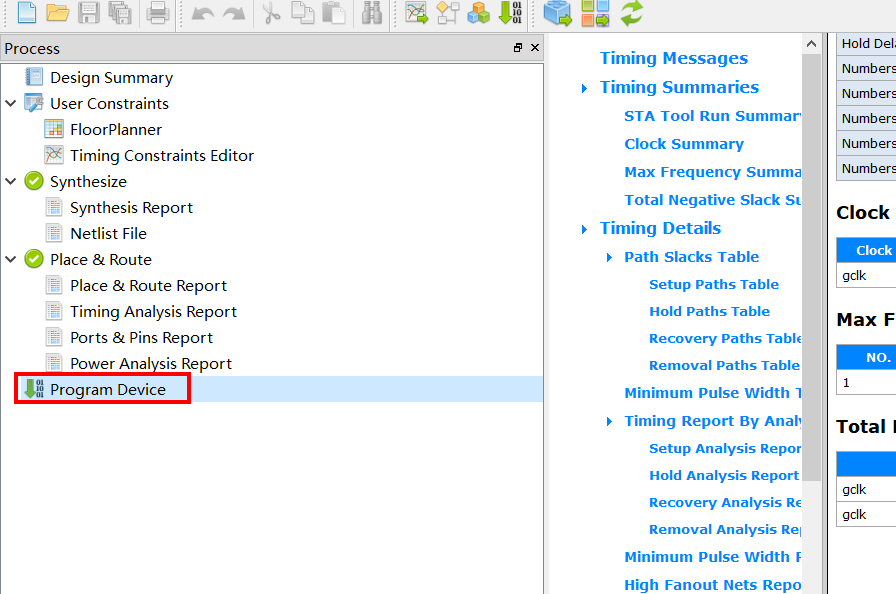

9. 程序下载

9. 程序下载

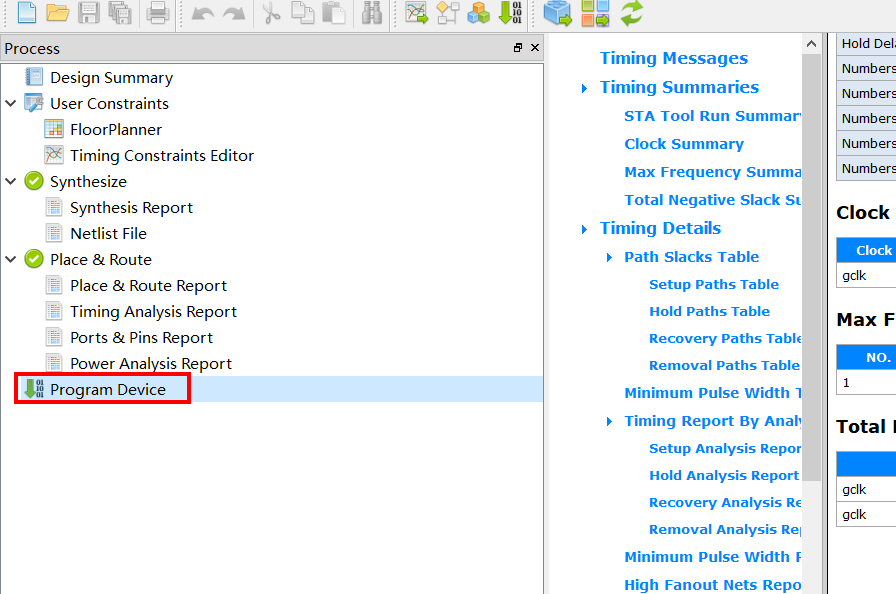

点击Program Device,打开编程工具,执行编程。

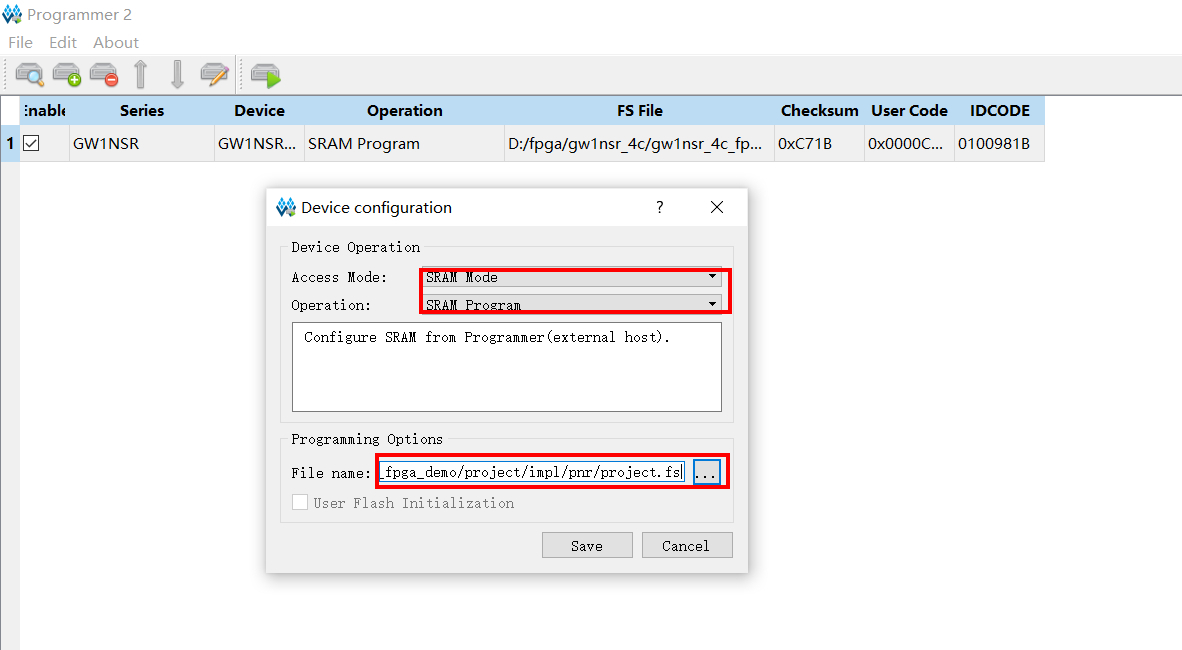

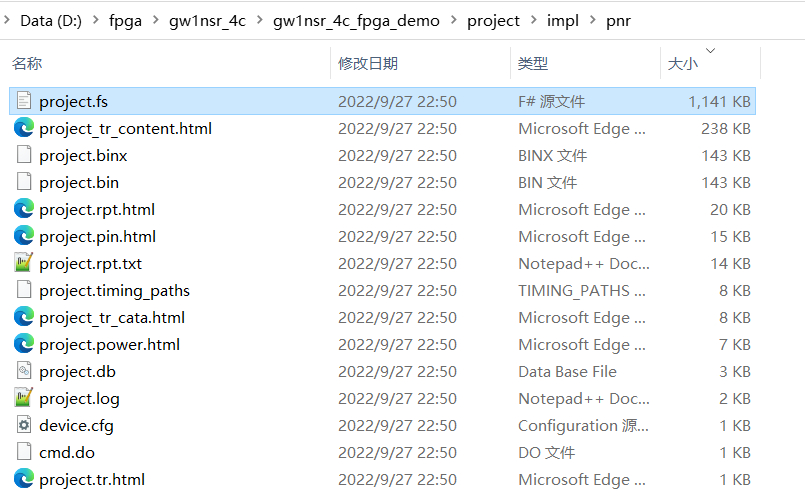

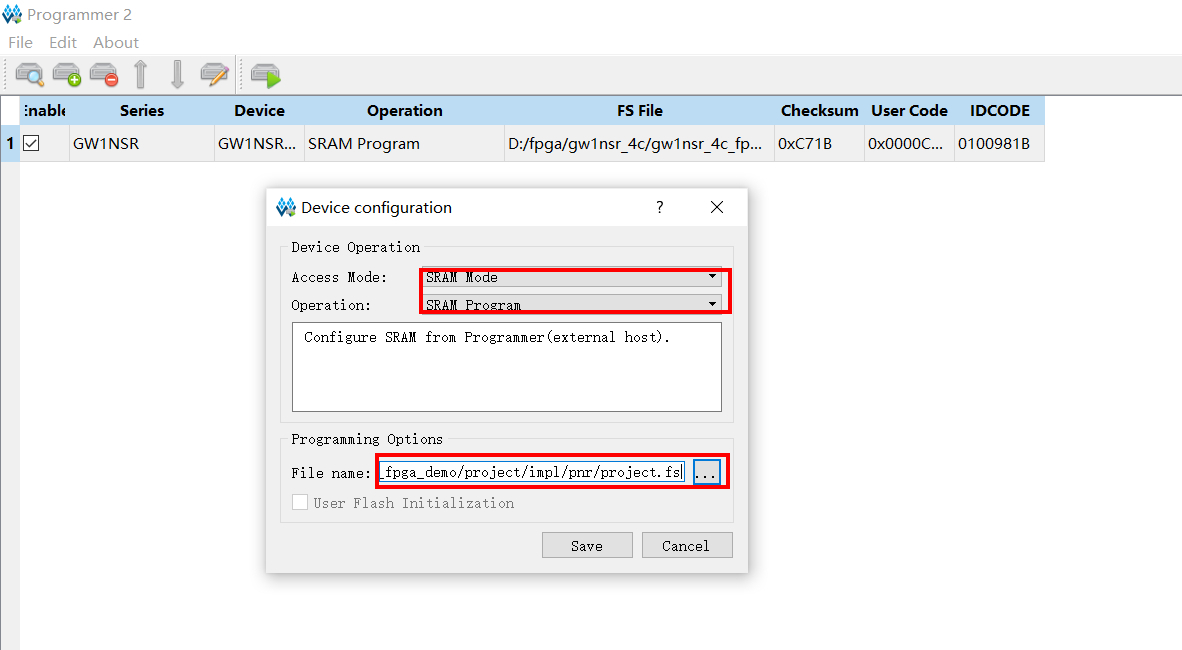

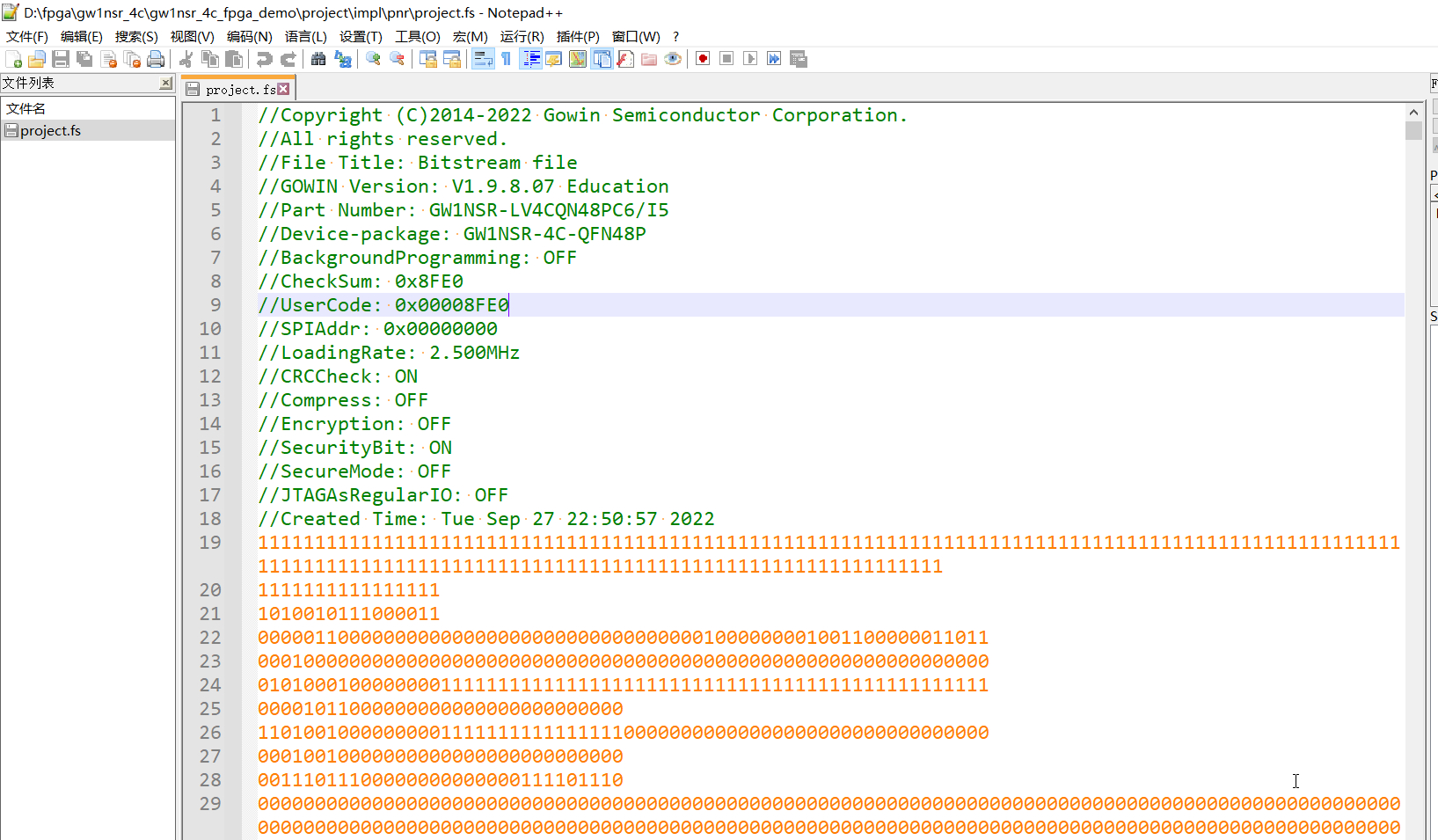

配置为SRAM模式,选择project/impl/pnr下的fs格式的比特流文件。这个模式是下载到内部RAM中,掉电程序会丢失。

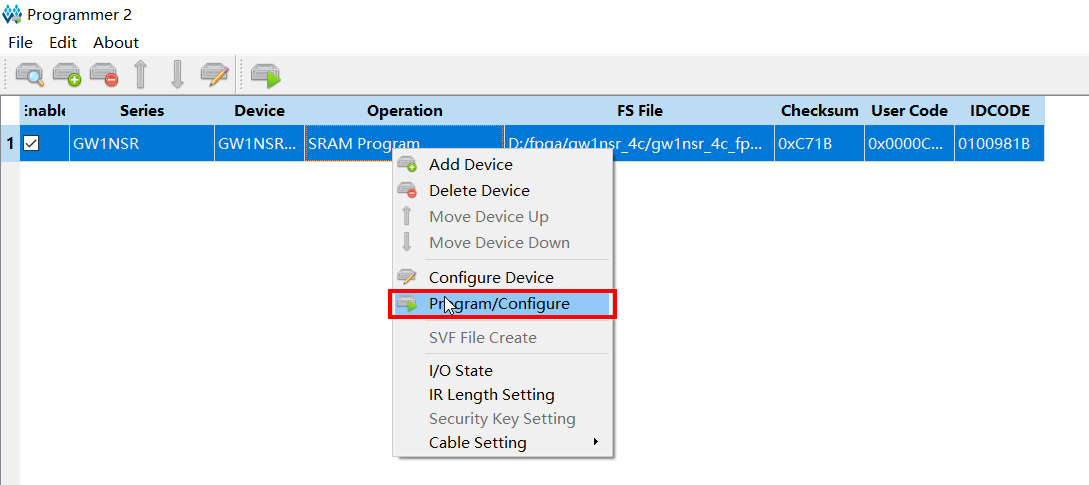

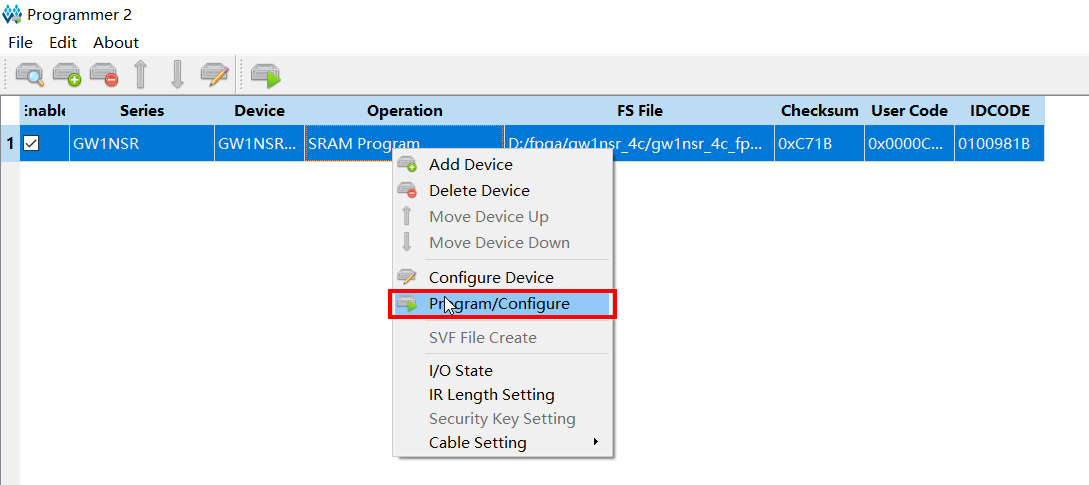

右键执行编程,下载速度很快。

10. 程序固化

10. 程序固化

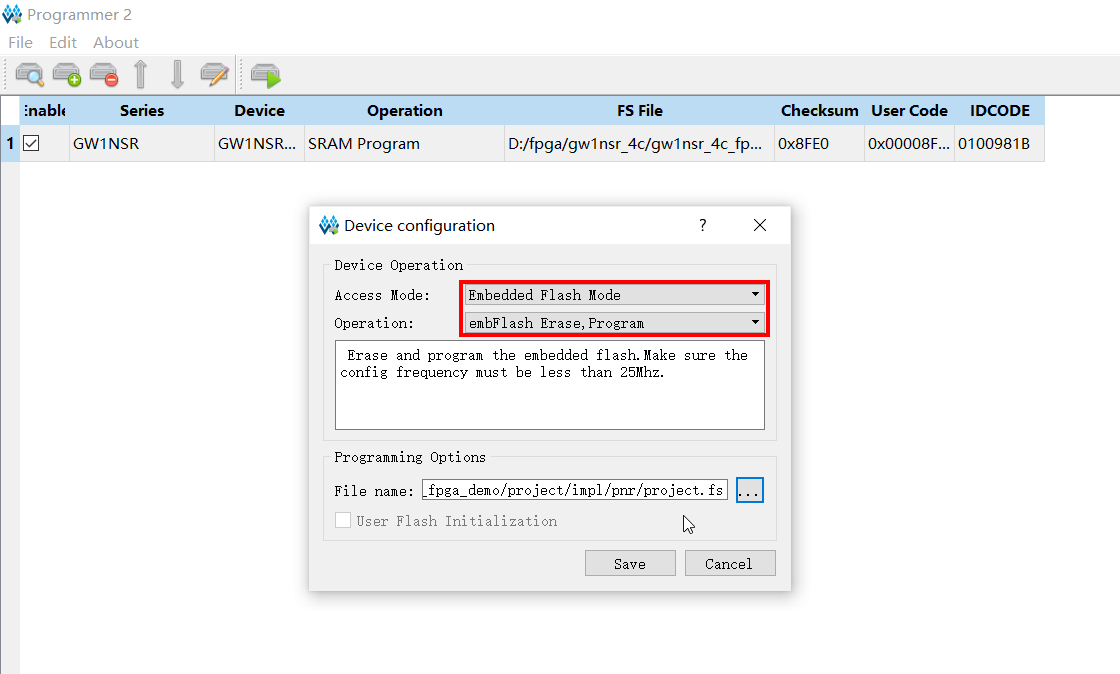

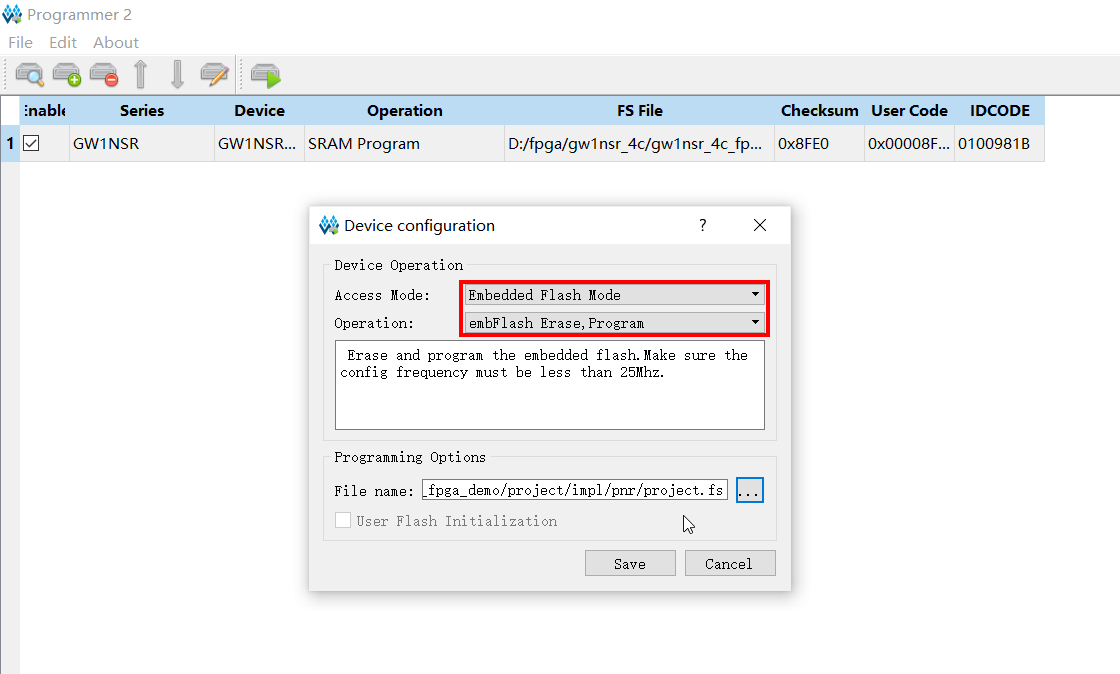

选择Embedded Flash Mode会把程序固化到内部Flash中,掉电程序不丢失,上电程序瞬时启动,同样是选择fs文件。

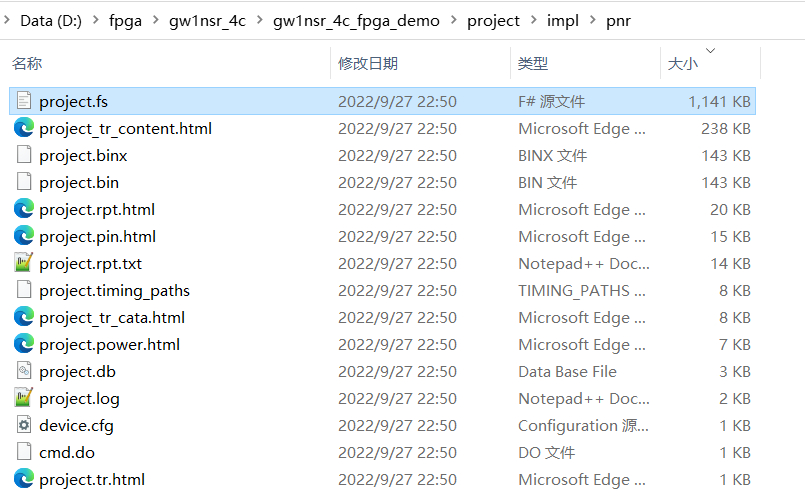

fs程序文件的保存路径

fs文件的内容格式

11. 总结

11. 总结

相比于国外FPGA厂商EDA开发环境,几个G到几十个G的大小,高云云源软件安装包也很小巧,界面也很简洁,综合速度非常快,是我没想到的,好像在使用单片机一样,点一下就编译完成了,以本文简单的LED示例工程为例,比特流文件几乎在几秒钟内生成;无论是下载比特流文件到RAM还是Flash中,速度都很快,而且只有一种fs程序文件格式,不用再进行bit/mcs转换;云源软件自带的编辑器也很好用,和Notepad++界面差不多,而且快捷键很方便,具有基本的自动补全功能。

12. 工程下载

以下链接是本次笔记中建立的高云FPGA工程,开发环境是Gowin V1.9.8.07 Education

- https://wcc-blog.oss-accelerate.aliyuncs.com/img/220928/gw1nsr_4c_fpga_demo.rar

3. 设计输入

3. 设计输入

4. 设计仿真

4. 设计仿真

6. 管脚分配

6. 管脚分配

9. 程序下载

9. 程序下载

10. 程序固化

10. 程序固化

11. 总结

11. 总结

/2

/2

托尼杰克马 2022-10-29 14:45

哈哈大哥哥 2022-10-28 14:45

乖乖兔爸爸 2022-10-10 09:30

“生成比特流文件速度快,下载也快,比国外EDA环境快很多”,原因是片上资源才4608,点灯总资源才60,简直是玩具一样。

你非要说自己的发条小车,0.5秒就起步发动了,比法拉利赛车要快,我也没办法,的确是事实。但能说明什么?

你的发条小车比法拉利赛车牛么?能hold住上万公里的赛程么?