本文是高云FPGA学习笔记系列的第4篇文章,首发于:

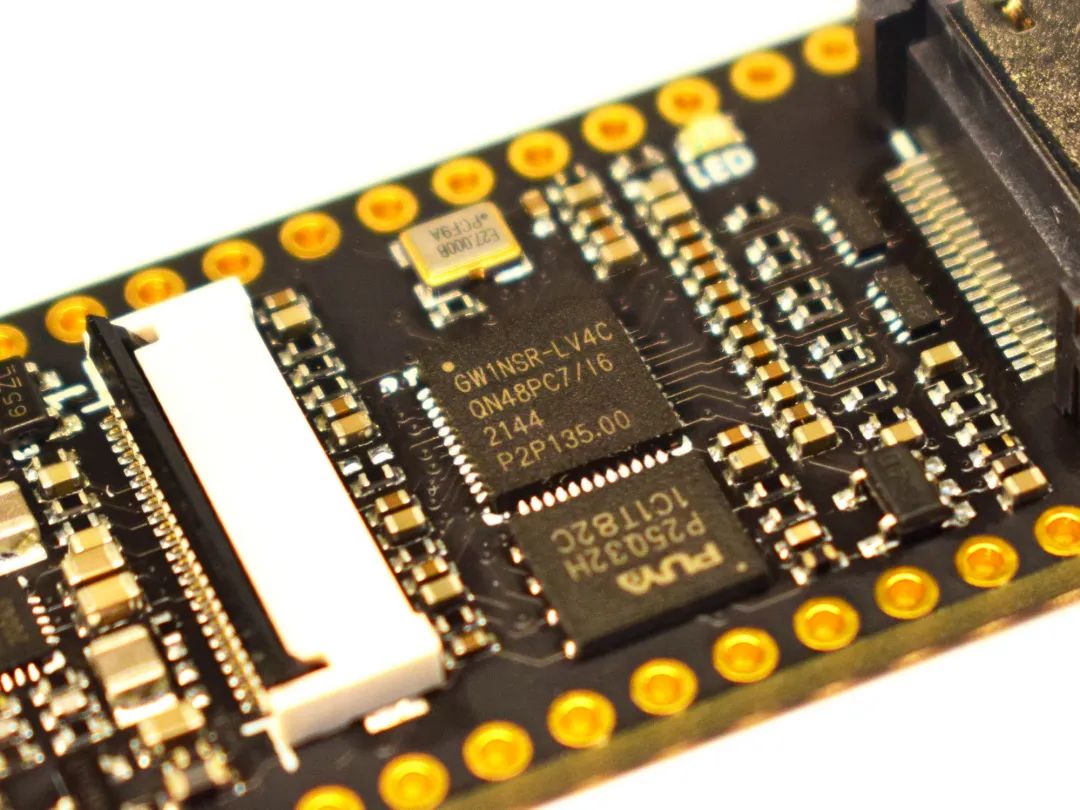

本篇文章介绍高云GW1NSR-4C FPGA基本原语和IP配置、使用和修改,以及如何在ModelSim环境下仿真这些IP和原语,基于TangNano 4K开发板。

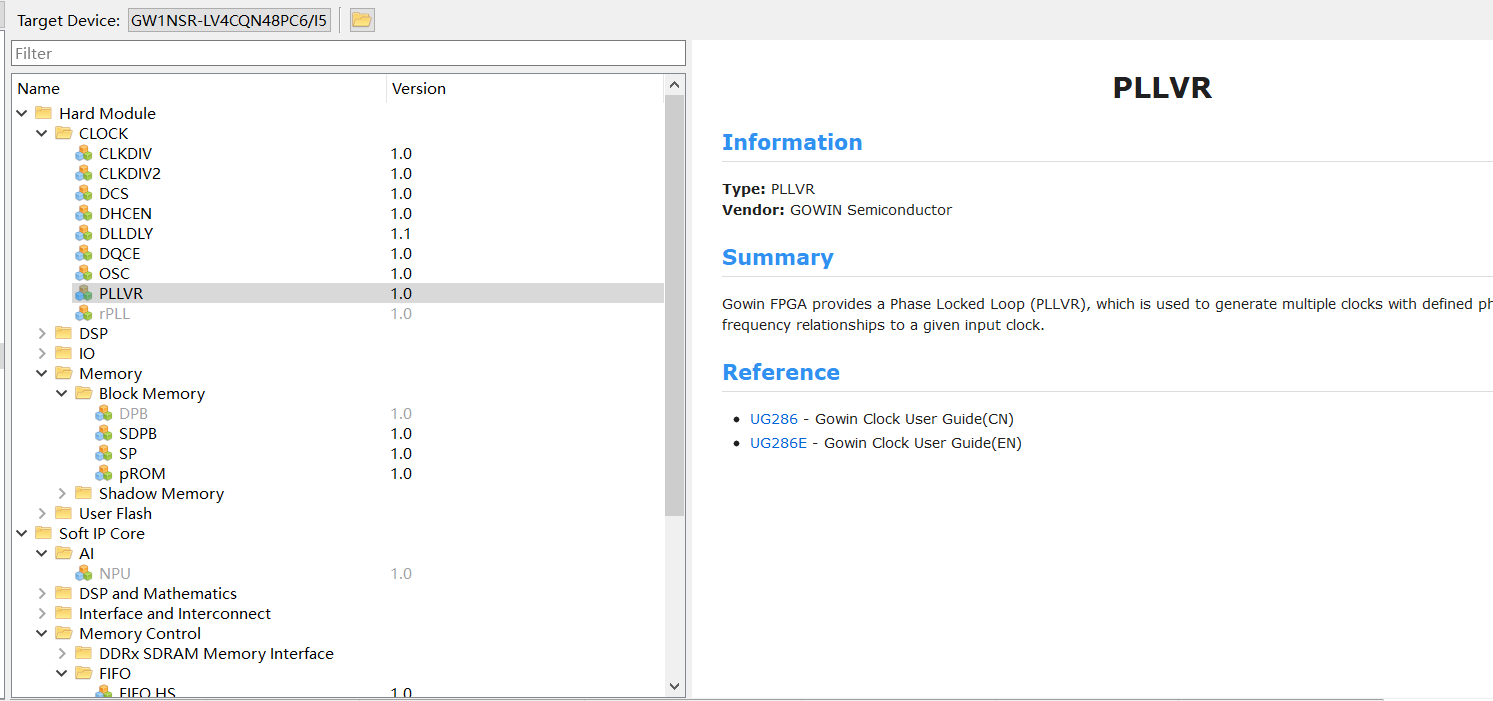

打开高云云源软件,点击工具->IP Core Generator可以调出高云IP核生成工具。

可以看到当前使用的器件支持的各类型IP核,如果不支持,IP核为灰色不可选,右侧有当前IP使用的中英文说明文档,点击可以直接下载。

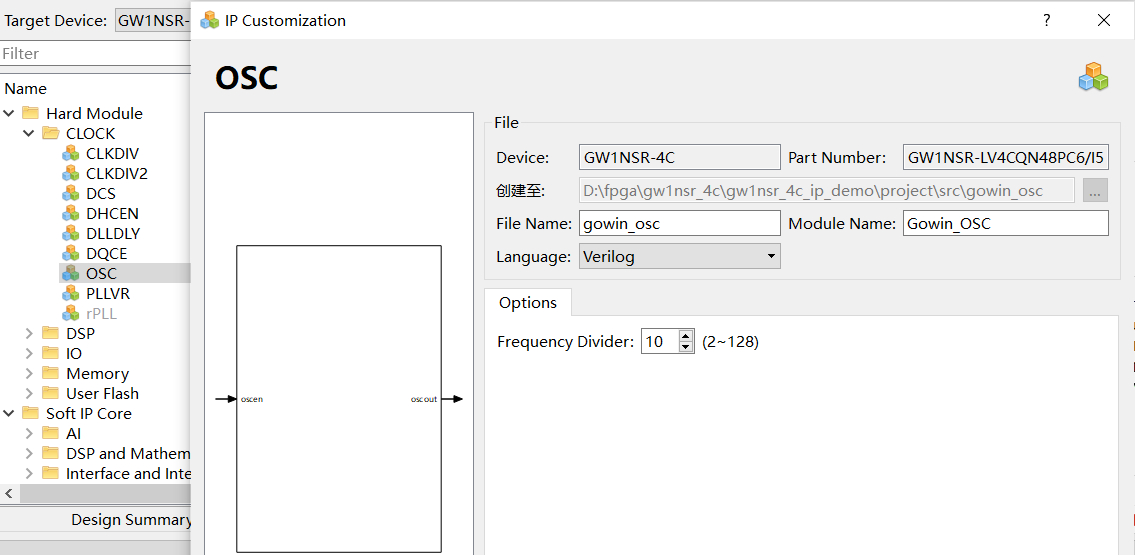

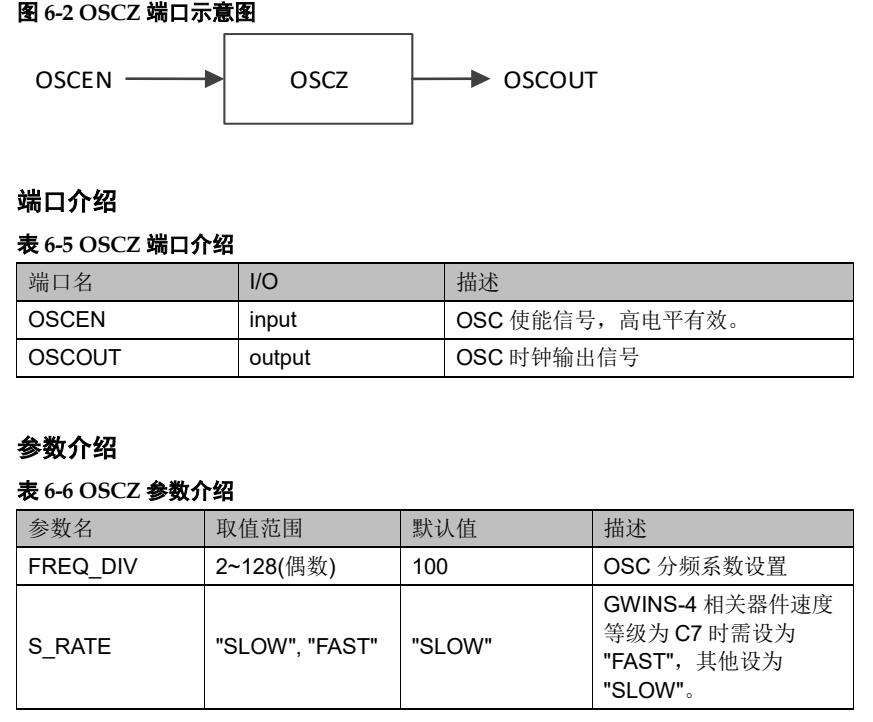

GW1NSR-4C芯片内部集成了一颗250MHz的时钟晶体,可以配置2-128偶数分配系数,带使能端。本次示例我们配置成输出25MHz输出,即10分频。

模块名称,保存路径可自定义,这里保持默认设置。

最终生成的文件:

module Gowin_OSC (oscout, oscen);我们也可以在自己的设计中直接例化OSCZ原语来使用。

关于高云FPGA时钟资源的介绍,可以查看云源软件安装目录下的UG286文档:

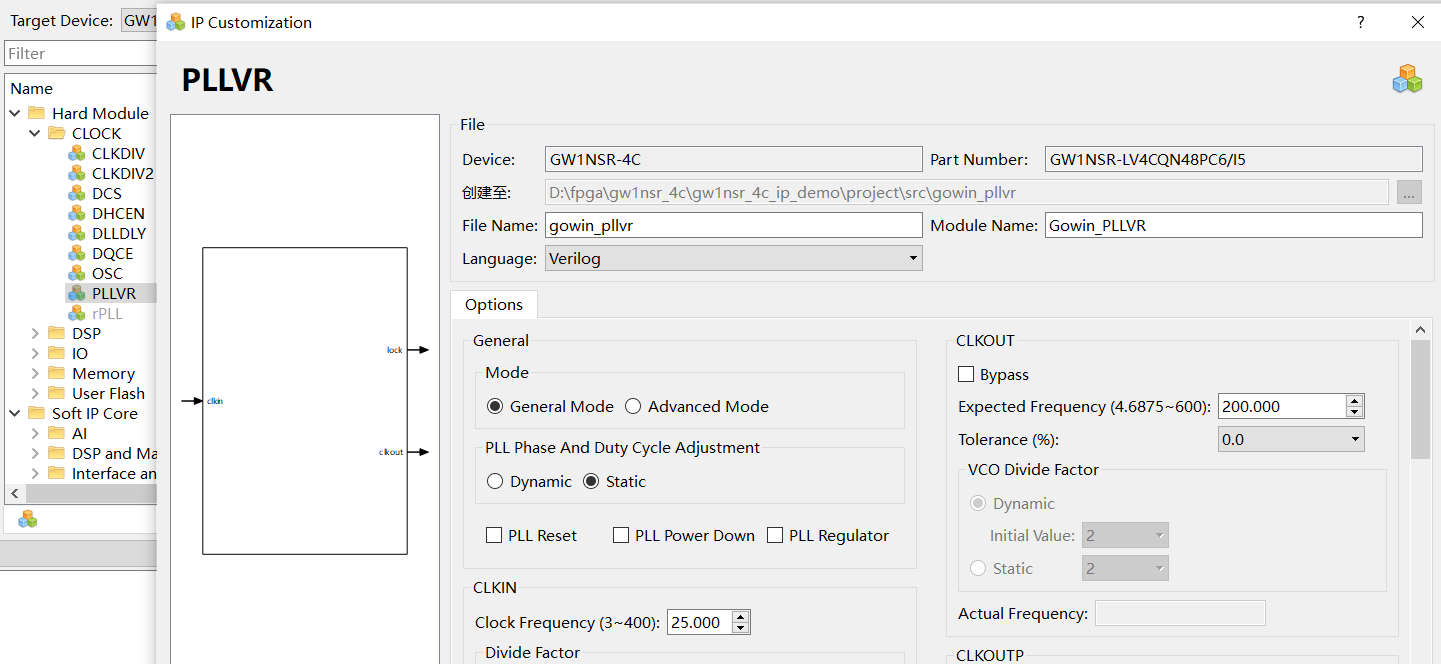

\Gowin\Gowin_V1.9.8.07_Education\IDE\doc\CN\UG286-1.9.4_Gowin时钟资源(Clock)用户指南.pdf3. IP示例2:锁相环PLLVR和OSCZ一样,选择PLLVR进行配置,指定PLL输入频率为25MHz,输出频率为200MHz。

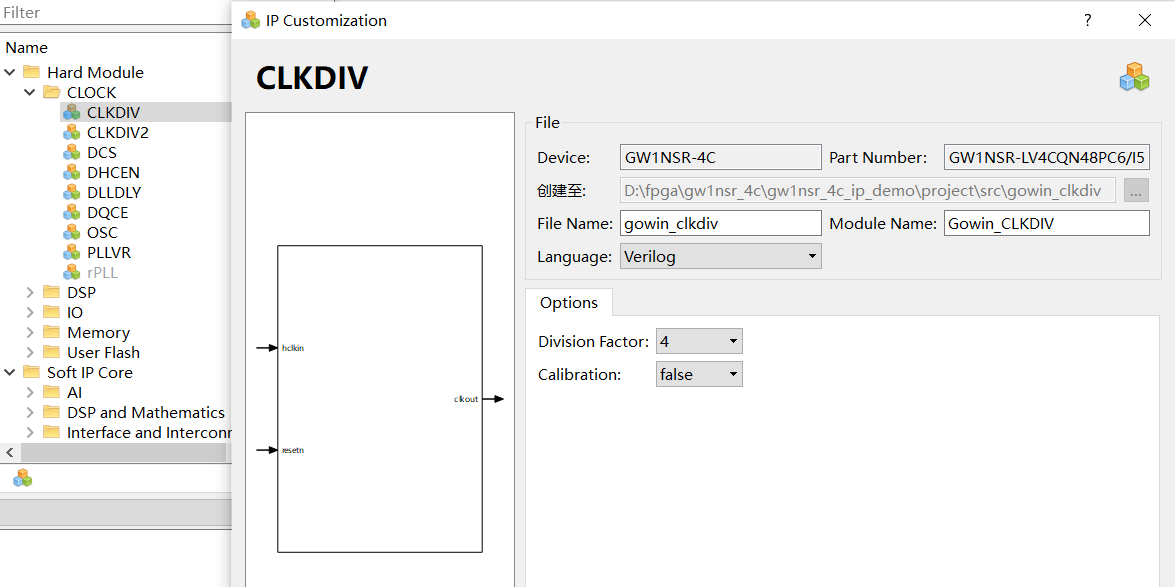

选择CLKDIV配置分频器系数为4

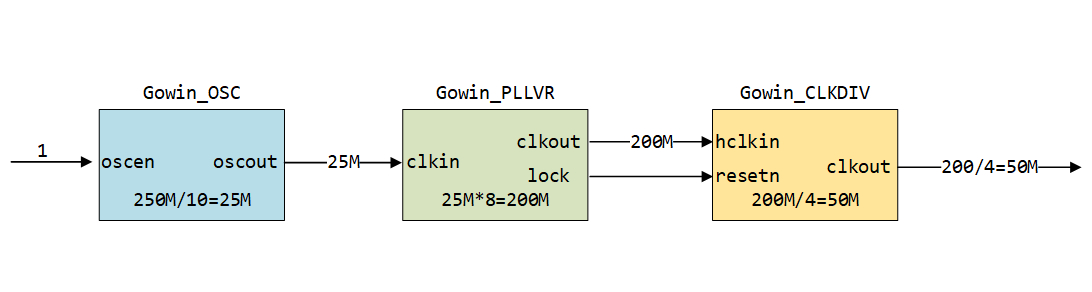

为了同时调用这几个IP,我们按照如下图进行连接。

顶层文件:

/***************************************************************和上一篇笔记实现的效果是一样的,按键按下LED快闪,按键释放LED慢闪,只不过本工程没使用到外部的晶体。

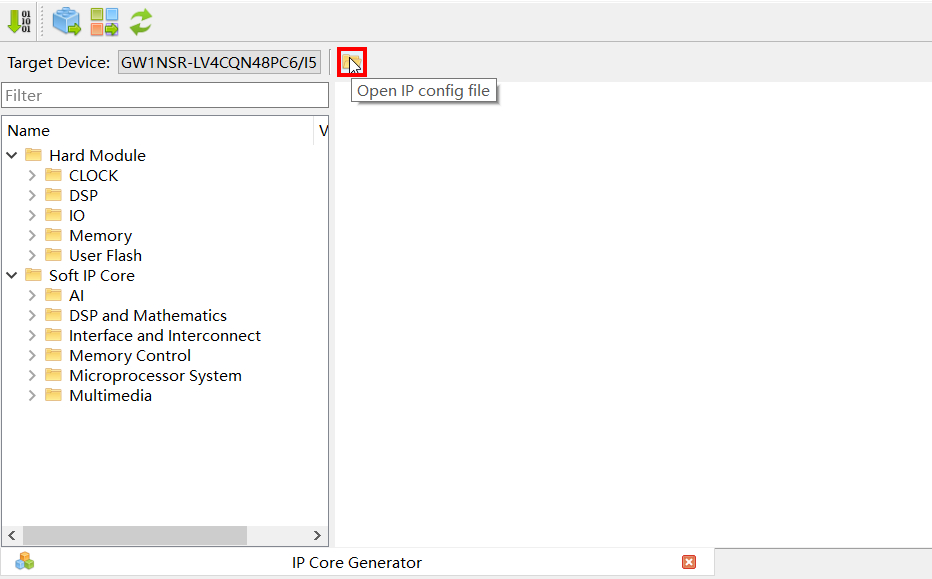

5. IP核配置修改云源软件支持对已经配置的IP核进行修改,说实话我一开始并没有找到这个功能,还以为无法修改呢,后来看了官方的视频教程才发现支持修改已经配置的IP。

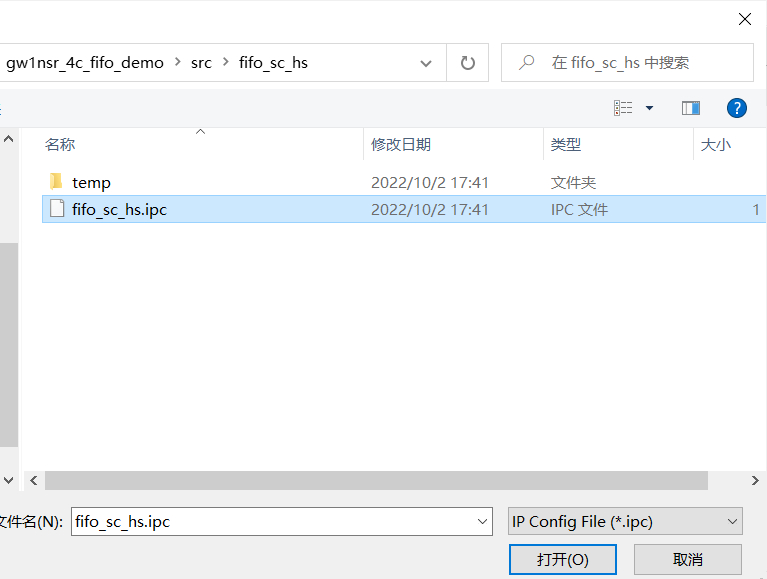

首先打开IP核生成界面,点击打开图标。

找到要修改的IP核文件夹下的ipc文件打开。

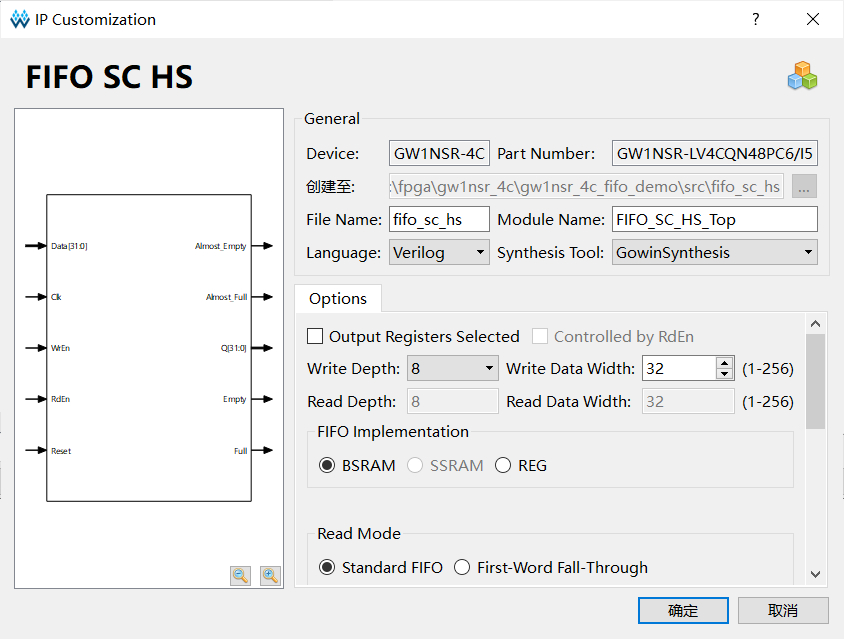

这样就可以进行修改了

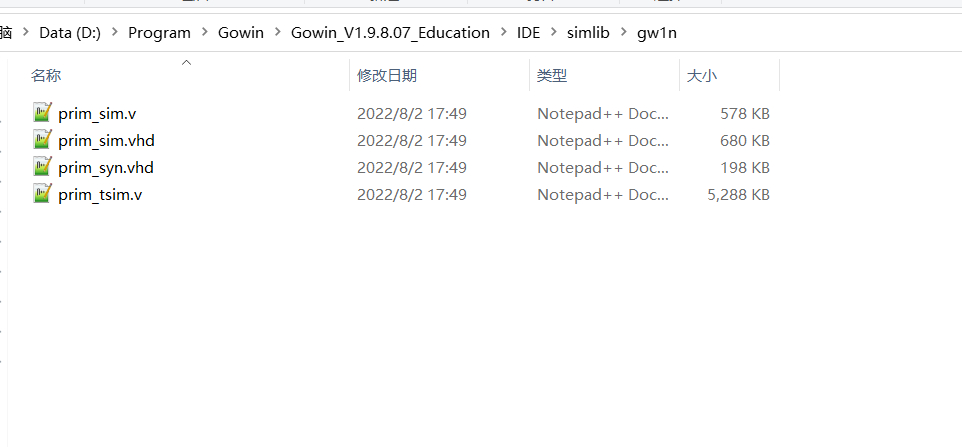

高云云源软件不包含仿真工具,需要借助第三方工具来完成功能仿真,如果涉及到官方的IP调用,比如PLL,OSC,FIFO等IP的仿真,需要进行添加一个官方的IP仿真库文件,文件路径为:

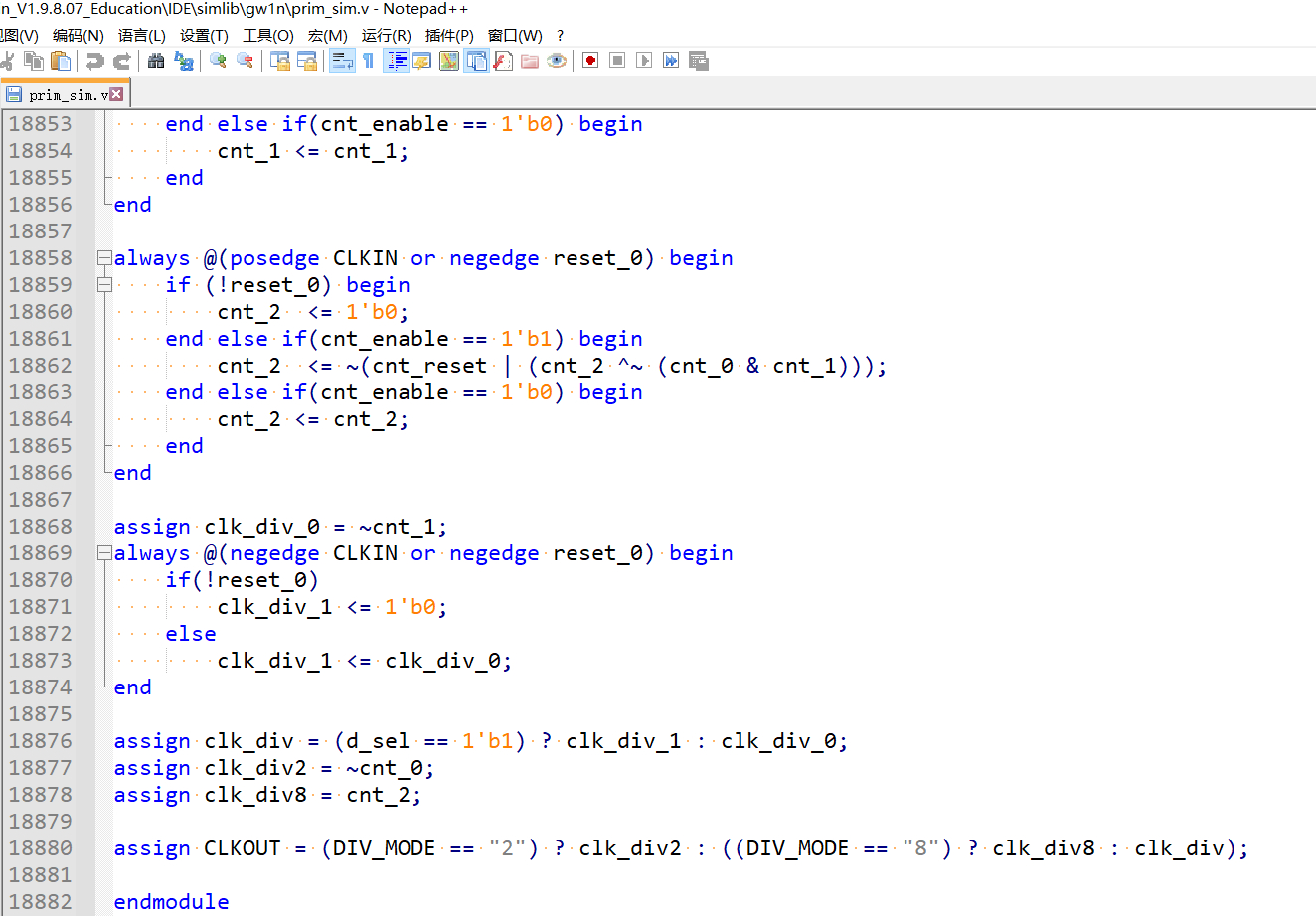

D:\Program\Gowin\Gowin_V1.9.8.07_Education\IDE\simlib\gw1n\prim_sim.v这个文件大小约600KB,近两万行代码,包括高云所有IP核的仿真模型,可以在Modelsim或其他第三方仿真工具中添加调用。

高云IP核仿真库文件内容完全开放,没有进行加密处理。

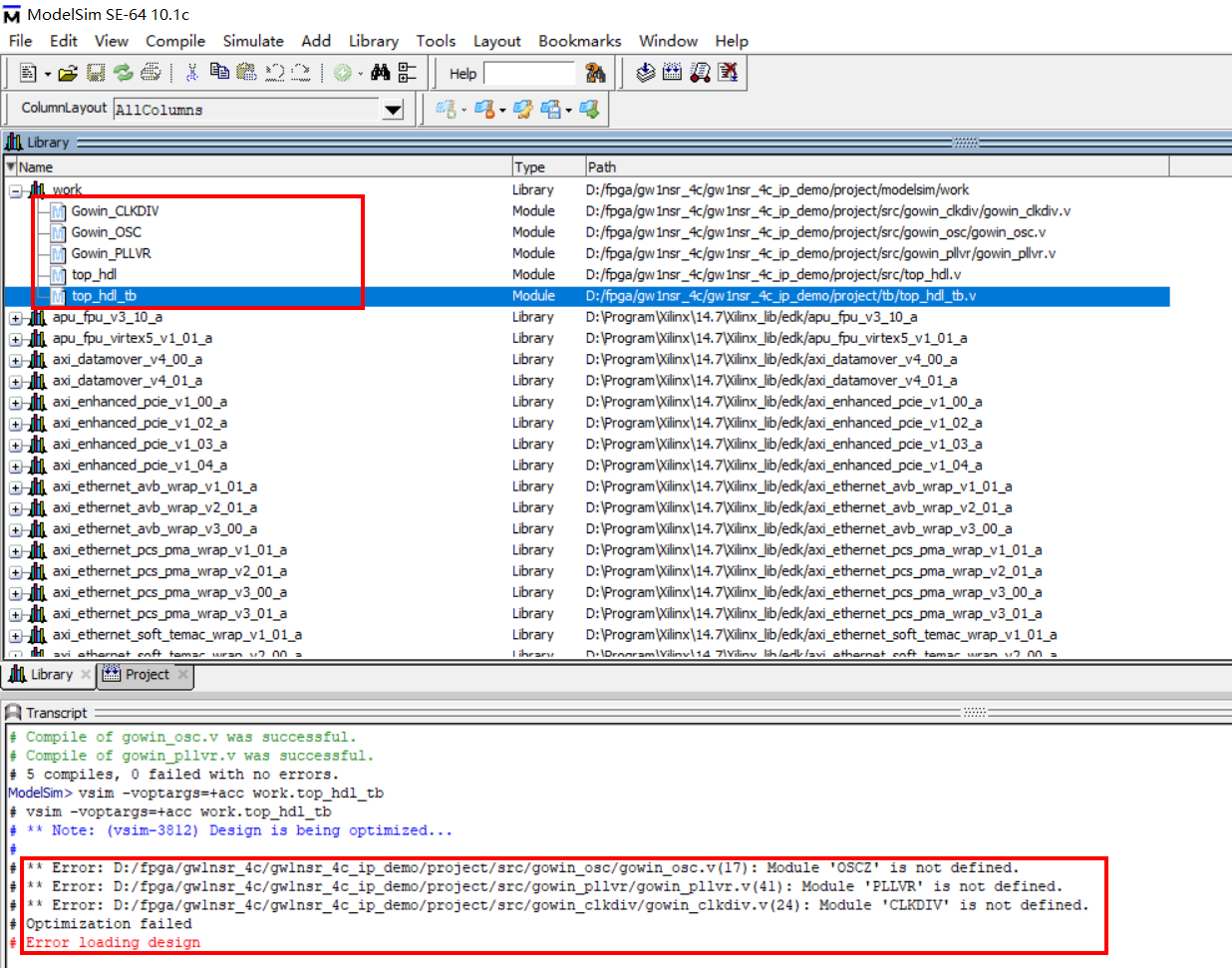

编译通过,仿真时会提示调用的模块未定义

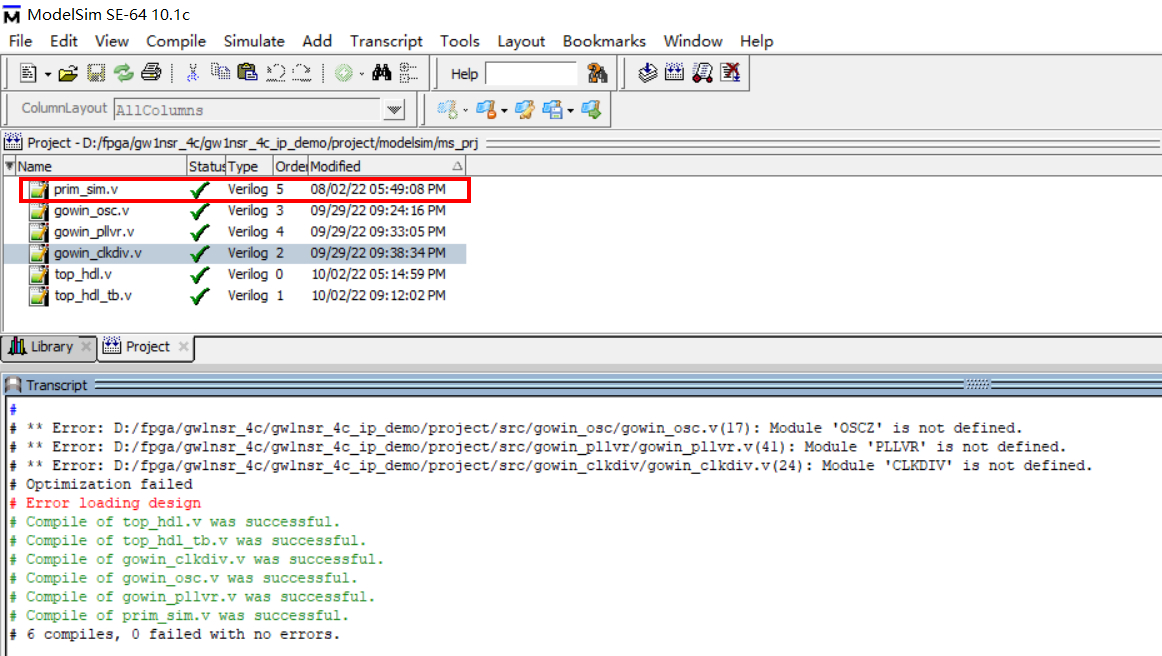

把prim_sim.v添加到Modelsim工程,再次编译,执行仿真。

提示如下:

在Testbench中例化如下全局复位模块,因为仿真库中调用了此模块:

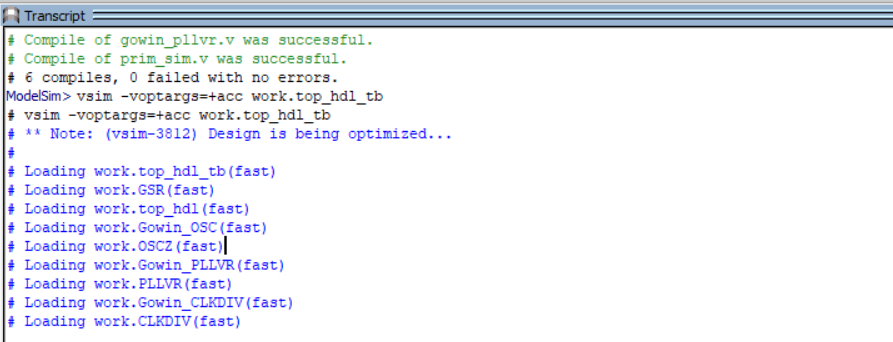

GSR GSR(重新编译,成功执行仿真。

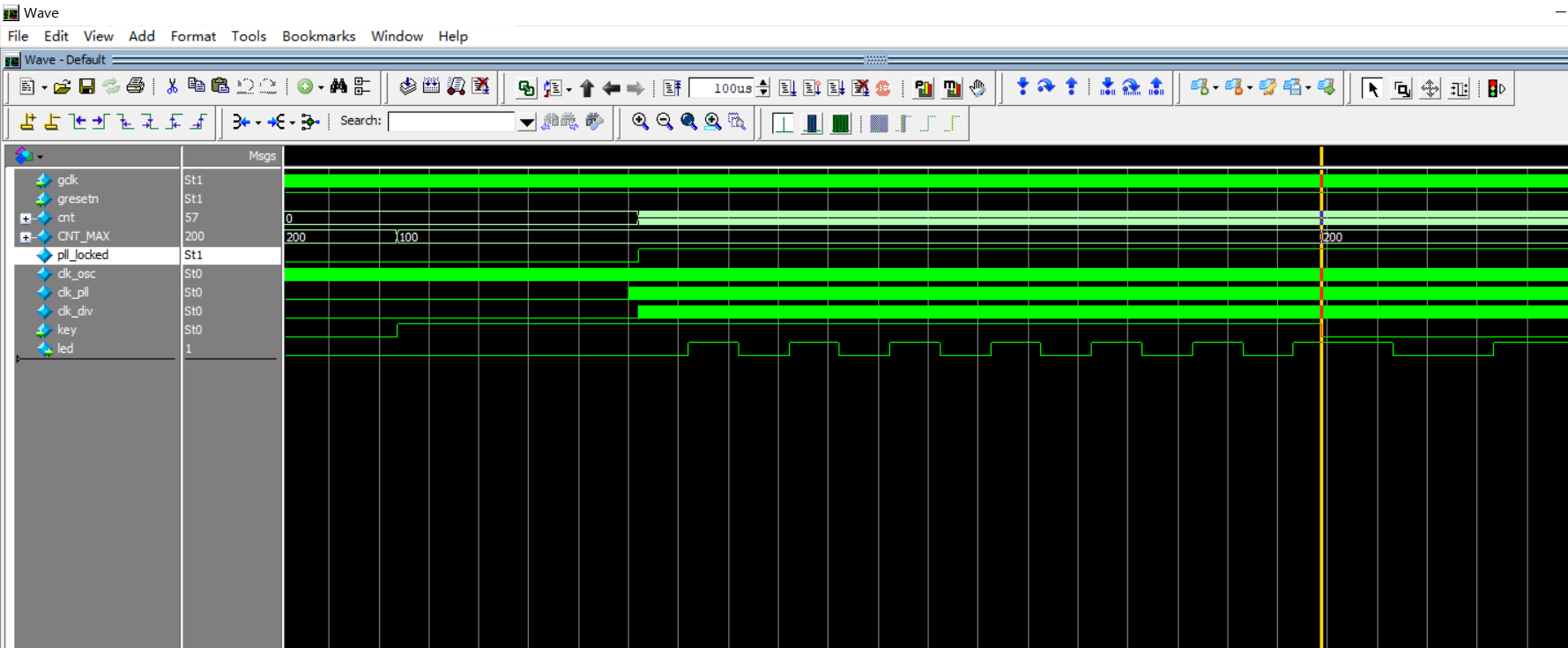

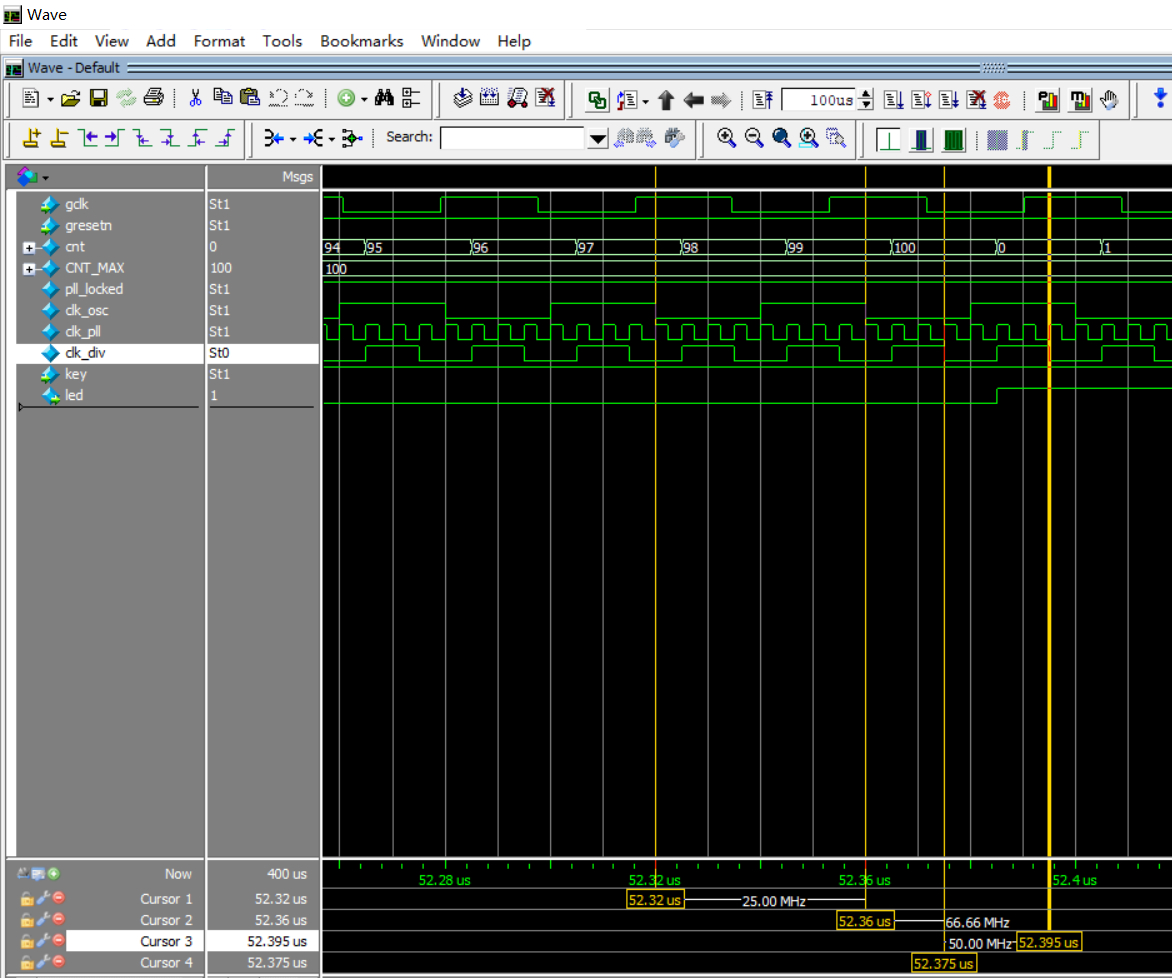

仿真波形:

OSC、PLL、DIV输出时钟频率和配置是一致的。

总的来说,GW1NSR-4C这颗FPGA可以使用的IP核不算太多,但基本的PLL,FIFO,RAM,DSP都有,还有一些非常实用的协议IP,如I2C,SPI,UART主机从机,以及之间的相互转换都有相应的IP,还有一些多媒体相关的IP,可以满足大多数的需求。

联合ModelSim仿真也比较简单,只需要添加一个仿真库文件即可完成所有IP的仿真,还是非常方便的。

本次示例中的工程,可以访问下方链接下载:

作者: whik, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3887760.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/1

/1

乖乖兔爸爸 2022-10-10 09:55

我对加解密,视频编解码 相关的 IP-Core 很感兴趣,可惜没有找到

不过 4068的资源,估计AI什么的,比较难放进了