作者:Andy Nightingale

即使在今天,超值多核系统级芯片 (SoC) 设计也可以由数百个知识产权 (IP) 模块组成,通常包含多达 1000 万个逻辑门。SoC 开发人员创建这种复杂性器件的一种方法是使用可靠的第三方供应商提供的经过验证的 IP 块。例如,当USB 3.2 Gen x接口已经作为现成的IP提供时,花费数千小时来重新发明它是没有意义的。相反,工程师可以将精力专注于创建自己内部的 IP ,这将使他们的SoC 具有差异化,与其他竞争产品区分开来。

对于当今大多数高性能、高容量和高复杂性的SoC来说,在连接IP模块以便它们可以相互通信时,唯一可行的选择是使用片上网络 (NoC)。许多人没有意识到的是,NoC也是IP,尽管这类IP跨越了整个SoC。像其他IP一样,设计团队可以决定自己内部开发NoC,也可以选择使用可靠的第三方供应商提供的经过验证的NoC IP,例如Arteris的事实行业标准FlexNoC。

SoC 架构师容易忽视的另一个考虑因素是 NoC 的设计环境必须具有物理感知能力。这大大促进了在流程的前端实现最佳NoC拓扑所需空间的探索。它还显著加快了后端的时序收敛速度。

组成 NoC 的元素

NoC 由多个元素组成。首先,每个IP模块都有自己的接口特性(数据宽度、时钟频率等),并且使用SoC行业采用的众多标准协议(OCP、APB、AHB、AXI、STBus、DTL等)之一。需要将一个或多个套接字连接到每个功能 IP 块,然后,这些套接字会将来自源 IP 的数据分组和序列化为适合通过网络传输的规范化形式。与之相反,连接到目的 IP 的套接字将把传入的数据包转换回所需的形式。

除了将所有部分连接在一起的电线外,NoC 的主要传输机制主要由交换机和缓冲器组成。交换机的作用类似于带有相关仲裁器的多路复用器,或带有相关映射逻辑的多路分解器,使用每个数据包标头中的目标数据从其源路由到其预期目的地。同时,缓冲器被用作存储元素,沿路径聚合数据。例如,缓冲区可以从一个使用快时钟的 IP 块快速加载,然后它可以将注意力转移到其他任务上,同时另一个使用较慢时钟的 IP 块将其耗尽。

最后但同样重要的一点是,将流水线寄存器插入到NoC路径中以解决时序问题。这些问题可能是由于NoC需要跨越SoC长距离贯穿造成的。

更小的几何形状意味着更大的问题

随着SoC设计转向更先进的工艺,芯片上的晶体管变得更小、更快。不幸的是,电线的尺寸和速度不能以相同的速率缩放,这意味着它们在面积和功率方面的相对成本更高。除了可以使用更小的器件尺寸将更多的逻辑压缩到同一区域之外,芯片本身也越来越大,从而支持越来越多的IP模块。SoC架构在时钟频率、数据带宽和关键路径的延迟优化方面也有更高的性能要求。

大型 7nm SoC 可能需要 6,000+ 个流水线寄存器。开发人员在确定这些寄存器需要位于何处以满足时序需求时,必须考虑许多参数,同时尽量减少面积、延迟和拥塞。由于这是一项艰巨的任务,通常伴随着紧迫的时间表,手动执行流水线寄存器的插入总是会导致过度设计,以减少昂贵的布局布线(P&R)迭代。随后带来的成本是更大的面积、更高的功耗和更长的延迟。更糟糕的是,手动插入容易出错,并且很容易导致P&R迭代增加,尽管人们尽最大努力确保在所有相关的路径上有足够的流水线。

流水线插入的大部分复杂性都存在于NoC IP中,NoC IP连接到芯片上的绝大多数IP块。因此,它是唯一贯穿芯片的IP,所以它具有最长的导线,并且很可能通过拥塞点进行路由。它还必须在项目过程中对架构和营销引发的设计变更单(ECO)做出反应,这意味着 NoC 通常是最后一个被冻结的 IP。

物理感知 NoC IP

手动插入流水线寄存器的相关成本与快速适应不断变化的需求的需要相结合,为自动化解决方案提供了绝佳的机会。通过考虑物理需求,物理感知NoC技术可以智能插入流水线寄存器,并向布局团队建议适当的位置。第三方工具具有此功能。

首先,有必要了解有关 IP 块的相对位置和所有关联路由通道。在 SoC 开发过程的后期阶段,物理设计团队将获得有关 IP 块位置和路由通道的详细数据。在这种情况下,他们可以以库交换格式(LEF)文件和设计交换格式(DEF)文件的形式提供此信息。但是,这些数据通常无法在项目早期获得,因此能够利用任何可用的早期细节非常重要。

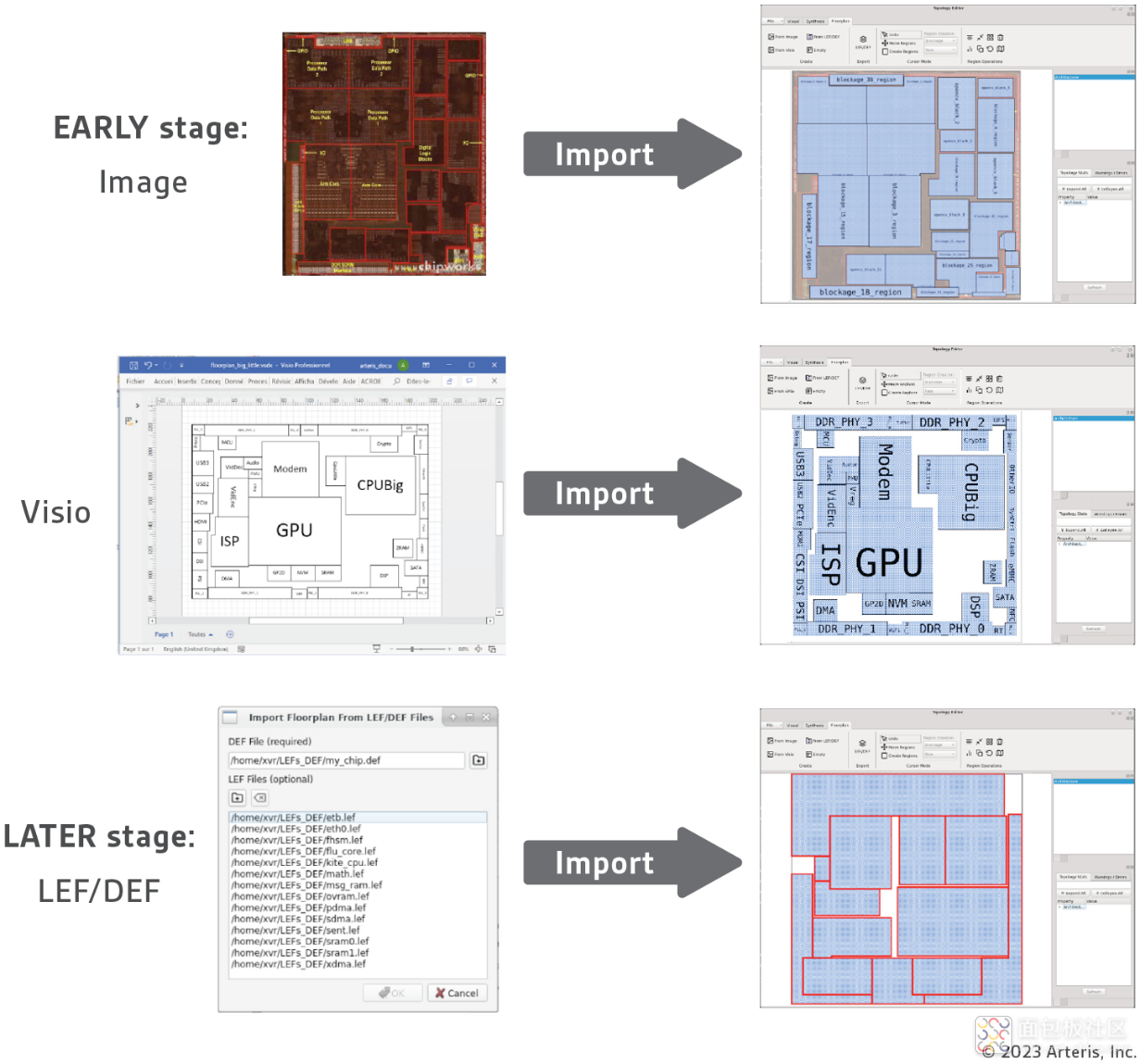

早期数据的示例包括图像、捕获 SoC 布局高级视图的 Visio 绘图或详细的 LEF/DEF 数据。第三方设计工具可以使用这些输入来建议适当的布局(图 1)。

图1. 使用 FlexNoC 设计工具的示例,该工具利用不同的布局数据源来帮助自动放置布局流水线寄存器。 (Source: Arteris, Inc.)

这些工具使用这类信息以及“速度和进给”需求,自动建议流水线寄存器的插入和位置。团队可以与工具交互协作,以试验不同的布局版位。作为这样做的回报,他们可以获得准确的时序和面积估算,并在设计流程的早期更好地了解当前NoC架构可以实现的目标。

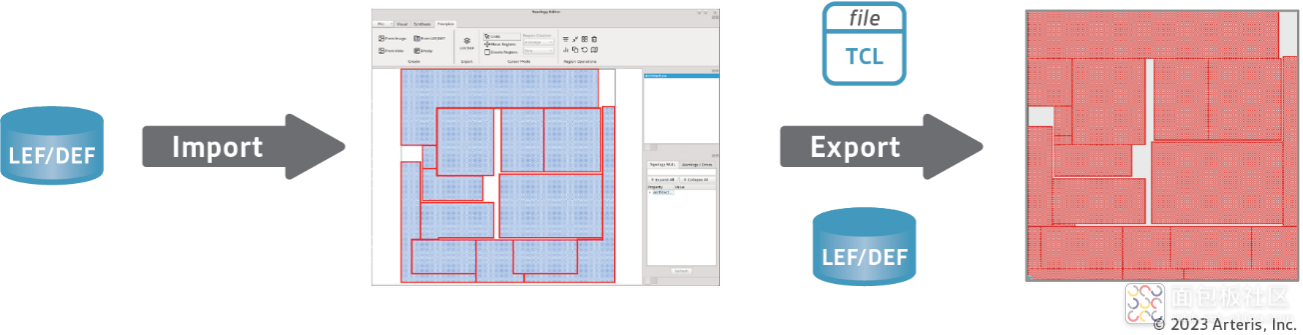

此外,第三方设计工具可以输出与NoC相关联的LEF/DEF数据,包括流水线寄存器的建议位置,以便与后端P&R工具一起使用(图2)。

图2. 使用FlexNoC设计工具的示例,该工具可以输出与NoC相关的LEF/DEF数据,包括流水线寄存器的建议位置,以便与后端P&R工具一起使用。(Source: Arteris, Inc.)

越快越好

允许团队在开发过程的前端以交互方式迭代,大大减少了时序收敛所需的后端到前端迭代次数。他们可以试验不同的NoC拓扑,并自动放置流水线寄存器,并且从面积、功耗和延迟方面评估此放置的结果。反过来,这降低了项目成本、风险和上市时间。此外,减少后端到前端迭代的次数会相应减少非重复性工程(NRE)成本,NRE成本通常在 SoC 设计周期的这一阶段达到峰值。

Andy Nightingale是一位经验丰富的全球商业领导者,在工程和产品营销方面拥有多元化的背景。他是英国计算机协会和特许营销学会的特许会员,在高科技行业拥有超过35年的经验。在他的整个职业生涯中,Andy 担任过一系列职务,包括在 Arm 担任工程和产品管理职位,他在那里工作了 23 年。Andy 目前担任 Arteris 产品营销副总裁,负责监督 Magillem SoC部署工具以及 FlexNoC 和 Ncore NoC产品。在此之前,他曾在 Arm 领导一个产品营销团队,专注于系统 IP 产品,包括网络互连、存储器和中断控制器,以及系统 MMU。

作者: ArterisIP, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3893295.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/1

/1

文章评论(0条评论)

登录后参与讨论