作者: Tim Schneider

Tim Schneider 是Arteris IP 的高级应用工程师,在与领先公司合作验证高性能系统级芯片 (SoC) 设计方面拥有超过 25 年的经验。他之前的工作包括模拟设计、逻辑、形式和硬件/软件验证,以及医疗设备行业的基于边缘的AI应用的机器视觉。 Schneider 拥有美国威奇托州立大学电子工程学士学位。

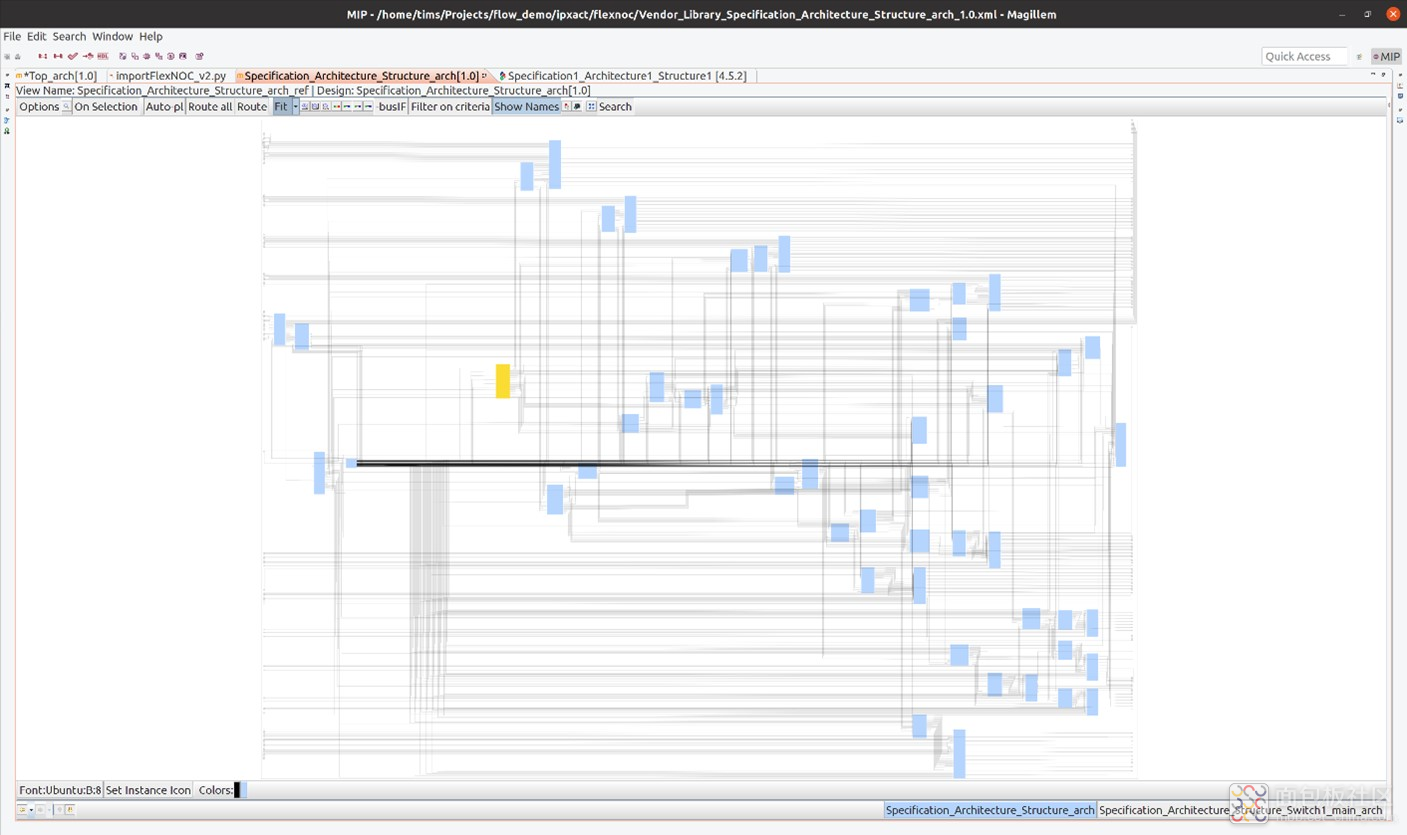

系统级芯片 (SoC) 的集成级别在 RTL 中定义,就像设计的其他部分一样。从历史上看,RTL 是通过文本编辑器构建的。然而,在十多年前,对于大型的 SoC 而言,这项任务的绝对复杂性就变得难以管理。现在,大多数 SoC 都跨越了这个门槛。这是为什么? SoC 中的 IP 数量当然是一个因素,还有就是因为集成级别的连接数量呈爆炸式增长。例如,单个AXI 通道连接可以有 25 个信号。多种风格的 AMBA 到 AMBA 连接在设计中激增。此外,设计器还必须包括集成基础结构 - 时钟、复位、电源管理和测试,这些都必须随着设计的进步而发展。在一个普通的 SoC 中,这些需求可能增加多达 10,000 个连接。 IP 之间的连接可能有数百个端口,带有多个配置绑定选项。这些端口可以保持开放或连接状态,并有许多其他重要的考虑因素。即使在设计的一个小子集中,典型的互连复杂性也是显而易见的,如图 1 所示。

图 1 使用 FlexNoC 互连的 SoC 的顶层视图。

在单个 IP 实例化可能跨越数百行的级别上,直接管理 RTL 是不可能的。这就是在过去十年中,为什么构建大型 SoC 的团队转向结构化组装方法的原因。输出仍然是相同的,是一个 RTL 顶级网表,但使用了通过抽象和自动化大规模简化任务的组装、细化和更新的工具和方法来构建。这些工具通常使用 IP-XACT 标准,这是一种最初由 Accellera 开发的基于 XML 的格式,现在被 IEEE 1685支持。

采用此流程还有许多其他附带好处,这些好处将在以后的博客中加以介绍。其中一些优势是自动为 SoC 生成完整而详细的内存映射,并且为内存映射、时钟数据和其他生成文档插入。这提供了从概念到签核的跟踪需求可追溯性。

组装 SoC

简化组装任务的核心组件是总线协议抽象,例如,AXI 总线被视为单个连接。 IP-XACT 为多种协议提供标准定义。可以对这些协议进行扩展,也可以定义新的协议或捆绑包。第二个关键组件是通过实例、端口、连接和层次结构的脚本定义实现自动化。脚本可以定义和访问比RTL 描述中常见的更丰富的属性集。这些可以包括接口的主/从类型或端口的信号类型(时钟、复位、数据等)。本文展示了 Python 脚本示例。还支持编程语言 Tcl。

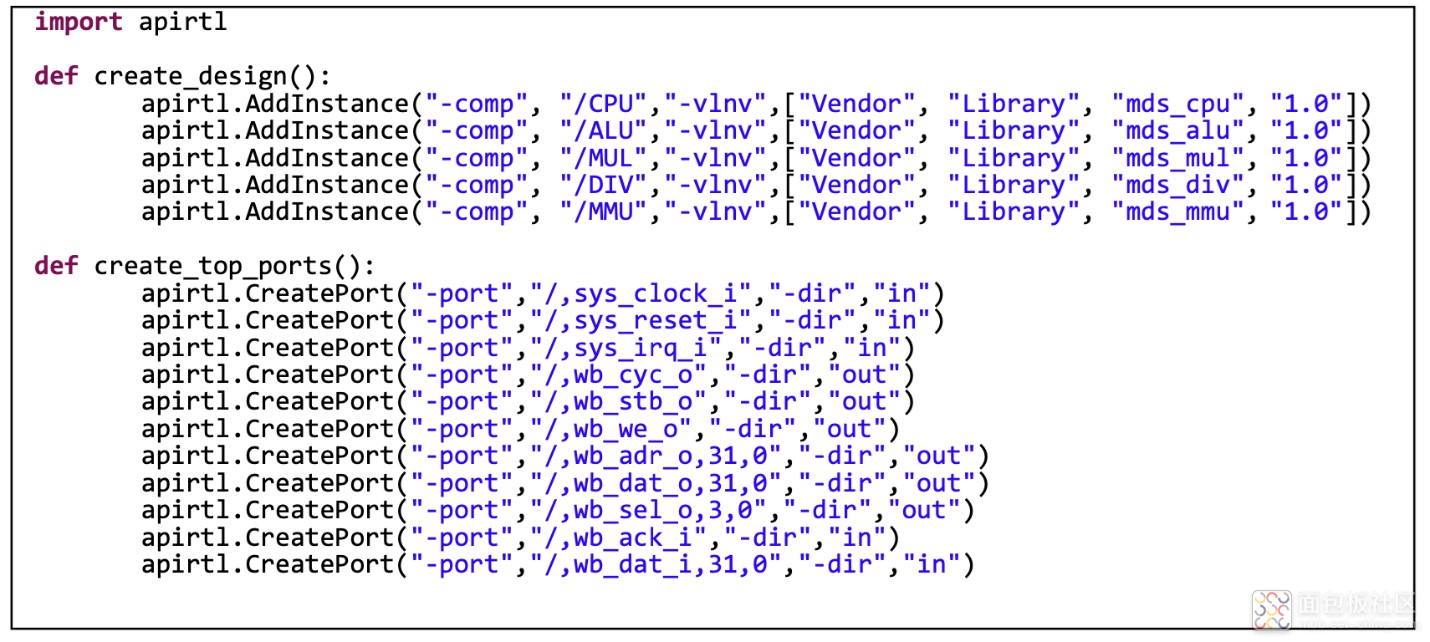

图 2 向当前设计对象添加实例和端口的功能。

这个过程很容易理解。 IPD 平台提供了丰富的 API,通过API可以创建、删除和修改对象。可以访问属性来指导脚本编写。图 2 说明了将实例和端口添加到当前设计对象的几个简单例程。

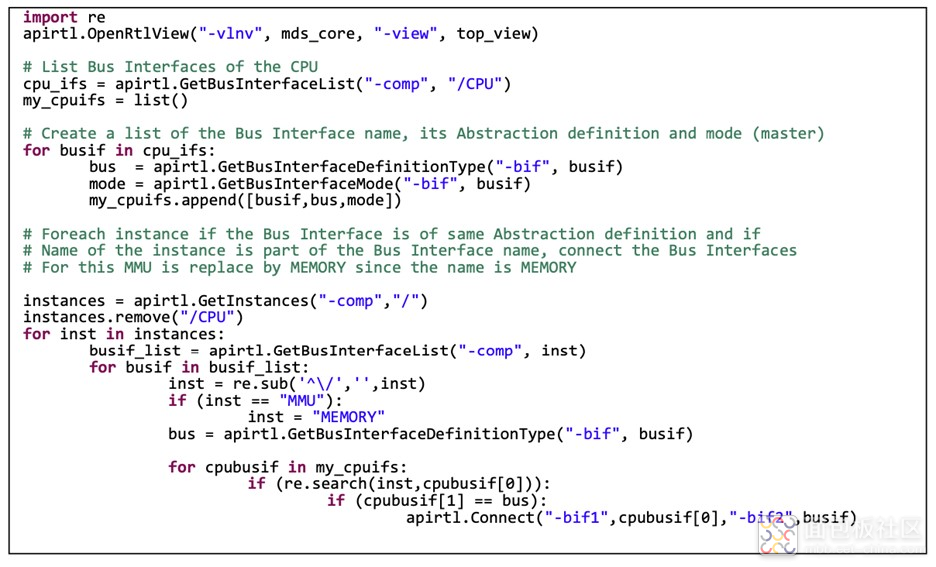

在 Python 中嵌入设计描述可实现强大的用户自定义自动化。符合程序定义的电路的任何方面都可以通过程序自动化定义,而不是通过线性实例化和连接来定义,如图 2 所示。SoC 组装中的一种常见技术是使用按名称连接,尤其是在将IP 总线接口连接到相应的总线结构实例时。图 3 显示了这种自动连接的一个示例。自动检查还可以验证这种组装过程,确保发现整个构建过程中的错误。自动执行此任务的 Python 函数非常容易定义。一个更复杂的例子可能是注入电源管理实例和连接。这是另一个对程序自动化开放的定义明确但相关的程序。最重要的是,当经过适当调试时,这些程序将不需要随着设计的发展而改变,甚至可以跨越设计家族。重要的是,程序自动化可以从 SoC 组装中抽象出功能复杂性。

图 3 自动化总线接口连接功能。

实现

Arteris IP IPD 平台支持命令行 (CLI) 或 GUI 模式。 GUI 模式在培训、审查和调试方面非常有用。 CLI 模式可能会更多地用于生产设计流程、批处理创建、回归以及持续集成和部署。本文重点将放在 CLI 模式上。可以在 CLI 命令之后,直接提供Python 脚本作为输入,以启动平台 shell程序。

脚本将为设计创建/修改/更新 IP-XACT 数据库。这些可以与其他所有的设计附属品(collateral)一起放到数据管理系统中。从 IP-XACT 数据库,可以在设计发展的任何阶段生成Verilog、SystemVerilog 或 VHDL 网表。此步骤将编写一个模拟/实现就绪的网表,直至任何叶级 IP 和一个工具命令脚本,该脚本将添加适当的库选项,以合并必要的 IP 设计 RTL。

合并遗留数据

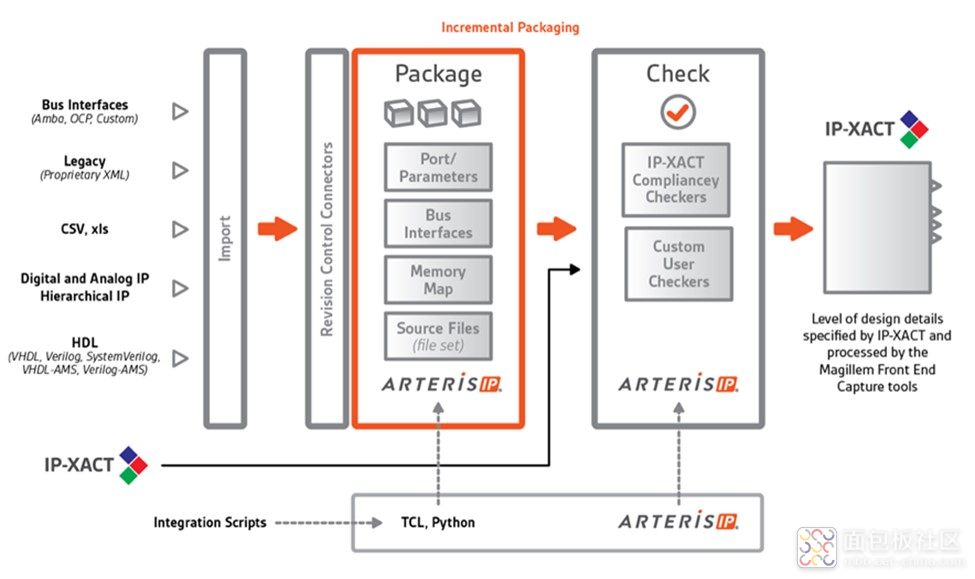

并非所有 IP 都具有 IP-XACT 模型;通常情况下,内部 IP 一般是在考虑结构化组装选项之前构建的。IPD 平台提供了一个导入选项,可以轻松地从现有的 IP 附属品(collateral)构建此类模型。

图 4 Arteris SoC 封装流程。

此选项可以读取多种格式的 RTL ,并引用 RTL 和协议接口定义构建 IP-XACT 模型。由于本地命名约定与标准命名在细节上可能有所不同,因此,此步骤通常通过 GUI 执行,允许用户指导本地端口和标准协议名称之间的映射。它还允许用户引导信号输入。输入端口不仅会处理遗留 IP;它还可以导入遗留设计,以支持结构化装配中的衍生开发。图 4 说明了此导入功能中可用的选项。

对于大多数 IP来说,从模拟命令行控件开始,会惊讶地发现,每个 IP 执行此步骤的时间超过几分钟。除非设计更改,否则导入只需执行一次。由于脚本允许自动化和更改,因此在重新导入和更新 IP 时可以减少返工。进一步的信息可以稍后添加到模型中,例如 IP 的寄存器映射。该主题将在下一篇文章中介绍。

可扩展的 SoC 组装

大多数设计团队都会认同,为 SoC 的顶层手工制作 RTL 不再实用。唯一的问题是,应该用什么来代替这种方法?内部脚本是一种早期的解决方案,但在构建和维护这些脚本时产生了更多开销。更好的方法是通过广泛采用的 IPD 平台进行集成。这为开发提供了坚实的基础,并增加了支持自动化组装的应用程序列表,同时允许在脚本差异化自动化中实现重要的设计创意。该平台为电源、内存管理单元 (MMU)、安全和安保管理的高级设计架构提供了真正的差异化支持。点击此处了解有关 Arteris IP IPD 平台的更多信息。

作者: ArterisIP, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3893295.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/2

/2

乖乖兔爸爸 2022-9-8 16:21

yzw92 2022-9-8 06:44