芯片设计中的软硬件接口概述

作者: Insaf Meliane

Insaf Meliane 是 Arteris 的产品管理和营销经理。在加入产品团队之前,她是一名现场应用经理,为客户提供复杂 SoC 设计集成支持。在加入 Arteris 之前,她曾在领先的半导体公司担任过其他设计和应用工程职务。Insaf 拥有法国格勒诺布尔国立高等电子与无线电工程学院微电子专业系统级芯片方面的工程学位。

软硬件接口 (HSI) 在芯片设计中扮演着重要角色,用于将物理硬件与其对应软件连接起来。它为复杂的系统级芯片 (SoC) 设计提供集成和性能优化。然而,软硬件接口在兼容性、时序、同步、测试、调试、性能优化、可靠性和电源管理等方面仍存在诸多挑战。

由于硬件和软件工程师沟通中使用的术语,以及各自对需求的关注点不同,软硬件接口定义之间如何平衡,本身就存在一定的挑战。

RTL 架构师面临的复杂挑战

通常说来:“如果设备要工作,驱动程序必须先正常工作。”这意味着设计人员应尽可能与 RTL 验证和软件团队协作。架构师经常发现自己处于这一挑战的最前沿。验证过程所需的时间和精力往往超过开发 RTL 本身所需的时间和精力。

软件开发始终要求将更多功能集成到硬件中。例如,软件开发人员认为“byte enables(字节使能)”是一种可以提高性能和吞吐量的功能,所以他们经常要求byte enables。这种技术是一种机制,通过这种机制,软件可以将寄存器内的操作划分为更易于管理的片段,以比整个寄存器更小的片段访问寄存器。然而,byte enables会使硬件变得更加复杂和混乱。尽管许多总线协议都支持byte enables,但这需要验证团队和 RTL 设计人员做大量工作,因此需要更多的时间来完成项目。

如果Register中某个field跨越多个字节,或者在字节不完整时跨越字节边界,这项任务的复杂性就会升级。对于在芯片设计环境中工作的人员来说,byte enables 是一项需要花费大量时间的功能。检查和设计 RTL 寄存器是一项相当大的投资,更不用说使用各种总线协议 (如 AMBA AXI、AMBA APB,有时甚至是自定义协议) 所带来的挑战。

RTL 架构师还负责创建最新的 HSI 文档,供各团队共享。此文档对于帮助其他人员了解每个字段的操作和用法至关重要,从而帮助验证团队正确验证,并帮助软件团队根据最新变化创建正确的驱动程序。随着项目的左移,他们需要确保该HSI文档准确无误并及时更新。

图 1. CSRCompiler 解决了 RTL 架构师面临的复杂挑战(来源:Arteris)

验证工程师在功能准确性方面的关键作用

验证工程师的职责是确保硬件团队提供的 RTL 在交给软件团队之前的功能性。这项任务极具挑战性,尤其是当设计中可能存在众多变量或状态空间很大时。即使是验证设计中的memory、寄存器及其域(field)也很困难。此外,随着附加功能的加入,复杂性也会增加。

除了 byte enables 和验证所有不同字节组合以确保其正常工作外,寄存器内不同字段的混合也会产生另一个问题。RTL 架构师通常会将多个域合并到一个寄存器中,以节省空间。这种做法会导致寄存器包含不同的访问类型,包括只读(read-only)、写1清 (write-one-clear) 等各种访问方法。 在同一寄存器中混合访问类型会使验证过程复杂化,增加验证难度。效率和速度是确保项目顺利通过验证阶段并按时交付给软件开发人员的关键。

与固件(Firmware)驱动程序开发人员一起优化HSI

在芯片开发过程中,固件驱动程序开发人员的任务是编写设备驱动程序。这个团队通常处于开发流程的末端,因为他们的工作要等到验证和硬件团队完成任务后才能开始。尽管为了加快这一过程shift-left方法的探究正在兴起,,目前完整的解决方案仍在制定过程中。在此之前,固件开发依然是一个瓶颈。

为了让固件开发过程更加顺利,驱动程序开发人员主张在硬件设计中采用数组(array)结构。数组可以简化软件开发,实现对寄存器和内存的直接访问。如果没有数组,软件团队必须手动创建函数和宏,才能与每个寄存器单独交互。通过采用数组结构,这些函数可以依靠简单的数学索引,从而简化整个过程。然而,并非所有硬件工程师都精通创建数组结构。

改变游戏规则的解决方案

CSRCompiler 技术是应对设计团队面临的挑战和不同要求的解决方案之一。Arteris 提供了一种可扩展的强大方法,可实现 HSI 设计、验证、固件和文档等所有方面的自动化。整个设计团队可以从单一来源获得地址映射信息。该信息以多种视图提供。每个团队成员都能以所需的格式访问信息。

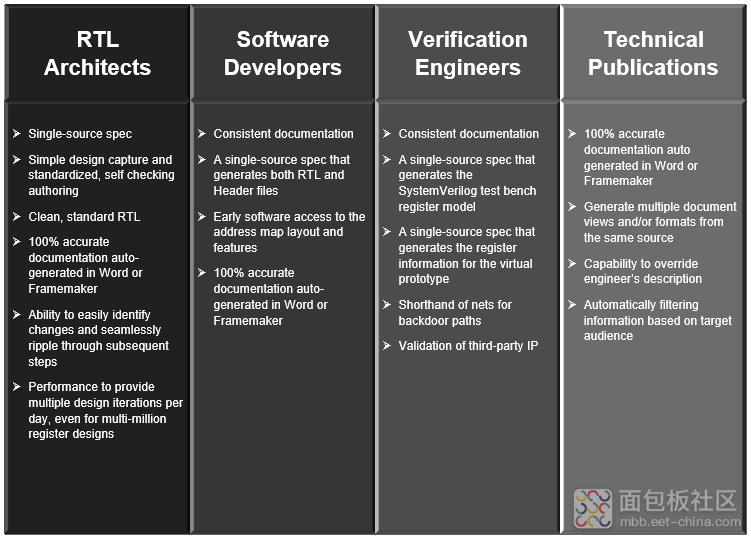

图 2. 团队成员通过 CSRCompiler 获得的收益 (来源:Arteris)

简化设计团队之间的交付流程

随着半导体芯片设计领域不断演进,团队之间必须进行有效沟通。HSI充当了沟通的桥梁,尽管由于语言和要求的不同,仍然存在一些挑战,但 Arteris 的 CSRCompiler 等工具简化了这一流程。

CSRCompiler 方法可文档化记录这些变更,确保团队间基于稳定可靠的、最新的HIS规格来协同工作。它为寄存器和memory-map信息提供单一来源的规范,并按照所有团队所需的格式和视图进行了全面配置。

作者: ArterisIP, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3893295.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

文章评论(0条评论)

登录后参与讨论