NoC的下一步发展是什么?

作者: Andy Nightingale

Andy Nightingale 是 Arteris 产品管理和营销副总裁,拥有超过 37 年的高科技行业经验,其中包括在 Arm 担任各种工程和产品管理职位 23 年。

Andy Nightingale 是 Arteris 产品管理和营销副总裁,拥有超过 37 年的高科技行业经验,其中包括在 Arm 担任各种工程和产品管理职位 23 年。

当今的高端 SoC 在很大程度上依赖复杂的片上网络(NoC)技术来实现性能和可扩展性。随着 人工智能(AI)、高性能计算(HPC)和其他计算密集型应用的需求不断发展,设计下一代 SoC 将需要更智能、更高效的 NoC 解决方案来应对这些挑战。

尽管这些进步带来了令人兴奋的机会,但也带来了巨大的挑战。SoC 设计人员面临着架构快速扩展、上市时间压力、专业知识稀缺、资源利用率低下以及工具链差异等诸多挑战。

SoC复杂性呈指数级增长

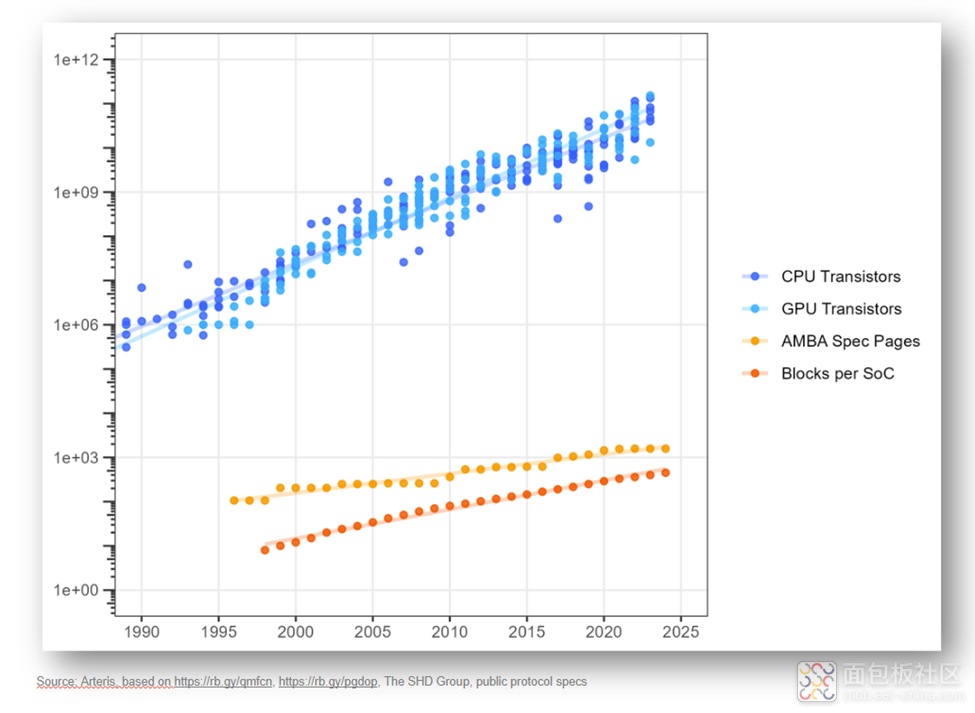

在工艺技术和设计工具进步的推动下,SoC 设计已经达到了前所未有的复杂程度。现在,SoC 通常包括 50 到 500多个 个 IP 模块,从处理器内核和内存控制器到用于 AI 和图形的专用加速器,应有尽有。这些模块过去仅包含数万个晶体管,而现在每个模块包含从100 万到超过 10 亿个晶体管。因此,这些 SoC 集成的晶体管总数达到惊人的 10 亿到超过 1000 亿个,反映了其规模和复杂性的指数级增长,如图 1 所示。

图 1. 晶体管预算增加与使用 SIP 模块之间的关系。(Source: Arteris, 基于 SHD 集团的公共协议规范 https://rb.gy/qmfcn 和 https://rb.gy/pgdop. )

IP 模块和晶体管密度的增长使具有多个处理器集群的高级架构的发展成为可能。在主流设计中,每个集群通常最多包含 8 个或更多内核,高性能配置达到 32 个或更多内核。如今,这些集群被组织成数组以提供大规模并行处理能力。这些尖端设计集成了高带宽内存控制器、专用 AI 加速器和复杂的 NoC 互连系统,以确保无缝通信和可扩展性。

使用先进的 NoC 互连技术可以应对这一前所未有的挑战,NoC 互连是芯片内高效数据传输和通信的骨干。这些片上网络可以实现众多 IP 模块的无缝集成。高端 SoC 通常依赖于多个 NoC,每个 NoC 都针对特定任务或子系统量身定制,以处理不同芯片区域的各种通信需求。这些 NoC 可根据应用需求采用多种拓扑结构,例如用于低延迟通信的环形结构、用于层次化组织的树形结构以及用于可扩展性和灵活性的网状拓扑结构。

为了应对这些密度和性能挑战,3D 堆叠技术正越来越多地被采用。与传统的 2D 设计相比,这些方法垂直集成了多层逻辑和存储器,从而实现了更高的带宽并降低了延迟。然而,3D 堆叠在 NoC 设计中引入了额外的复杂性,例如需要管理层间通信和热约束,这也需要创新的互连解决方案。

其他挑战

SoC 设计日趋复杂,市场的快速发展带来了更多挑战。随着架构变得越来越复杂,设计人员面临着越来越大的压力,他们必须克服这些障碍,采用创新的解决方案,努力跟上行业需求的步伐。

这些挑战可以总结如下:

应对这些挑战需要采用自动化设计方法,增强员工专业知识,并整合工具链以简化工作流程并提高效率。

设计人员需要更智能的NoC解决方案

新一轮 SoC 设计复杂性的压力正在将设计团队推向极限。应对这些挑战的有效方法是将设计划分为更小、更易于管理的部分,将其分为 IP 模块。这种方法在简化单个设计任务的同时,也带来一个新的挑战,那就是如何确保无缝集成这些模块,以形成一个功能齐全、经过优化的 SoC。 集成过程经常会出现一些意想不到的问题,如接口不匹配、时序冲突和资源争用等,这些问题会严重影响性能并延迟产品上市时间。

随着 SoC 设计采用AI加速器和高级互连系统等日益复杂的组件,集成挑战变得更加突出。例如,神经处理器单元(NPU)和 NoC 技术的发展突显了 SoC 架构复杂性的快速增长。最早的 NPU 通常以乘法累加 (MAC) 函数阵列的形式实现。相比之下,如今的 NPU 要先进得多,可以作为处理部件 (PE) 阵列来实现,所有处理部件都由各自的网状拓扑 NoC 链接。

同样,NoC 技术也取得了显著进步。第一代 NoC 需要手动布局和实现,包括插入流水线阶段(insertion of pipeline stage)。后来的 NoC 技术则引入了物理感知技术,允许自动生成 NoC 和自动插入流水线阶段。

最新一代的 NoC 支持更高端的功能,例如软瓦格化(tiling)。该技术包括处理单元(PU)的自动复制,例如高级 SoC 中的处理器集群(PC)或 NPU 中的处理部件(PE)。它还会自动生成 NoC,并为与每个 PU 关联的网络接口单元(NIU)自动配置唯一地址。物理感知和 NoC 软瓦格化等功能大大提高了生产率、缩短了产品上市时间并降低了风险。然而,随着设计复杂性的不断增长,需要更多的进步来应对新出现的挑战。

为SoC设计的未来做准备

成功实现下一代器件变得越来越困难,尤其是当涉及到将所有 IP 集成到完整的 SoC 中时。目前显然需要对工具(包括 NoC 技术)进行改进,以满足市场变化带来的不断扩大的需求,例如:

为工程师提供用户友好的界面和灵活的工作流程,支持增量更新和与现有工具链的集成。

当具备这些功能的 NoC 工具和技术问世时,SoC 设计人员将能够以更高的效率和创新能力来满足这些不断升级的设计需求。下一代 NoC 解决方案的设计必须既能应对当今的挑战,又能预见未来 SoC 设计日益增长的需求。

作者: ArterisIP, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3893295.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论