2 端接的策略

2.1 末端端接

2.1.1末端端接的特点

根据电缆末端电压的函数,可以得到末端端接的特性

(1)驱动波形以满幅度沿着整个电缆的路径传播

(2)所有的反射都被末端的端接电阻衰减

(3)接收到的电压等于传输电压

2.1.2末端端接的上升时间

考虑末端端接对上升时间的影响

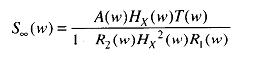

频率响应模型:

分子是减号。其中,T(w)= R2(w)+1。

A.假设传输线的长度超过上升沿的长度,这样即可忽略从末端端接器反弹的反射。因为在第一个上升沿完成整个过程之前,末端反射没有足够的时间到达源端,这样就不影响最初的上升波形。 这样,在数学上,可以强迫R1(w)=0。

B. 假设驱动阻抗小于传输线的阻抗这样可以使A(w)归一化。

C. 进一步假设电路长度不足以使信号分散,从而使H(w)归一化,即没有衰减。

最后得到S(w)= R2(w)+1,因为R2(w)=(ZL-Z0)/(ZL+Z0),则S(w)=2ZL/(ZL+Z0)=2/(1+Z0/ZL)

D. 进一步,把特性阻抗Z0(w)简化为常数阻抗Z0,而ZL是由端接电阻(Z0)和门电路的输入负载并联的,1/ZL=jwC+1/Z0

最后得到:S(w)=2/(1+Z0(1/Z0+jwC))=1/(1+jwCZ0/2)

这是一个RC滤波器的模型,时间常数t=Z0C/2,上升时间Tr=2.2t=1.1CZ0。如果驱动电路的上升时间是t1,则接收电路的上升时间是T=sqrt(t1^2+Tr^2),当传输线很长,超过上升沿的长度,它的输出有效阻抗就是Z0,如果缩短传输线使之接近上升沿的长度,阻抗就降低,(因为线路越短,驱动端就越快的感受到负载的存在(即传输线的影响减小),最终,线很短的时候,驱动端直接就感受到了负载而感受不到传输线的存在,这样,相当于驱动阻抗就降低为驱动阻抗Rs,这样,相当于阻抗就降低了),当走线很短的时候,接收电路的上升时间就等于驱动电路的上升时间,因此会得到一个比较快的上升时间。

2.1.3 末端端接器的直流偏置

实际中的TTL或CMOS电路很少使用末端端接的方案,因为在这样的电路中,高电平下需要提供很大的驱动电流;比如5V驱动65欧传输线,当输出跳变为Vcc时,它必须向末端端接器提供5/65=76mA的电流,很少有驱动器能够提供这么大的电流。可以采用一个改善的端接方案是,分离(split)端接。

将末端端接器变化为戴维南等效电路。选择R1R2的约束条件是

(1) R1//R2 =Z0

(2) 不能超过IoHmax(最大的高电平输出电流)

(3) 不能超过IoLmax(最大的低电平输出电流)

这三个约束条件给出的方程组是:

Z0=R1//R2

VoH/R2 - (Vcc-VoH)/R1 < IoH

(Vcc-VoL)/R1- VoL/R2 < IoL

解出R1,R2得到split端接的值。这里,忽略了输入门的电流,因为CMOS电路理论上的输入电流为0。有时候,这组方程不一定能够给出一个解,这时,就找不到一个合适的端接的阻值。末端端接可以只使用一个端接电阻端接到一个固定的中间电压。如何求解这个固定电压呢?可以先设计一个分离的端接网络,求出分离端接的戴维南等效电压源,这个等效源的输出阻抗是Z0,等效电压源就是端接电压——V端接=Vcc*R2/(R1+R2)。

/4

/4

文章评论(0条评论)

登录后参与讨论