4 总线的topology结构

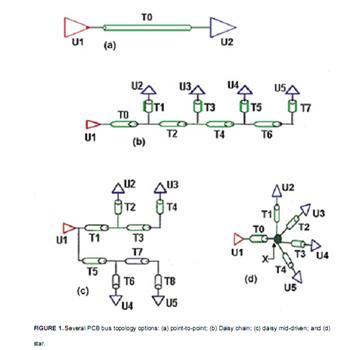

常见的topology结构主要有以下几种:point-to-point, daisy-chain, star, Tee, multi-drop.

multi-drop和daisy-chain类似,也可以看成一种。在这些拓扑结构中,总线的类型有分为uni-direction和bi-direction。单向总线简单,而双向的总线复杂一些。有时候,需要把几个网络连接在一起,而网络上的器件有时tri-state,既能输入,又能输出。这种情况下,需要仔细选取端接的方案。

5 端接方案的选择和比较

5.1 端接策略的选择[1][2][4][6][7][8][9]

阻抗控制一般都在+-15%,阻抗的变化对源端端接的影响更大。对于短线(short line),最小的脉冲宽度接近传输线的延时的时候,选择源端端接更好;对于长线,脉冲宽度比传输线的延时小很多,负载端接(load termination)更为有效。因为可能有多个信号往返与传输线,负载端的反射会返回源端,与传播的信号发生干扰,所以,反射必须在负载端消除。

长线短线的定义在[4],pp-46.这里的短线与前面提到的短线的概念是不一样的。长线定义为传输线的延时至少是信号上升时间(或下降时间)的一半。For a truly long line, one where the ratio of (line delay)/(signal risetime) is greater than 1[10].

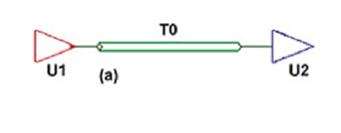

5.2 Point-point

5.2.1 uni-direction Point-point

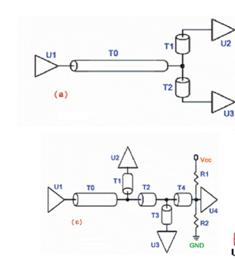

这是最简单的总线布置。最好的方式是源端端接。A point-to-point connection between two components produces optimum signal quality。

5.2.2 bi-direction Point-point

这种情况,总线两端的器件都能驱动总线。总线的结构可以表示为[12]:

[XCVR A]--[resistor B]--[C--long line--D]--[resistor E]--[XCVR F].

可以采取源端端接的方案。两端的串联电阻加上各自驱动器的输出阻抗,都应该等于传输线的阻抗。

当一端的器件驱动总线时,源端得到匹配,在负载端,上升时间会比正常源端端接时的上升时间滞后,这是由于额外的端接电阻造成的。正常的源端端接电路,得到的Rc时间常数是Z0C,Z0是线路阻抗,C是负载电容;双向源端短接後,Rc时间常数是(Z0+Rs)C。两个PCI器件的互联可以采用这种方式。

/4

/4

文章评论(0条评论)

登录后参与讨论