2.4 二极管端接

2.4.1 二极管端接的原理

二极管的偏置电压是Vt,二极管工作在反向偏置的状态,仅有极少量的漏电流流过。因此没有静态功耗。当负载处的电压Vin>Vdd+Vt时,二极管正向偏置,线路上的电压被钳为在V=Vdd+Vt。同理,当电压下降到VSS-Vt的时候(一个负的下冲),下边的二极管开启,相当于一个电阻的作用,传输线实际上就被这个电阻端接。二极管实际上不吸收任何能量,它只是把过冲和下冲偏置到电源或地。

可以用数学来表示上述的关系。假设发送到线路上的初始电压是I,负载处的电压是T,负载处的反射电压是R,那么,这三者可以表示为T=I+R。即R=T-I。如果二极管把电压钳位在Vdd,而初始发射电压也是Vdd的话,反射电压R实际上等于0!。如果I小于T的话,R就不为0,得到一个反射电压,也就是说,二极管端接只能衰减第一次的入射波(大于Vdd+Vt或等于Vdd)。由于二极管不吸收能量,剩余的反射只能依靠线路的电阻衰减。二极管的端接性能取决于它的开启时间,正向偏置电压,和反向恢复时间。

Higher turn-on time, ton, results in undershoot. Higher forward-bias voltage. Higher forward-bias voltage Vff, causes time jitter. Higher reverse-recovery time, trr, increases the rise time, tr, of the signal. Thus, you can pre-serve signal integrity by using a diode that has a small ton, Vff, and trr as a termination device. A Schottky diode possesses these characteristics.[8]

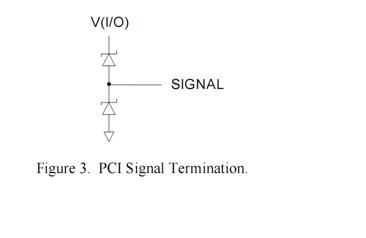

2.4.2 二极管端接的实例

CPCI的背板设计中,CPCI规范指出了对于强驱动和轻负载的情况,可以使用二极管端接(TI-74S1053).

For this specific system configuration, fast Schottky diode signal termination (For example: see Texas Instruments 74S1053 diode array) shall be added to the end of the backplane furthest from the System Slot on all bused PCI signals, as illustrated in Figure 3. The diodes may be added directly to the backplane or via a diode termination board in the slot furthest away from the System Slot. If used, the diodes shall be as near as practical to the end of the net for each PCI signal.

3 端接的功耗分析[1][2][3]

3.1 源端端接功耗

3.1.1源端端接的驱动电流

源端端接总的阻抗是特性阻抗的2倍。因此,当门电路跳变的时候,驱动电流是V/2Z0,这个驱动电流在2TD时间之后变为0(这时,从末端发射的电压返回到源端并被端接电阻吸收)。如果信号跳变很少(也就是不频繁),平均电流会很小,但峰值电流还是V/2Z0。对于快速跳变的电路,在反射电压返回源端之间,下一个跳变就开始了,这时候,需要驱动器持续提供峰值电流。

3.1.2源端端接的功耗

在2TD的时间内,驱动电流是V/2Z0,电压是v/2,因此,2TD期间,端接电阻上的能量是 E="2TD"*(v/2)^2*(1/R).

3.2 末端端接功耗

3.2.1不同末端端接的功耗

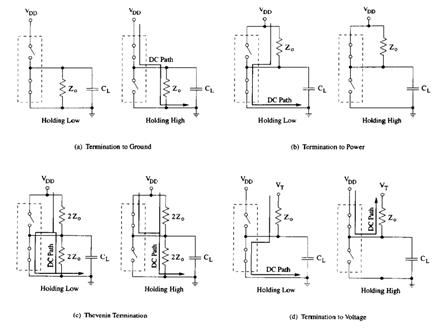

末端端接有几种不同的形式,直接端接到GND,split端接,或split端接的Thevenin等效(即端接到一个固定的电压)。

对于split端接,即使没有状态转换,末端端接也要消耗功率。如果状态在HI和LO的时间基本相当,末端端接的功耗是[1]:

对于R1=R2=2Z0 的端接情况,如果高电平和低电平之间的电压差为V,那么,端接电阻的平均功耗是,V^2/2Z0。

下图是不同的末端端接的功耗比较[3],假设传输线的特性阻抗都是Z0,输出阻抗是R。

对于(a)的情况,在HI状态,静态功耗是:Vdd^2/(R+Z0) ,在LO状态,功耗为0。很明显,直接端接到GND或VCC的缺点是,驱动电路必须能够驱动足够的电流,a中,需要提供Vdd/(R+Z0)。

如果端接到Vdd,如在(b)中,下边的晶体管需要流过同样大的电流。

对于(c)的thevenin电路,功耗则为:VDD2 /(2Z0+R//2Z0),需要的驱动电流是,Vcc/(2(R+Z0))。

对于(d),采用了另外一种方法,端接到一个中间的电压值。Thevenin的等效电压源Vt=VDD/2。功耗是,VDD2 /4(R+Z0),驱动电流是VDD/2(R+Z0).这种端接的主要缺点是需要一个良好的低阻抗的电压源VDD/2,即需要提供一个端接电压,同时,这个电压源还必须能够source和sink电流。

3.2.2 末端端接的电压摆幅[3]

/4

/4

文章评论(0条评论)

登录后参与讨论