[1] 压降

(1)什么是压降?

压降电压 VDO 是指为实现正常稳压,输入电压 VIN 必须高出所需输出电压 VOUT(nom) 的最小压差。

(2)决定压降的因素是什么?

压降主要由 LDO 架构决定。

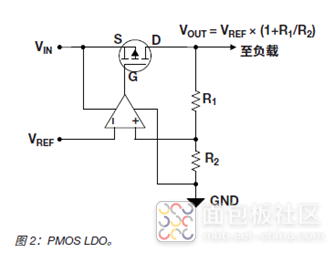

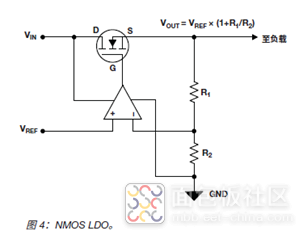

为说明原因,让我们来了解一下 P 沟道金属氧化物半导体(PMOS) 和 N 沟道 MOS (NMOS) LDO,并对比其工作情况。

A: PMOS型号LDO在特定的点,误差放大器输出将在接地端达到饱和状态(不能小于GND),无法驱动 VGS 进一步负向增大。通过提升输入电压,可以使 VGS 值负向增大。因此,PMOS 架构在较高的输出电压下具有较低的压降。

B: NMOS型号LDO在特定的点,VGS 无法再升高,因为误差放大器输出在电源电压 VIN 下将达到饱和状态。

C: 其他因素

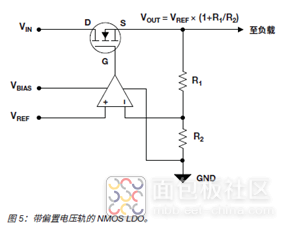

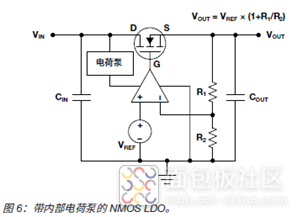

(3)如何降低压降

通过辅助电源轨或者电荷泵来提高误差放大器输出的Vgs来降低Vdrop

本人学习笔记公众号,将在上面分享学习记录与心得:

公众号名称:硬件之路学习笔记

作者: 硬件之路学习笔记, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3966341.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论