图1:静电导致晶体管Gate oxide膜层的击穿失效表征-漏电流过大

图2: 集成电路制造后段wafer sawing工序的rinsing过程的静电导致绝缘膜层punch through的损坏情形

集成电路微电子器件制造中静电产生,主要来自取各制程设备操作与生产工序的相关过程,主要表现在:

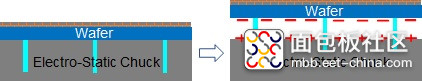

1.物体间的接触-分离静电起电,如wafer在各种制程设备中wafer在ESC(Electro-Static Chuck)上的loading与lift up操作,又如PR(Photo Resist)coating过程中wafer的静电累积,再如wafer在spin drying过程中的静电起电与累积等;

2.真空制程设备中的RF plasma作用使wafer膜层上累积静电,CVD,PVD,DET;

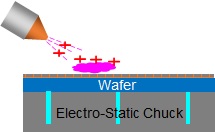

3.高压rinsing过程wafer上的静电带电与静电累积等;

4.封装阶段wafer切割blue tape的贴膜与撕膜过程的静电在wafer上的产生与累积。

5.其他制程设备中的静电产生情形。

图3:wafer在ESC上的静电起电情形

图4:wafer在高压rinsing过程中的静电带电情形

静电导致集成电路微电子器件发生功能不良(功能失效及电气可靠性下降),主要表现为wafer上方的静电累积过高导致绝缘膜层电性损坏(集中于wafer Fab阶段的制程设备与生产工序中),与静电放电(Electro-Static Discharge,ESD)过程产生的快速电流脉冲stress绝缘介质膜层引发击穿失效(主要发生于wafer的probing test,封装测试阶段的die bond、wire bond及各种电性测试工序)。

图5:wafer上方的静电累积导致die电性不良的情形

图6:Wafer/IC高静电带电后在电性测试工序发生ESD的电气失效情形

作者: Copper_Hou, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3980254.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/2

/2

文章评论(0条评论)

登录后参与讨论