原创

芯片封测工厂中自动化测试设备中的静电CDM ESD导致的芯片电性失效简介

关键词:

ATE,Automated Test Equipment,自动化测试设备

CDM,Charged Device Model,至微电子器件带静电后,与接地的导体发生接触,而产生的剧烈静电放电事件

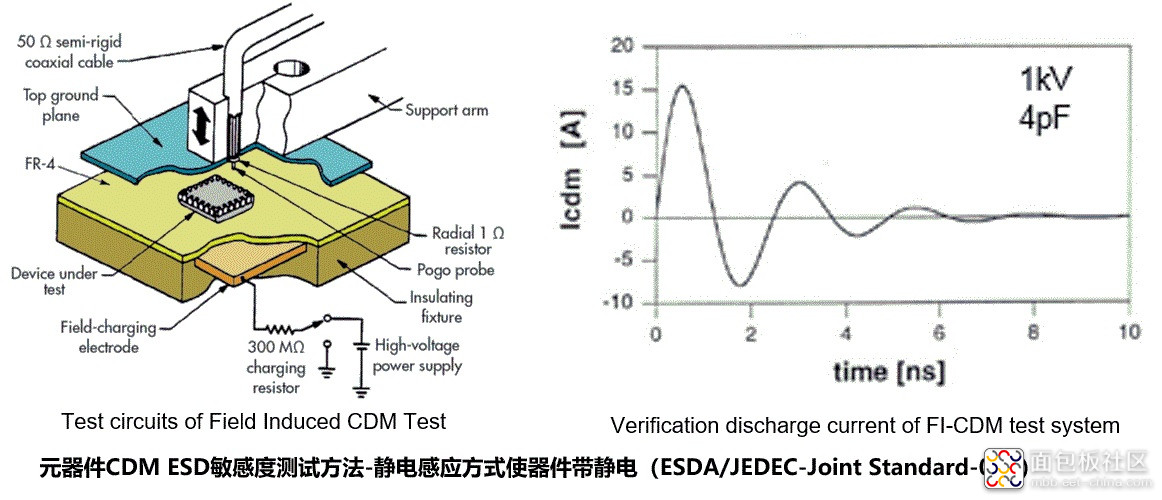

Field-Induced CDM,静电感应方式使电子器件带静电的CDM情形

ESD,Electro-Static Discharge,静电放电,

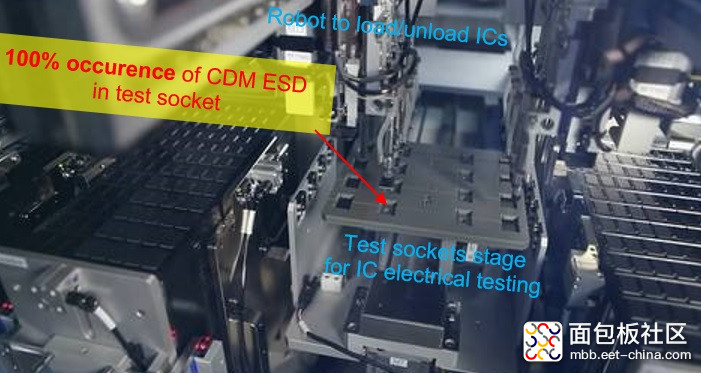

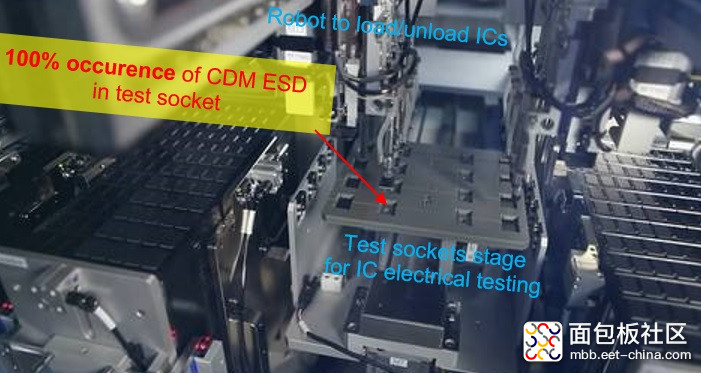

芯片封测工厂中末段的许多自动化电性测试设备(ATE,Automated Test Equipment:涉及DC参数测试、open/short测试、functional测试、烧录等)都存在共同的ESD失效风险:处于高静电带电状态的IC接触到测试机的测试pin发生剧烈的静电放电,产生快速放电脉冲冲击IC内部器件结构,并导致相应的电性参数失效。芯片在ATE设备上是否会产生电气失效,主要取决于:1.芯片的ESD敏感等级(也就是芯片能够承受的最大CDM电压水平);2.芯片在ATE设备中的最高静电带电水平(取决于的芯片的封装材质与ATE设备的自动化设定技术条件)。

关于芯片封测工厂的ESD失效问题,现实中代表性的ESD现象主要包括:1.同一批生产的芯片在不同ATE设备上的电性不良率呈现差异(表明不同ATE设备的ESD防护有效性存在差异);2.同一批生产的芯片经过ATE测试会比未进行ATE测试的出现较高的电性不良品(充分表明ATE设备的ESD防护不到位);3.ATE设备测试判定为良品的芯片再次进行ATE测试仍会再次出现电性不良品(表明前面的ATE设备在测试座取出芯片发生了ESD失效,或后面的ATE设备的ESD防护不到位)。

芯片在ATE设备中的静电带电来源,主要包括:

1.搬运robot真空吸嘴取放芯片在芯片绝缘封装壳体上累积静电;

2.芯片在test socket中loading/unloading过程,导致test socket的芯片导向部件累积静电。

解决芯片在ATE设备中的ESD失效,关键在于芯片在自动取放过程中的静电带电水平是否可以控制到位,具体可以通过ATE相关取放机构的ESD改造及芯片在测试座区域的取放过程的离子化静电消除等技术手段来实现。

附件:微电子器件的(Field Induced)CDM ESD敏感度评测方法

作者: Copper_Hou, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3980254.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/1

/1

文章评论(0条评论)

登录后参与讨论