1、例程目的

基于Xines广州星嵌电子Xilinx XC7Z035/45-2FFG676I 平台的Zynq7035/45 PL端高速串行接口,使用千兆以太网通讯方式来测试验证底板上的光口通信,实现以下以太网功能:

1) 支持IP、UDP协议,实现UDP数据收发;

2) 支持ARP、ICMP协议,实现PING功能。

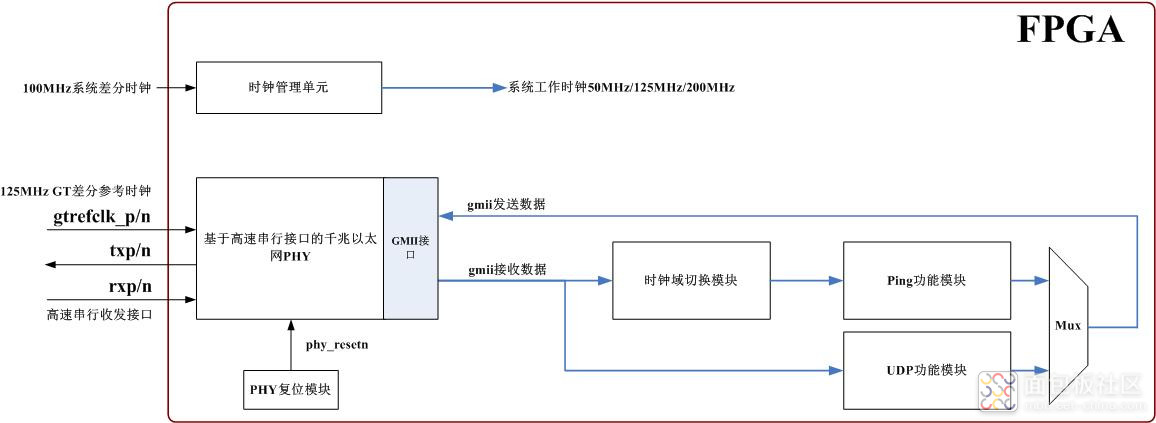

图1例程设计框图

1 | 时钟管理单元 | 为例程提供时钟源; |

2 | 基于高速串行接口的千兆以太网PHY | 以太网PHY,本地为GMII接口,对外是高速串行接口,可对接光口转RJ45模块,连接到外部以太网; |

3 | 时钟域切换模块 | gmii接收数据时钟域切换,ping功能模块收发数据要求在同一个时钟域; |

4 | Ping功能模块 | 支持ARP、ICMP协议,实现以太网PING功能; |

5 | UDP功能模块 | 支持IP、UDP协议,实现UDP数据收发功能; |

6 | MUX复用器 | ping功能模块和UDP功能模块各自gmii发送数据复用输出; |

7 | PHY复位模块 | 以太网PHY复位控制; |

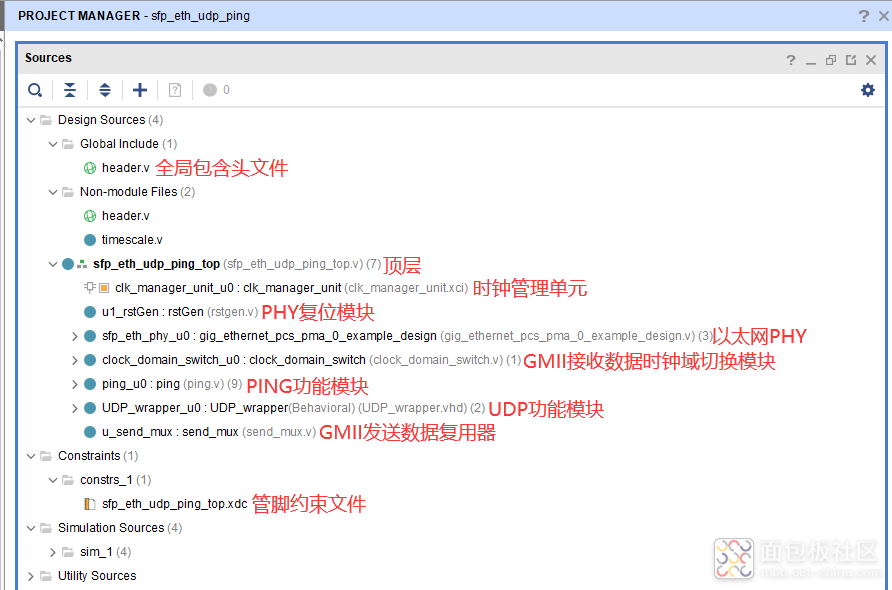

图2例程文件结构

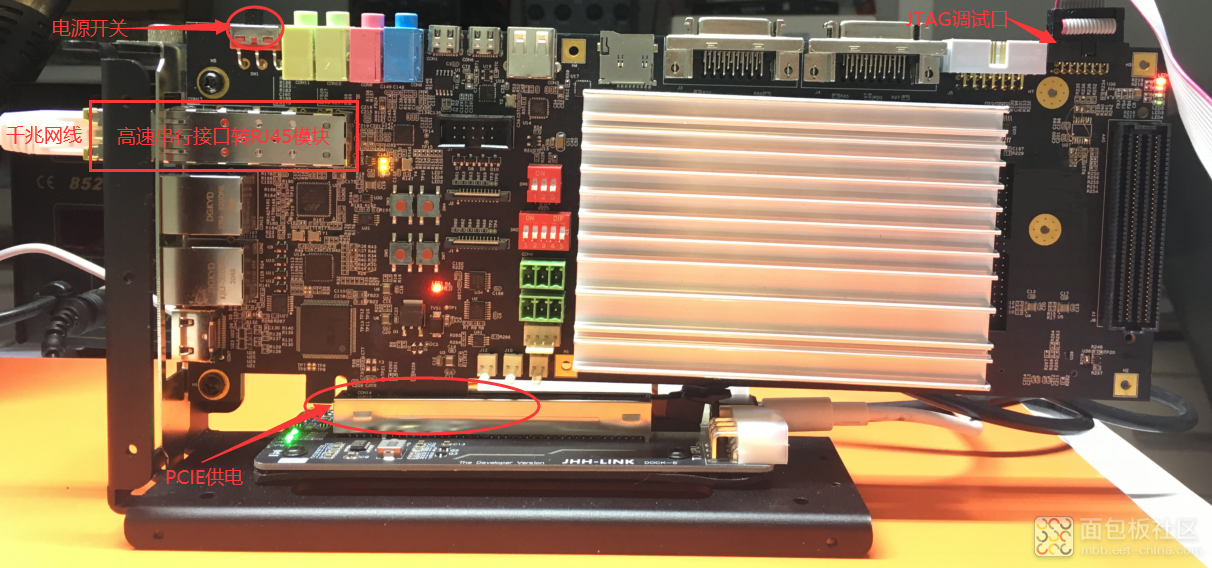

1)使用PCIE供电,连接FPGA JTAG下载线至JTAG调试口,将高速串行接口转RJ45模块插入光口笼子里面,并用千兆网线连接至PC电脑:

XQ6657Z35-EVM连接示意图

2)打开电源开关。

4.2测试

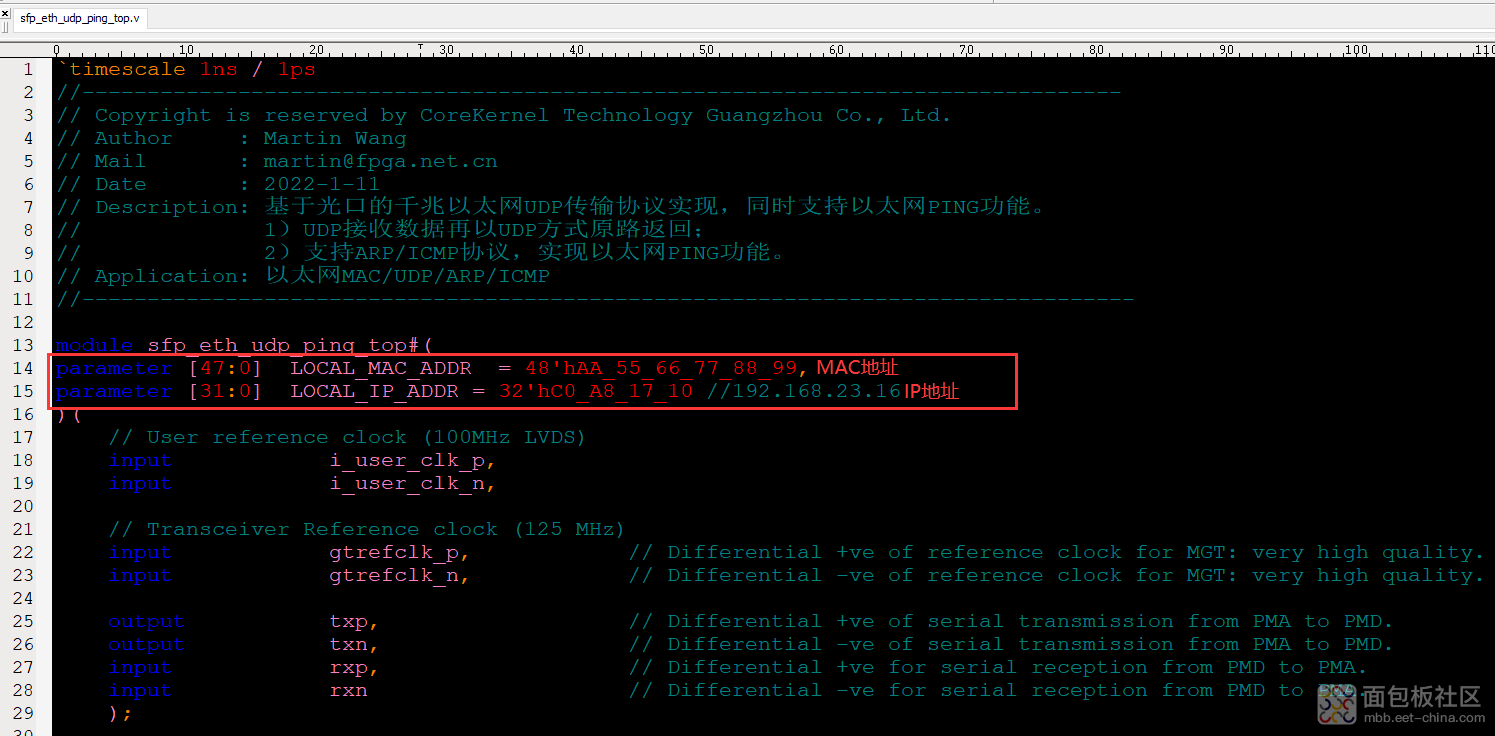

1)本地MAC和IP地址:

2)测试环境:DSP+ZYNQ评估板 XQ6657Z35-EVM

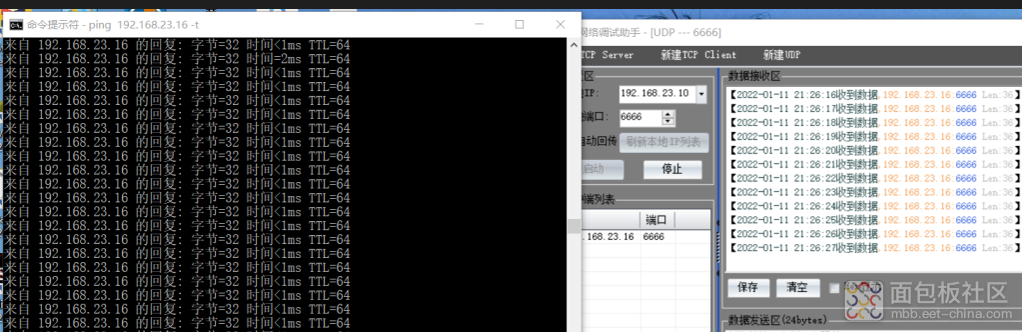

3)同时进行ping操作和UDP数据收发功能正常:

(以上实验数据基于XQ6657Z35-EVM评估板硬件平台测试结果)

USB TYPE-C/PCIe供电,12V@4A

5.2开发资料

序号 | 提供资料 |

1 | 核心板引脚定义说明; |

2 | 可编辑底板原理图、可编辑底板PCB、芯片Datasheet; |

3 | 提供Zynq与DSP通过SRIO、EMIF16、SPI等相关通讯例程; |

作者:王忠亮

/2

/2

文章评论(0条评论)

登录后参与讨论