本文主要分析MII/RMII/SMII,以及GMII/RGMII/SGMII接口的信号定义,及相关知识,同时本文也对RJ-45接口进行了总结,分析了在10/100模式下和1000M模式下的设计方法。

MII接口提供了MAC与PHY之间、PHY与STA(Station Management)之间的互联技术,该接口支持10Mb/s与100Mb/s的数据传输速率,数据传输的位宽为4位。

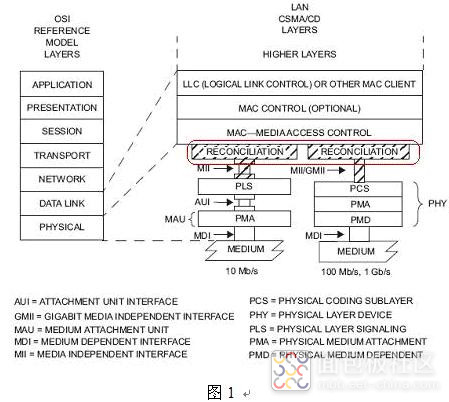

提到MII,就有可能涉及到RS,PLS,STA等名词术语,下面讲一下他们之间对应的关系。所谓RS即Reconciliation sublayer,它的主要功能主要是提供一种MII和MAC/PLS之间的信号映射机制。

RS与MII之间的关系如下图:

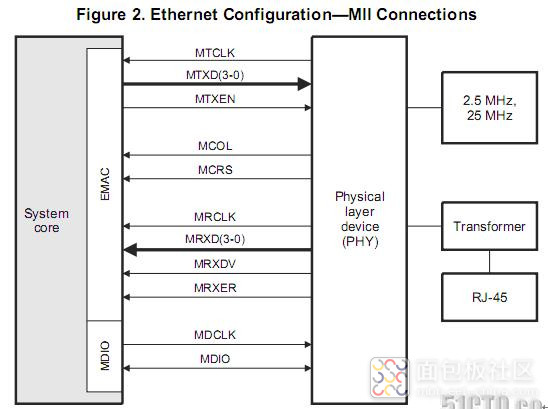

MII接口的Management Interface可同时控制多个PHY,802.3协议最多支持32个PHY,但有一定的限制:要符合协议要求的connector特性。所谓Management Interface,即MDC信号和MDIO信号。

前面已经讲过RS与PLS的关系,以及MII接口连接的对象。它们是通过MII接口进行连接的,示意图如下图。由图可知,MII的Management Interface是与STA(Station Management)相连的。

接口支持10Mb/s以及100Mb/s,且在两种工作模式下所有的功能以及时序关系都是一致的,唯一不同的是时钟的频率问题。802.3要求PHY不一定一定要支持这两种速率,但一定要描述,通过Management Interface反馈给MAC。

下面将详细介绍MII接口的信号定义,时序特性等。由于MII接口有MAC和PHY模式,因此,将会根据这两种不同的模式进行分析,同时还会对RMII/SMII进行介绍。

MII接口可分为MAC模式和PHY模式,一般说来MAC和PHY对接,但是MAC和MAC也是可以对接的。

以前的10M的MAC层芯片和物理层芯片之间传送数据是通过一根数据线来进行的,其时钟是10M,在100M中,如果也用一根数据线来传送的话,时钟需要100M,这会带来一些问题,所以定义了MII接口,它是用4根数据线来传送数据的,这样在传送100M数据时,时钟就会由100M降低为25M,而在传送10M数据时,时钟会降低到2.5M,这样就实现了10M和100M的兼容。

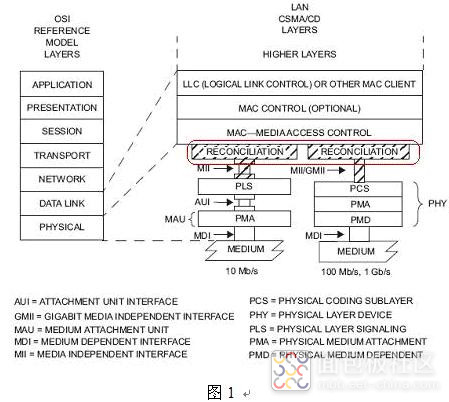

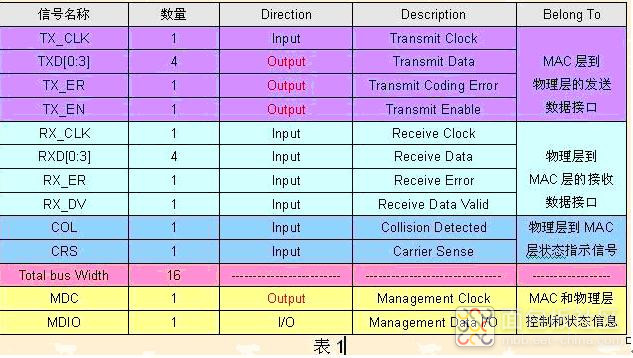

MII接口主要包括四个部分。一是从MAC层到物理层的发送数据接口,二是从物理层到MAC层的接收数据接口,三是从物理层到MAC层的状态指示信号,四是MAC层和物理层之间传送控制和状态信息的MDIO接口。

MII接口的MAC模式定义:

MII接口PHY模式定义:

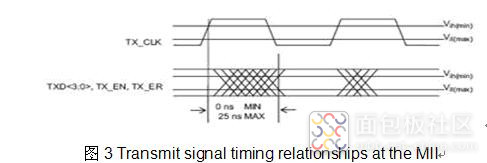

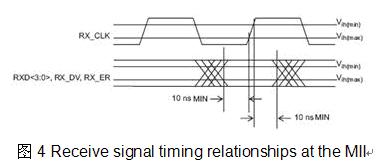

在MII接口中,TX通道参考时钟是TX_CLK,RX通道参考时钟是RX_CLK,802.3-2005定义了它们之间的关系。

由图3可知,即The clock to output delay shall be a min of 0 ns and a max of 25 nsSpec只对TX通道上MAC这一侧的发送特性作了定义,而对TX通道PHY那一侧的接收特性并没有定义。IC Vendor可在TX通道那一侧的PHY的接收特性作适当调整,只要最终的时序满足TX通道上MAC这一侧的发送特性就可以。

由图4可知,The input setup time shall be a minimum of 10 ns and the input hold time shall be a minimum of 10 nsSpec只对RX通道上MAC这一侧的接收特性作了定义,而对RX通道PHY那一侧的发送特性并没有定义。IC Vendor可在RX通道那一侧的PHY的发送特性作适当调整,只要最终的时序满足RX通道上MAC这一侧的接收特性就可以。

<1>:TX_CLK (transmit clock),TX_CLK (Transmit Clock)是一个连续的时钟信号(即系统启动,该信号就一直存在),它是TX_EN, TXD, and TX_ER(信号方向为从RS到PHY)的参考时钟,TX_CLK由PHY驱动TX_CLK的时钟频率是数据传输速率的25%,偏差+-100ppm。例如,100Mb/s模式下,TX_CLK时钟频率为25MHz,占空比在35%至65%之间。

<2>:对于同样的RX_CLK,它与TX_CLK具有相同的要求,所不同的是它是RX_DV, RXD, and RX_ER(信号方向是从PHY到RS)的参考时钟。RX_CLK同样是由PHY驱动,PHY可能从接收到的数据中提取时钟RX_CLK,也有可能从一个名义上的参考时钟(e.g., the TX_CLK reference)来驱动RX_CLK

<3>:TXD (transmit data),TXD由RS驱动,同步于TX_CLK,在TX_CLK的时钟周期内,并且TX_EN有效,TXD上的数据被PHY接收,否则TXD的数据对PHY没有任何影响。

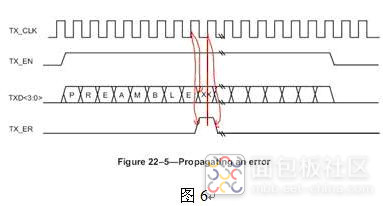

<4>:TX_ER (transmit coding error),TX_ER同步于TX_CLK,在数据传输过程中,如果TX_ER有效超过一个时钟周期,并且此时TX_ENTX_ER有效并不影响工作在10Mb/s的PHY或者TX_EN无效时的数据传输。在MII接口的连线中,如果TX_ER信号线没有用到,必须将它下拉接地。

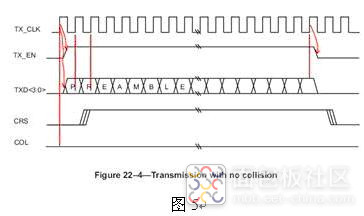

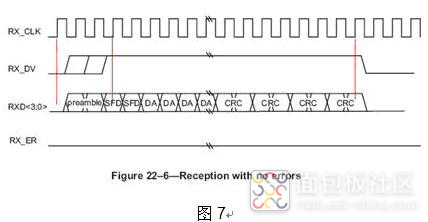

<5>:RX_DV (Receive Data Valid),RXD_DV同步于RX_CLK,被PHY驱动,它的作用如同于发送通道中的TX_EN,不同的是在时序上稍有一点差别:为了让数据能够成功被RS接收,要求RXD_DV有效的时间必须覆盖整个FRAME的过程,即starting no later than the Start Frame Delimiter (SFD) and excluding any End-of-Frame delimiter,如下图7。

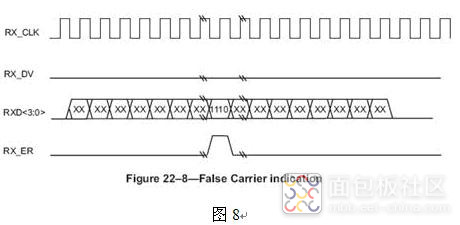

<6>:RXD (receive data),RXD由RS驱动,同步于RX_CLK,在RX_CLK的时钟周期内,并且RX_DV有效,RXD上的数据被RS接收,否则RXD的数据对RS没有任何影响。While RX_DV is de-asserted, the PHY may provide a False Carrier indication by asserting the RX_ER signal while driving the value <1110> onto RXD<3:0>。

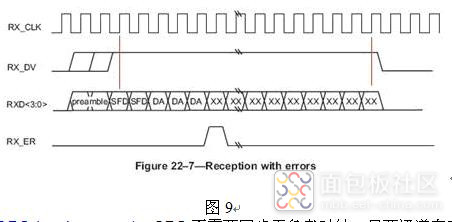

<7>:RX_ER (receive error),RX_ER同步于RX_CLK,其在RX通道中的作用类似于TX_ER对于TX通道数据传输的影响。

<8>:CRS (carrier sense),CRS不需要同步于参考时钟,只要通道存在发送或者接收过程,CRS就需要有效。The behavior of the CRS signal is unspecified when the duplex mode bit 0.8 in the control register is set to a logic one(自动协商禁止,人工设为全双工模式), or when the Auto-Negotiation process selects a full duplex mode of operation,即半双工模式信号有效,全双工模式信号无效。

<9>:COL (collision detected),COL不需要同步于参考时钟。The behavior of the COL signal is unspecified when the duplex mode bit 0.8 in the control register is set to a logic one(自动协商禁止,人工设为全双工模式), or when the Auto-Negotiation process selects a full duplex mode of operation。即半双工模式信号有效,全双工模式信号无效。

MDIO接口包括两根信号线:MDC和MDIO,通过它MAC层芯片(或其它控制芯片)可以访问物理层芯片的寄存器(前面100M物理层芯片中介绍的寄存器组,但不仅限于100M物理层芯片,10M物理层芯片也可以拥有这些寄存器),并通过这些寄存器来对物理层芯片进行控制和管理。MDIO管理接口如下:

MDC:管理接口的时钟,它是一个非周期信号,信号的最小周期(实际是正电平时间和负电平时间之和)为400ns,最小正电平时间和负电平时间为160ns,最大的正负电平时间无限制。它与TX_CLK和RX_CLK无任何关系。

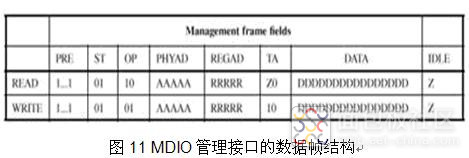

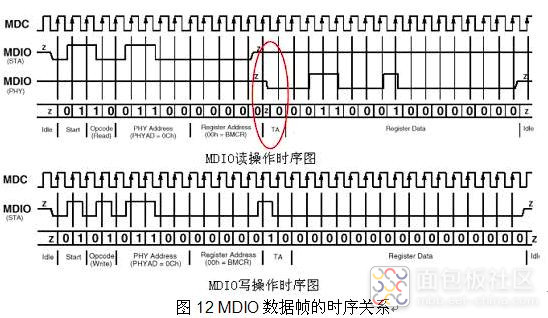

MDIO是一根双向的数据线。用来传送MAC层的控制信息和物理层的状态信息。MDIO数据与MDC时钟同步,在MDC上升沿有效。MDIO管理接口的数据帧结构如:

PRE:帧前缀域,为32个连续“1”比特,这帧前缀域不是必要的,某些物理层芯片的MDIO操作就没有这个域。

OP:帧操作码,比特“10”表示此帧为一读操作帧,比特“01”表示此帧为一写操作帧。

PHYAD:物理层芯片的地址,5个比特,每个芯片都把自己的地址与这5个比特进行比较,若匹配则响应后面的操作,若不匹配,则忽略掉后面的操作。

REGAD:用来选择物理层芯片的32个寄存器中的某个寄存器的地址。

TA:状态转换域,若为读操作,则第一比特时MDIO为高阻态,第二比特时由物理层芯片使MDIO置“0”。若为写操作,则MDIO仍由MAC层芯片控制,其连续输出“10”两个比特。

DATA:帧的寄存器的数据域,16比特,若为读操作,则为物理层送到MAC层的数据,若为写操作,则为MAC层送到物理层的数据。

IDLE:帧结束后的空闲状态,此时MDIO无源驱动,处高阻状态,但一般用上拉电阻使其处在高电平,即MDIO引脚需要上拉电阻。

MDIO数据帧的时序关系如下:

MII接口也有一些不足之处,主要是其接口信号线很多,发送和接收和指示接口有14根数据线(不包括MDIO接口的信号线,因为其被所有MII接口所共享),当交换芯片的端口数据较多时,会造成芯片的管脚数目很多的问题,这给芯片的设计和单板的设计都带来了一定的问题。为了解决这些问题,人们设计了两种新的MII接口,它们是RMII接口(Reduced MII接口)和SMII接口(StreamMII接口)。

这两种接口都减少了MII接口的数据线,不过它们一般只用在以太网交换机的交换MAC芯片和多口物理层芯片中,而很少用于单口的MAC层芯片和物理层芯片中。RMII接 口和SMII接口都可以用于10M以太网和100M以太网,但不可能用于1000M以太网,因为此时时钟频率太高,不可能实现。

下面这张图是从DM368的datasheet上的:

/5

/5

文章评论(0条评论)

登录后参与讨论