概述:由于近期要使用以太网PHY芯片,于是在网上查找各种资料,学习这部分的知识,这篇文章是对当前的学习做一个汇总。海翎光电的小编目前也是在学习PHY,所以难免会有错误不足,有什么需要更正补充的,欢迎大家一起讨论交流。

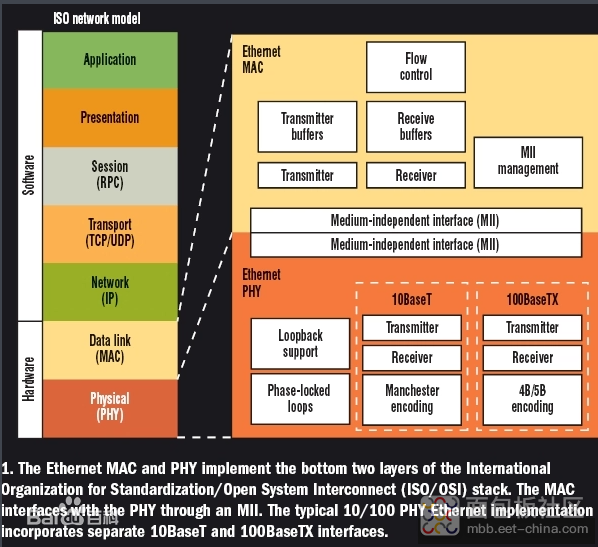

什么是PHY? PHY(英语:Physical),中文可称之为

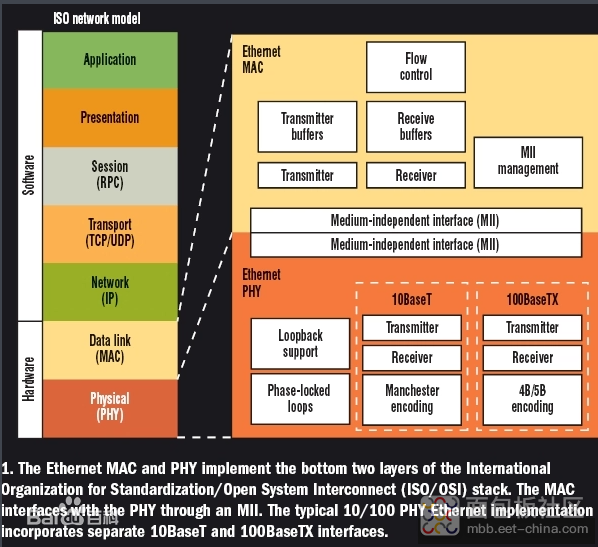

端口物理层,是一个对OSI模型物理层的共同简称。而以太网是一个操作OSI模型物理层的设备。一个以太网PHY是一个芯片,可以发送和接收以太网的数据帧(frame)。 也就是说,PHY是网络结构中的最底层,物理层。PHY芯片是实现物理层这一层功能的芯片。网络设备之间就是通过PHY芯片相互连接的(介质是网线或者光纤)。

PHY芯片的硬件连接简单介绍 拿CPU与PHY的连接举例,网络上层几层框架,基本都可以封装或集成到CPU内部,但一般PHY芯片可能会单独出来,虽然目前一些集成度高的网络设备,或者CPU也可以做到将PHY集成到一个芯片。但一般来说,PHY的功能是单独做到一个PHY芯片内部的,集成了PHY的网络设备芯片(CPU、交换机芯片等等)一般也有接口连接单独的PHY。这是因为

PHY的主要功能就是将数字信号转成模拟信号,然后在网线或者光纤传输。因为模拟信号和数字信号的不同,加上不同设备之间的传输环境复杂,因此,

大部分的PHY都是单独做到一个芯片内的。 因此,在一般的网络设备电路设计中,需要为PHY芯片设计电路。PHY的芯片厂家为了满足大部分的应用场景,会在PHY上面提供很多接口协议,以供设计人员使用。比如,一颗PHY可能会支持网线传输,又或者支持光纤传输,然后在连接数据链路层这边,会提供很多的MII接口以供选择。 由于一个PHY芯片的功能可能会比较多,因此,在PHY芯片的应用中,有一点很重要的就是要选择合适的接口来满足自己的应用。

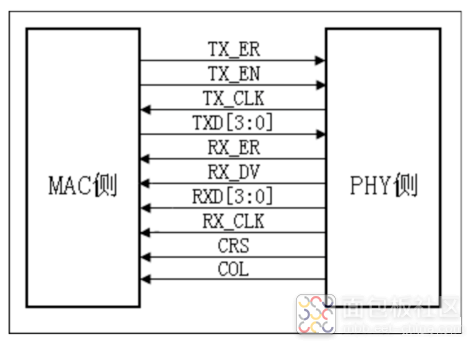

PHY芯片的接口介绍 MII接口 MII是连接PHY和MAC的总线。有一系列的MII总线协议来满足不同的应用场景,如MII, RMII, SMII, GMII, RGMII, SGMII, XGMII等等。

既然有这么多的协议,为什么不使用同一种固定的总线协议呢,比如IIC或者SPI这种,这么多的总线协议,不是加大了应用设计的难度? 这是因为,网络传输是一种高速的通信,而且是一直在发展的,导致以前的一些协议已经不能满足现在的传输要求,比如从10M/100M到现在的1G/10G等等,不同的MII接口就是为了满足不同的应用。而且,由于芯片设计的发展,也可以对一些占用资源的总线做优化改动,

例如以前的并口通信,会占用很多的引脚资源,但现在由于高频通信的发展,使用串行总线也可以达到高速通信的目的,并且还节省引脚资源。 下面介绍一些常用的MII总线协议,以供参考。 注:MII命名是有一定规律的,比如G代表1000兆,XG代表10G(万兆),R代表减少引脚,S代表串行通信,例如,RGMII就是减少引脚的1000兆MII总线,SGMII就是串行通信的1000兆MII总线。

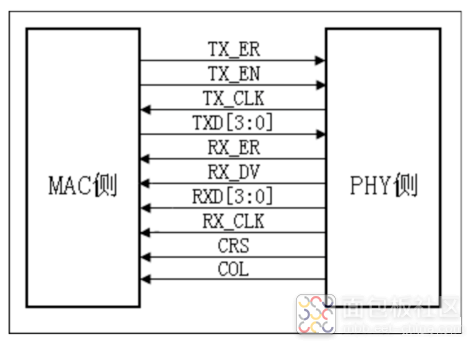

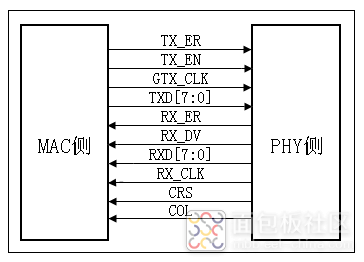

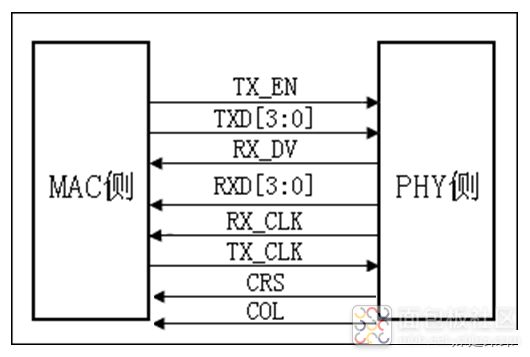

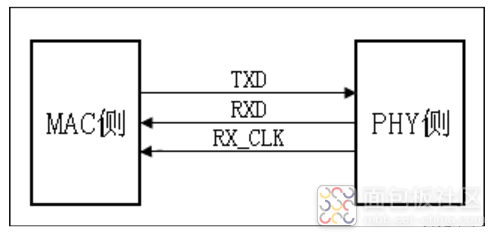

1.MII接口模式是支持10/100兆。

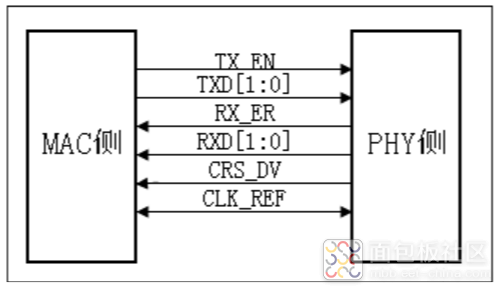

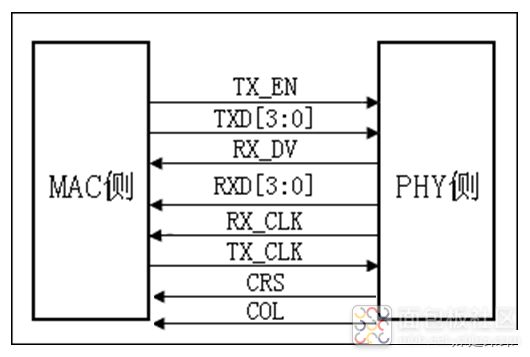

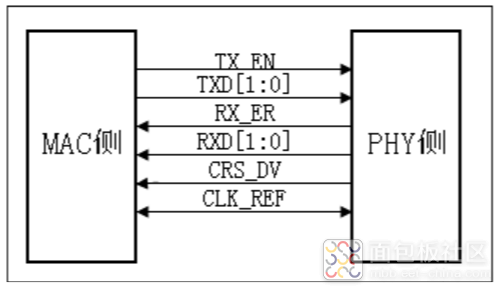

2.RMII:MAC和PHY芯片之间的接线图,数据线相比MII减半,时钟为50MHZ,还是需要注意TX_CLK是由phy芯片发出,如果是需要自适应10/100M。

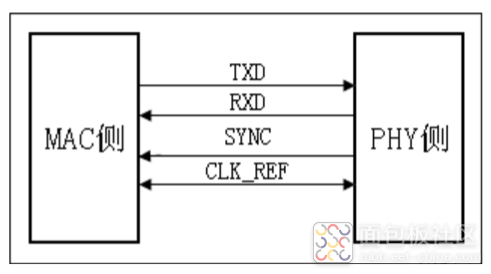

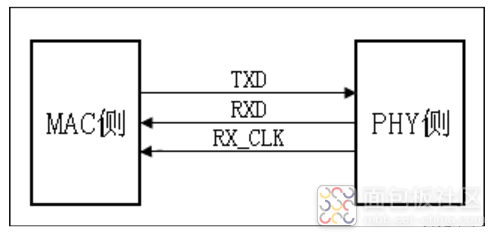

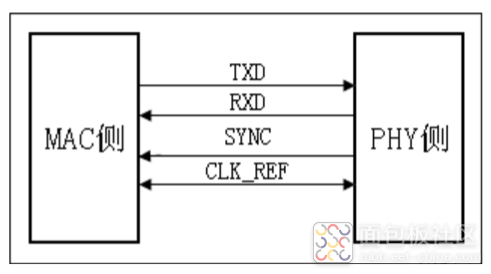

3.SMII:10/100M

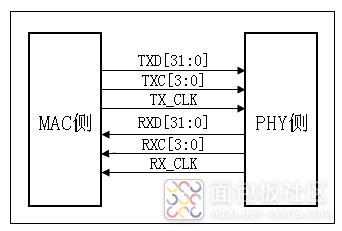

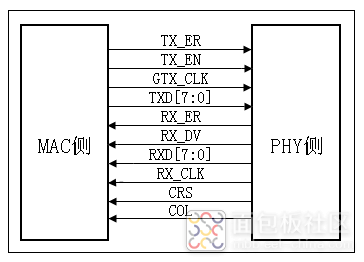

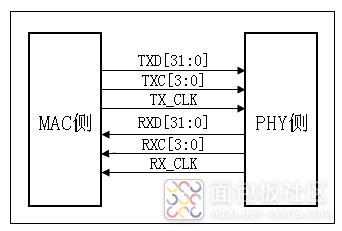

4. GMII:对应为千兆网;要实现1000Mb/s、100Mb/S、10Mb/S自适应必须加上TX_CLK(PHY输出)

5.RGMII:

6.SGMII:

7.XGMII:10G,万兆。

SMI(MDC/MDIO)接口 有很多PHY芯片有许多的接口和功能,需要根据自己的需求进行选择配置,配置的方法就是配置PHY内部的寄存器,而SMI接口就是PHY专门用于管理这些寄存器的一个标准协议。

SMI接口是一个串行接口,接口包括两根信号线:MDC和MDIO。 这个接口也是遵守IEEE802.3协议规范的,因此可以通过IEEE802.3协议了解SMI接口的具体细节要求。下面对SMI接口做一些简单介绍。

MDC: 管理接口的时钟,它是一个非周期信号,信号的最小周期(实际是正电平时间和负电平时间之和)为400ns,最小正电平时间和负电平时间为160ns,最大的正负电平时间无限制。

MDIO:这是一根双向的数据线。用来传送MAC层的控制信息和物理层的状态信息。MDIO数据与MDC时钟同步,在MDC上升沿有效。

目前SMI接口一共有两种协议,第22条款和第45条款,其中两个条款使用同样的硬件,在时序上是一致的。第22条款和45条款,就是对应IEEE802.3的22节和45节。现在一些简单的PHY内部的寄存器使用的是802.3的第22条款,只有32个寄存器,功能简单,比如一些千兆百兆PHY。而一些复杂的PHY使用的是802.3的第45条款,可以将寄存器扩展至65536个寄存器。

注:虽然对于PHY芯片的寄存器有相关标准的规定,但厂家有可能不按照标准设计,所以最好是查看对应的芯片手册了解寄存器的功能。

PHY的SMI接口可以由MAC侧或者MCU(单片机)控制,通过SMI接口可以实现PHY的配置以及各项参数的读取,以达到监控PHY的状态。当MCU无SMI接口时,可以使用GPIO模拟SMI接口。

光电接口 目前数据在网络中传输,主要的传输介质是铜缆或者光纤,在PHY芯片对应的就是电口或者光口。我们经常见到1000base-T、1000BASE-TX、1000BASE-FX这样的描述,对应的解释如下。

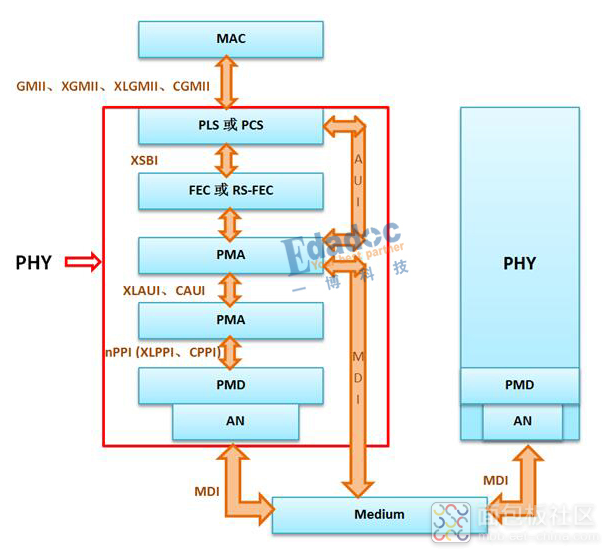

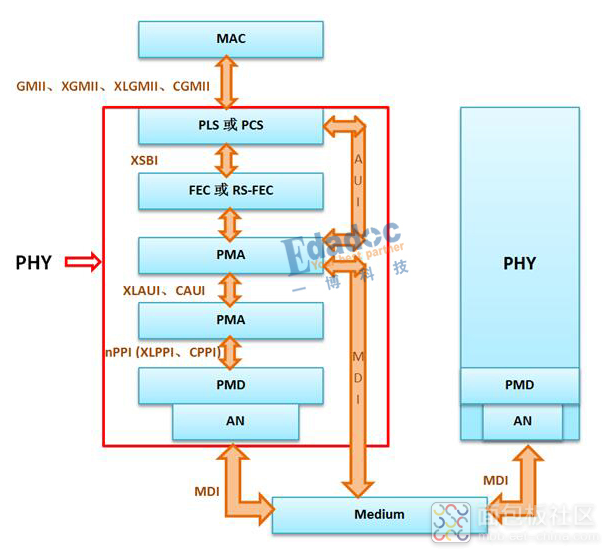

1000:表示传输速率;BASE: 表述基带;-T/TX:传输介质为铜介质的双绞线,其中1000BASE-T对应传输线为4对,全双工运行,时钟125MHZ。超五类网线。1000BASE-TX对应传输线也为4对,只是其中2对用来收,两对用来发。故运行时钟250HZ,对应线缆为6类网线。-FX:传输介质为光纤;光口,信号传输走的是光信号这是与上面不同的。 PHY芯片的内部结构 PHY它包含了多个功能模块,功能模块的多少会因需要的不同而有所增减。比如:只有10GBase-R、40GBase-R、100GBase-R的PCS需要FEC;

40GBase-R的PCS需要2个PMA、100GBase-R的PCS需要3个PMA;

只有≥1Gbps以上的背板应用场景才会用到AN。

PHY由多个模块组成,各个功能模块的作用如下:PLS:PhysicalSublayer Signaling,对MAC给的信息进行传递,只在1Mb/s、10Mb/s的应用场景才出现;

PCS:Physical Coding Sublayer,对MAC给的信息进行编码,应用于≥100 Mb/s的应用场景,比如完成8B/10B、64B/66B、256B/257B编码;

FEC:Forward Error Correction,前向纠错,与10GBase-R、40GBase-R的PCS 搭配;

RS-FEC:Reed-Solomon前向纠错,比单纯的FEC纠错能力更强,与100GBase-R的PCS 搭配,采用256B/257B编码;

PMA:Physical Medium Attachment,物理媒介适配层,PMA子层主要用于串行化和解串。PMA子层中集成了SERDES,发送和接收缓冲,时钟发生器及时钟恢复电路。

PMD:Physical Medium Dependent,物理介质相关子层,PMD子层位于整个网络的最底层,主要完成光纤连接、电/光转换等功能。PMD为电/光收发器,把输入的电压变化状态变为光波或光脉冲,以便能在光纤中传输。

AN: Auto-Negotiation Function,自动协商,使背板两侧的Device能够互换信息以发挥出彼此最大的优势;

其中主要的常用的模块是PCS、PMA、PMD。在各种PHY芯片内部基本都有这几个模块。

PHY的功能

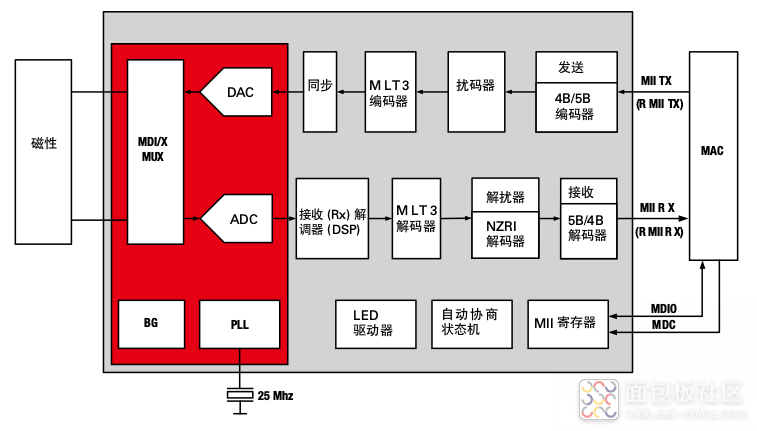

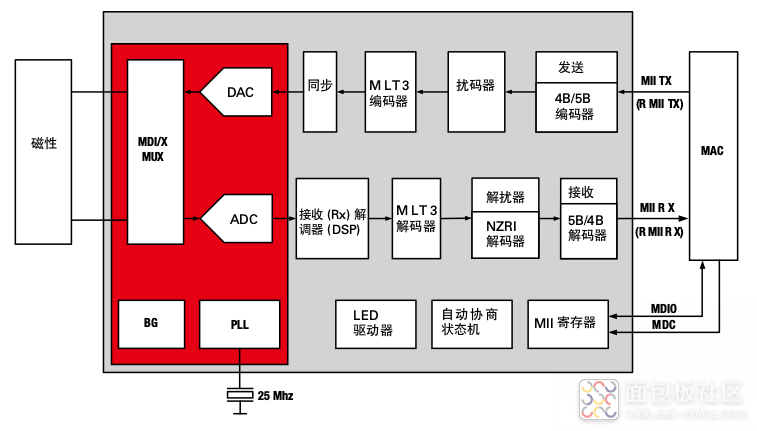

PHY的功能之一:与MAC通过MII接口进行数据传递,对发送的数据进行编码,对接收的数据进行解码 MAC器件通过MII接口来与PHY进行数据交换。PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据而不管什么地址,数据还是CRC),每4bit就增加1bit的检错码(PCS),然后把并行数据转化为串行流数据(PMA),再按照物理层的编码规则把数据编码(PMA),再变为模拟信号把数据送出去(PMD)。 当PHY接收数据时的流程反之。

PHY的功能之二: CSMA/CD的部分功能 PHY还有个重要的功能就是实现CSMA/CD的部分功能。它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。如果两块网卡碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。

参考资料:

Network 之二 Ethernet(以太网)中的 MAC、MII、PHY 详解_itexp-CSDN博客_mac

MII/GMII/RGMII知识学习。- 知乎

各种MII详解(MII,GMII,RGMII,RMII,SMII,SSMII,TBI,RTBI) - 百度文库

了解与MDIO/MDC接口相关的22号、45号条款_jason的专栏-CSDN博客_mdio接口协议

PHY——内部接口协议

MAC和PHY基本组成与工作原理简析_Clearfix_Xia-CSDN博客_phy芯片工作原理。

/5

/5

文章评论(0条评论)

登录后参与讨论